# AN INTELLIGENT MULTI-TERMINAL INTERFACE

by

## Roger Charles Samuel Peplow

Submitted in partial fullfillment of the requirements for the degree of Master of Science in Engineering in the Department of Electronic Engineering at the University of Natal, Durban.

Durban

November 1987

## Preface

The work described in this thesis was carried out in the Department of Electronic Engineering, University of Natal, Durban, from June 1978 to January 1979, under the supervision of Professor H.L. Nattrass.

This material represents the author's original work except where specific acknowledgement is made, and has not been submitted in part, or in whole, to any other University for degree purposes.

## Acknowledgements

My thanks go to my supervisor Professor Lee Nattrass, not only for his guidance during the course of the project, but also for allowing me the time to do the work when the departmental lecturing load has been so high. I also thank him for his patience while waiting for me to complete the thesis which has been awaiting final proof reading for far too long.

Thanks also go to my colleagues Dave Levy and Nils Otte who suffered my ministrations to their computer systems while I was debugging the RMUX interface software. Thanks also for their show of faith in using so many of the final units.

Special thanks must also go to my wife Eleanor for her encouragement, criticism and support and also for her great assistance in the typing of the document.

I would also like to thank Philip Facoline for producing many of the final drawings on his CAD system, Sheila Wright for doing much of the typing, and Tandy Wright for getting much of the final document through the printer.

The document was printed on the KIDRON type setting system in the Department of Electronic Engineering after originally being captured on the HP1000 for the TYPEC text and document processor. The drawings were produced on both a GERBER IDS80 system and a CEADS CAD system and were all plotted on an HP7586 plotter.

### Abstract

The document describes the development of a micro-processor based terminal multiplexer to connect four terminals to a standard Hewlett Packard series 1000 mini-computer. The project was required to fulfill the dual roll of both increasing the number of terminals that the HP1000 could support and of reducing the peripheral load on the host CPU.

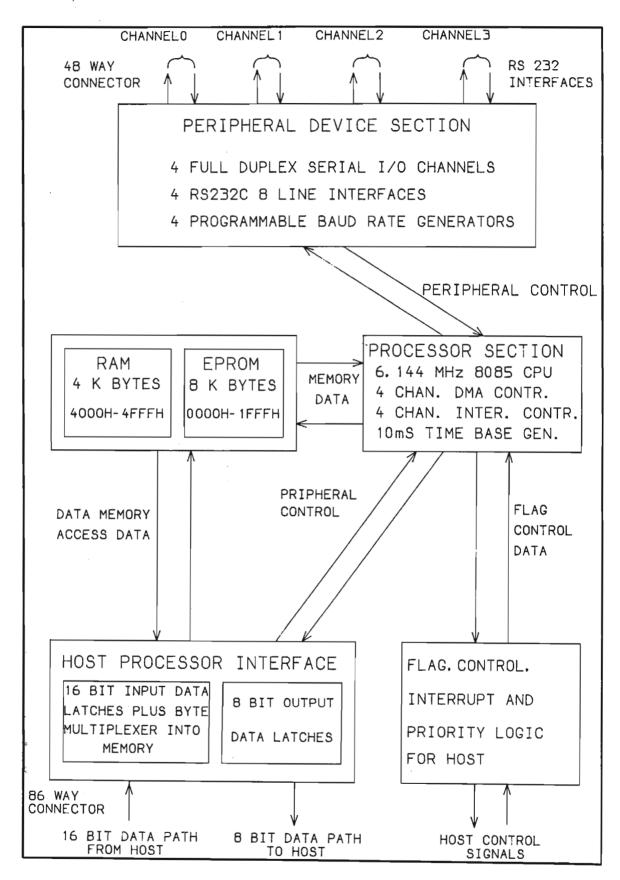

The final product occupied a standard 200mm square HP size interface card and used an 8085 micro-processor and several 8085 family peripheral chips to provide four full duplex serial channels and a high speed data link with the host.

A multi-tasking executive was written to control the multiplexer software which was finally implemented as 15 independent tasks occupying 8 kilo-bytes of eprom. The software was written to perform all terminal interaction and editing in order to reduce the host CPU involvement to a single interrupt per record.

The resultant interface proved capable of handling an aggregate throughput in excess of 4000 characters per second which was sufficient to cope with all four terminals running at 9600 bits per second, even when all four were transferring in burst mode. The interface also proved to be between five and eighteen times less demanding on the host than the two standard Hewlett Packard interfaces then available. When compared to the low cost HP12531 interface, the multiplexer increased the 9600b/s terminal handling capability of the host from 3 terminals to 52.

# Contents

# CHAPTER

| 1. | In | troduct | tion                                    |      |

|----|----|---------|-----------------------------------------|------|

|    |    | 1.1     | Introduction                            | 1    |

|    |    | 1.2     | A Brief look at Peripheral Control      | 2    |

|    | 2. | An I/   | O Expander for Terminal Interfaces      | 5    |

|    |    | 2.1     | Introduction                            | 5    |

|    |    | 2.2     | The HP I/O System                       | 5    |

|    |    | 2.3     | The HP12531 Teletype Interface          | 7    |

|    |    | 2.4     | The Expander Mainframe                  | 8    |

|    |    | 2.5     | The Terminal Interface                  | 10   |

|    |    | 2.6     | Conclusion                              | 11   |

|    | 3. | An I    | ntelligent Drum Printer Controller      | 12   |

|    |    | 3.1     | Introduction                            | 12   |

|    |    | 3.2     | Printing on a Drum Printer              | 13   |

|    |    | 3.3     | The Controller Hardware                 | 14   |

|    |    |         | The Timing Logic Card                   | 14   |

|    |    |         | The Processor Module                    | 15   |

|    |    | 3.4     | The Printer Controller Software         | 16   |

|    |    |         | The Data Producer                       | 16   |

|    |    |         | The Data Consumer                       | 16   |

|    |    |         | Interrupt Tasks                         | 17   |

|    |    | 3.5     | The Message Transfer Protocol           | 18   |

|    |    | 3.6     | Conclusion                              | 18   |

|    | 4. | The     | RMUX Terminal Multiplexer— Design Aims  | 20   |

|    |    | 4.1     | Introduction                            | 20   |

|    |    | 4.2     | A survey of Standard Interface Features | 20   |

|    |    | 4.3     | Objectives for an Ideal Interface       | 22   |

|    |    | 4.4     | The Host—Slave Interface Philosophy     | 24   |

|    |    | 4.5     | The Slave Micro-processor Requirements  | 27   |

|    |    |         | Peripheral Choices                      | 27   |

|    |    |         | Memory Choice                           | 2    |

|    |    |         | Memory Address Allocation               | 28   |

|    |    | 4.6     | Final Hardware Design                   | . 28 |

|    |    | 4.7     | Read and Write Signal Decoding          | 29   |

| 5. | The N      | Multi-plexer Interface Operating Software         | 33 |

|----|------------|---------------------------------------------------|----|

|    | 5.1        | Introduction                                      | 33 |

|    | 5.2        | The A8085 Cross Assembler                         | 33 |

|    | 5.3        | The Requirements of a Multi-Tasking Executive     | 35 |

|    | 5.4        | Semaphores for Task Control                       | 36 |

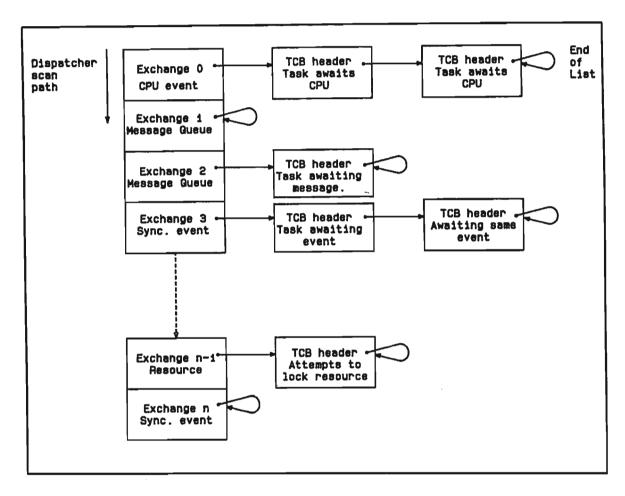

|    | 5.5        | The MTX Multi Tasking Executive Kernal            | 37 |

|    |            | The Task Control Block                            | 37 |

|    |            | The Exchange                                      | 38 |

|    |            | The Use of Exchanges                              | 39 |

|    |            | Event Calls                                       | 39 |

|    |            | Resource Calls                                    | 39 |

|    | <b>5.6</b> | Memory Management Facilities                      | 40 |

|    | 5.7        | Task Control Facilities                           | 42 |

|    | 5.8        | MTX—A Summary                                     | 42 |

|    |            | Interrupt Handling                                | 42 |

|    |            | Coding the System                                 | 43 |

|    | 5.9        | Time List Handling                                | 43 |

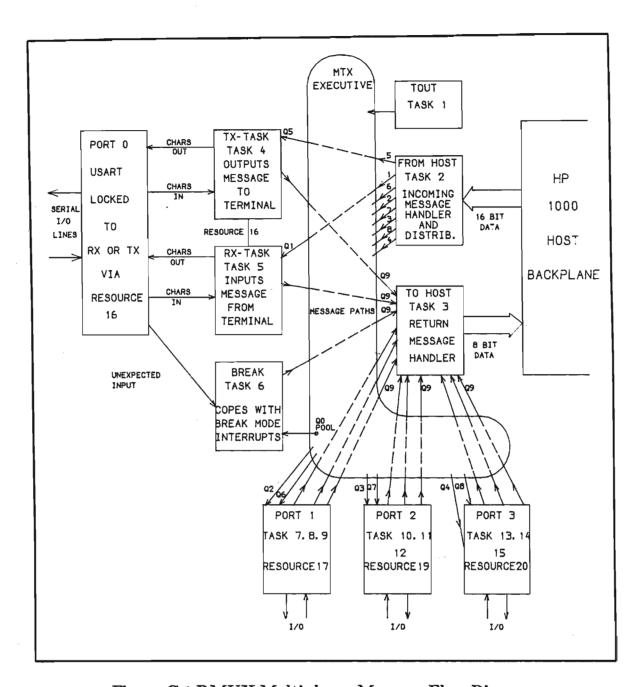

|    | 5.10       | Application Task Structure                        | 44 |

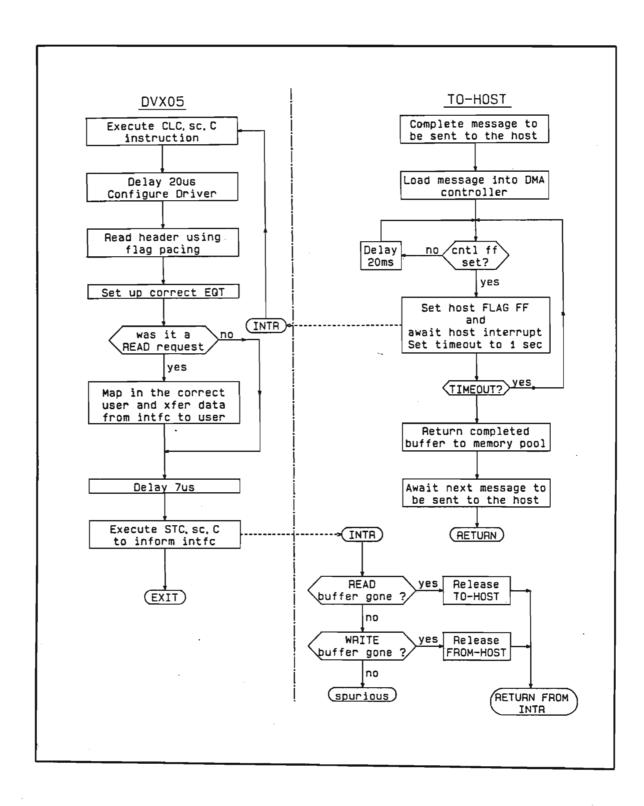

|    | 5.11       | Host Interaction Tasks                            | 45 |

|    |            | TO_HOST                                           | 45 |

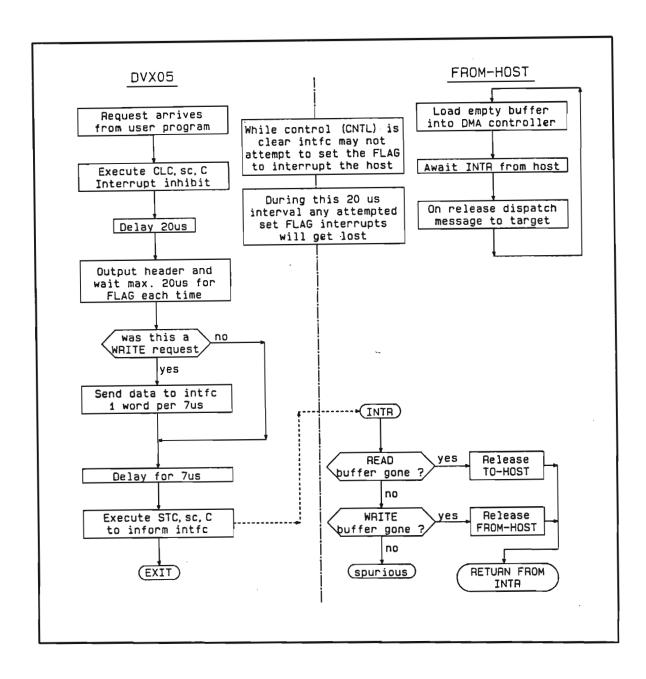

|    |            | FROM_HOST                                         | 46 |

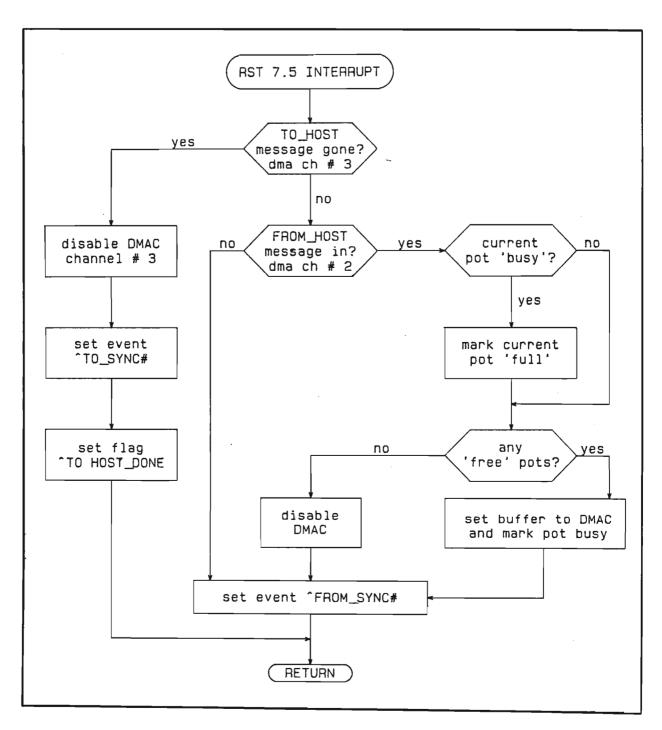

|    |            | STCINT                                            | 49 |

|    | 5.12       | Port Handler Tasks — An Overall View              | 50 |

|    | 5.13       | TX_TASK, the Port Transmit Handler                | 52 |

|    | 5.14       | RX_TASK, the Port Receive Handler                 | 54 |

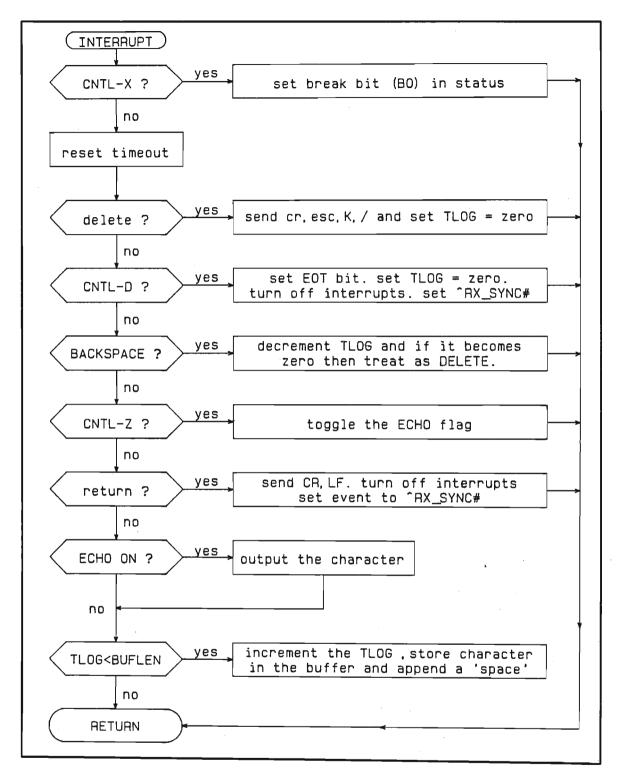

|    |            | Receive Interrupt Handler                         | 55 |

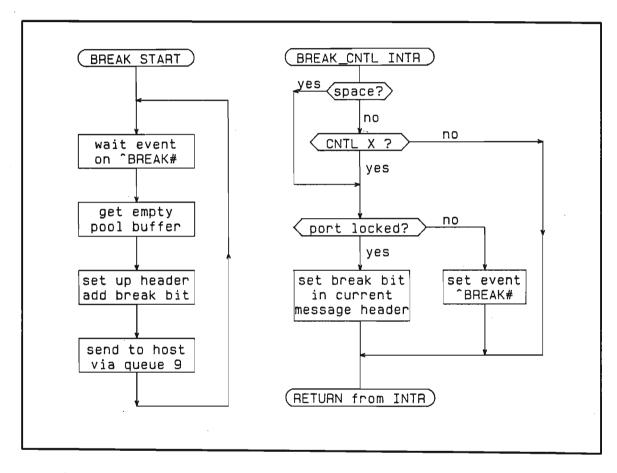

|    | 5.15       | BREAK_TASK, the Unsolicited Interrupt Handler     | 57 |

| 6. | The        | Host Software Driver Routine — DVX05              | 59 |

|    | 6.1        | Introduction to DVX05                             | 59 |

|    | 6.2        | The normal Interrupt Response Procedure           | 60 |

|    | 6.3        | Operating System feature changes — The Philosophy | 61 |

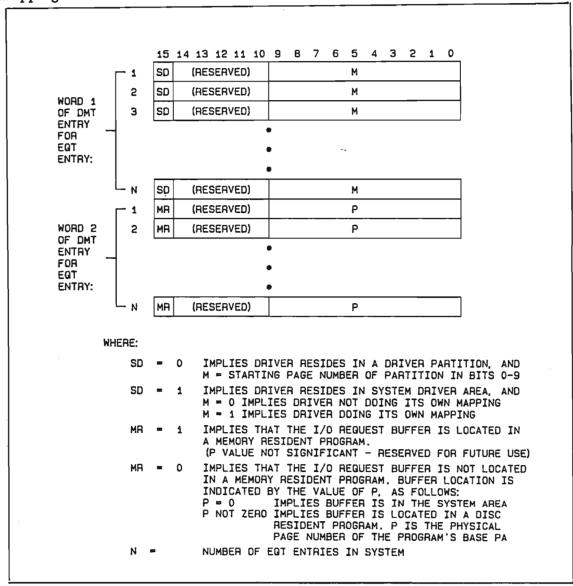

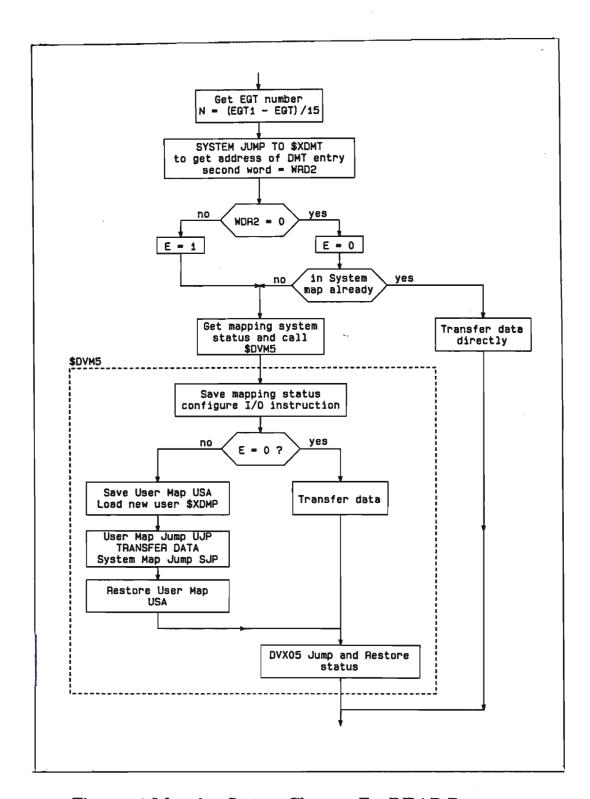

|    | 6.4        | Mapping System changes — \$DVM5                   | 63 |

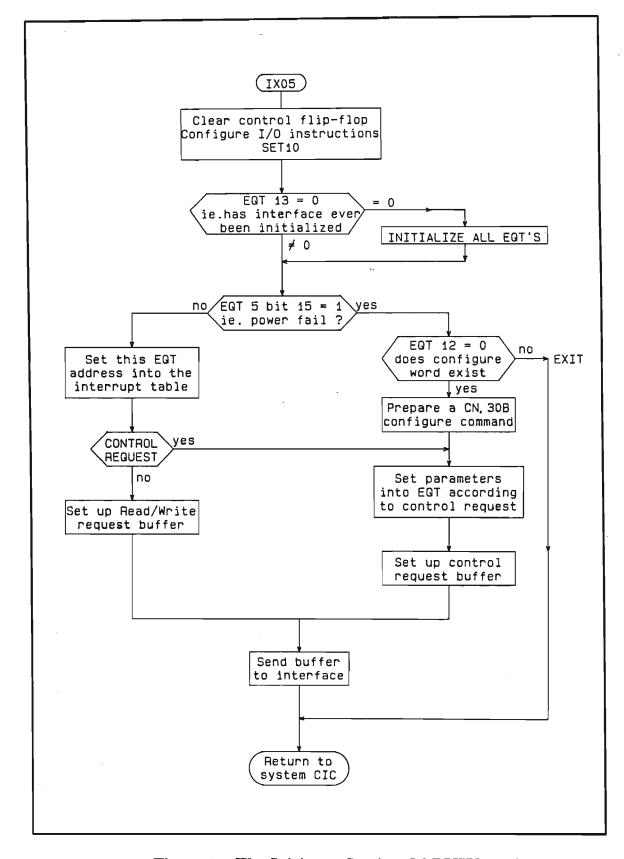

|    | 6.5        | The layout of the Main Driver — DVX05             | 65 |

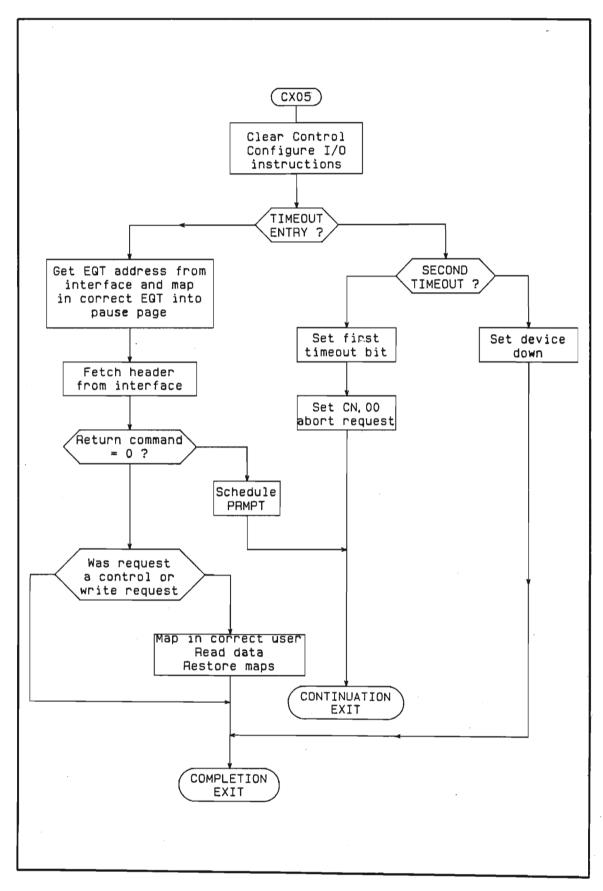

|    |            | The Initiation Section                            | 66 |

|    |            | Configuration of I/O Instructions                 | 67 |

|    |            | Cold Start Initialization                         | 67 |

|    |            | Power Fail Handling                               | 67 |

|    |            | Minimizing Map Changes                            | 67 |

|    |            | Request Processing                                | 68 |

|    |            | The Completion Section                            | 69 |

|    |            | Timeout Processing                                | 69 |

|                        |        | Normal Interrupt Processing                                 | 71        |

|------------------------|--------|-------------------------------------------------------------|-----------|

|                        | 6.6    | Timing considerations                                       | 71        |

|                        |        | Cold Start Delay                                            | 71        |

|                        |        | Driver Exit Delay                                           | <b>72</b> |

|                        |        | CLC to driver-output delay                                  | 72        |

| 7.                     | Perfo  | rmance Measurements and Results                             | 74        |

|                        | 7.1    | Introduction                                                | 74        |

|                        | 7.2    | Interface Timing Measurements                               | 74        |

|                        | 7.3    | Host Throughput Measurements                                | 76        |

| 8.                     | Concl  | usion                                                       | 80        |

| ΑF                     | PENI   | DICES                                                       | 82        |

| Ap                     | pendix | A. A terminal I/O Extender for the HP1000                   | 82        |

| $\mathbf{A}\mathbf{p}$ | pendix | B. Honeywell Line Printer Controller – Hardware Description | 92        |

| Ap                     | pendix | C. Honeywell Line Printer Controller – Software Description | 99        |

| Аp                     | pendix | D. Honeywell Line Printer Controller – Host Software        | 105       |

| Аp                     | pendix | E. RMUX Hardware Description                                | 108       |

| Аp                     | pendix | F. MTX Software Description and User Manual                 | 126       |

| Ap                     | pendix | G. RMUX System Software                                     | 143       |

| Ap                     | pendix | H. The RTE IVB Input/Output System                          | 162       |

| Ap                     | pendix | I. The host driver to control the RMUX Interface            | 168       |

| Ap                     | pendix | J. The 8085 Assembler-A8085                                 | 183       |

| Ap                     | pendix | K. The RMUX Users Manual                                    | 196       |

## **FIGURES**

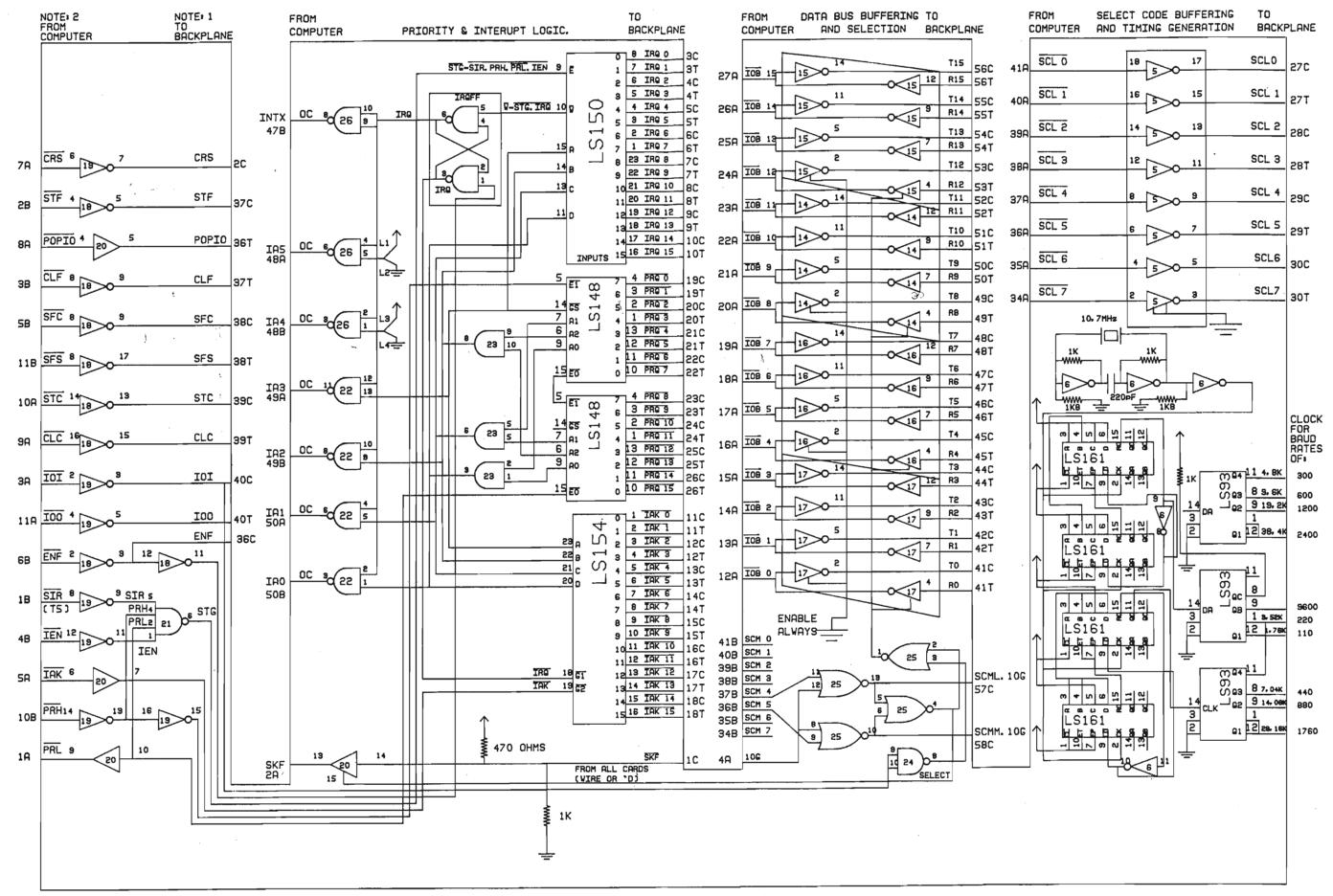

| 2.1        | Standard HP I/O interface control logic    | 0   |

|------------|--------------------------------------------|-----|

| 2.2        | Master control card schematic              | 9   |

| 4.1        | Host—Slave Interaction Policy              | 25  |

| 4.2        | The Ideal Slave System Interface           | 26  |

| 4.3        | Recommended 8085—8237 Connection Scheme    | 30  |

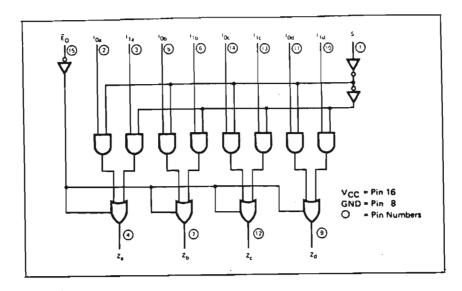

| 4.4        | 74LS257 Quad Multiplexer construction      | 31  |

| 4.5        | Read and Write Signal Routing              | 31  |

| 5.1        | TOHOST Task Layout                         | 46  |

| 5.2        | FROM_HOST Task Layout                      | 47  |

| 5.3        | STCINT—The Interrupt Handler               | 49  |

| 5.4        | Partial Listing of &RXDRV                  | 51  |

| 5.5        | An Overview of TXTASK, the Output Handler  | 53  |

| 5.6        | Long Mode Block Transfer Sequence          | 56  |

| 6.1        | The Driver Mapping Table (DMT) format.     | 63  |

| 6.2        | Mapping System Changes for Read Requests   | 64  |

| 6.3        | The Initiation section of DVX05            | 66  |

| 6.4        | The Completion section of DVX05            | 70  |

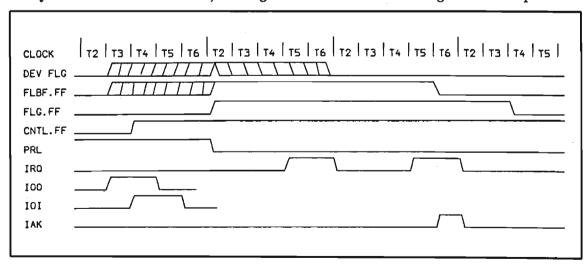

| <b>A.1</b> | Timing of flag, Control and Interupt Logic | 82  |

| <b>A.2</b> | Standard HP I/O Interface Logic            | 83  |

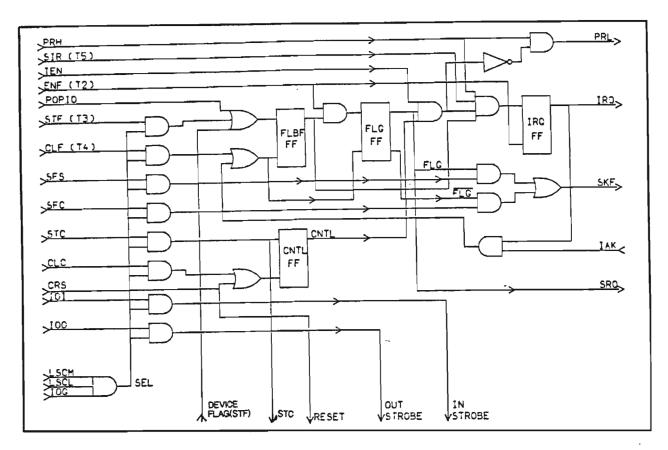

| <b>A.3</b> | Priority and Interrupt Logic in the I/O    | 84  |

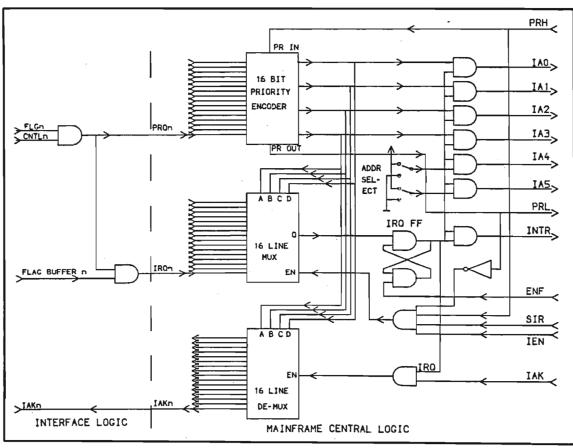

| <b>A.4</b> | Master Control Board Logic                 | 86  |

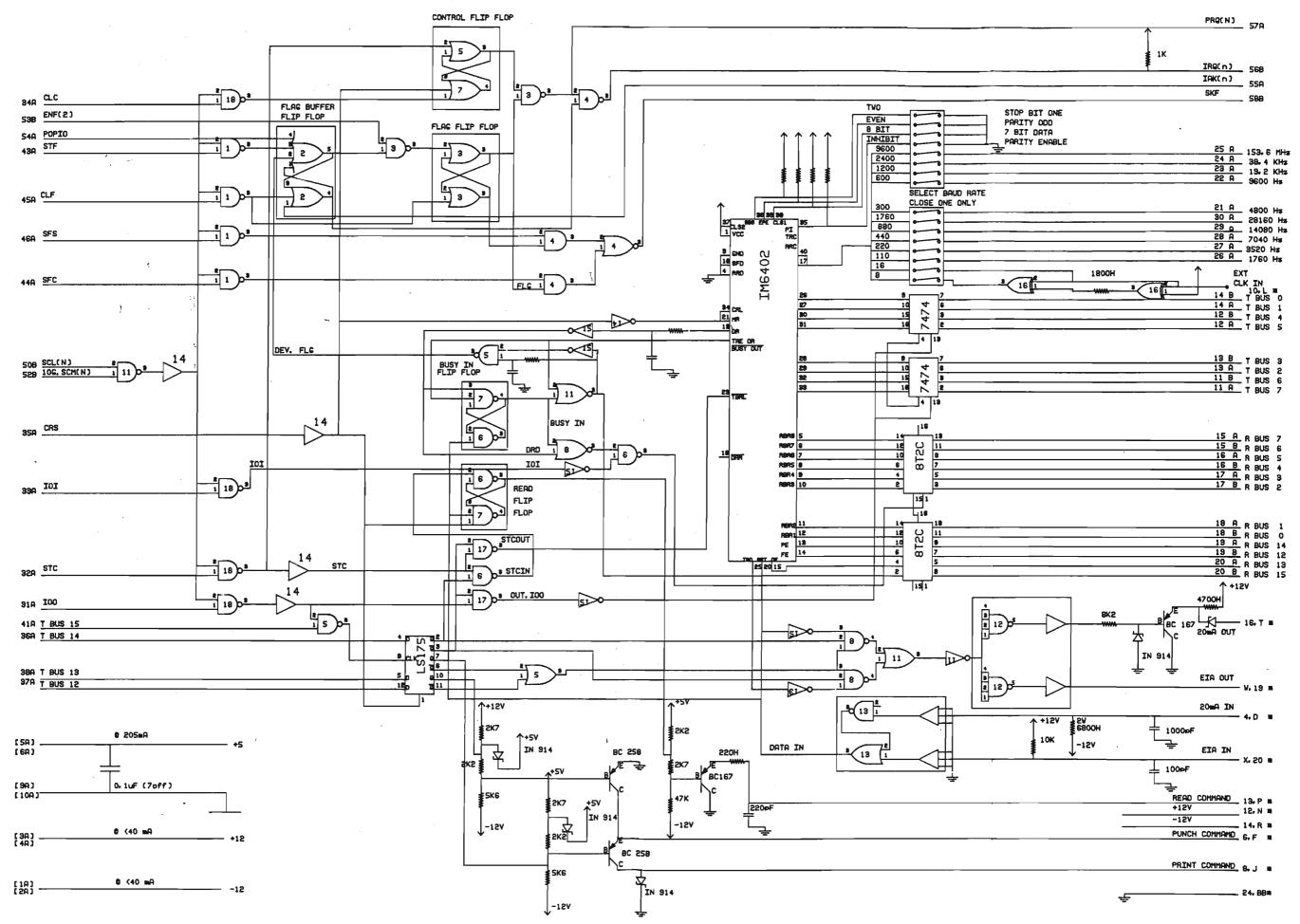

| <b>A.4</b> | Terminal Interface Logic                   | 88  |

| A.6        | Terminal Interface board Layout            | 91  |

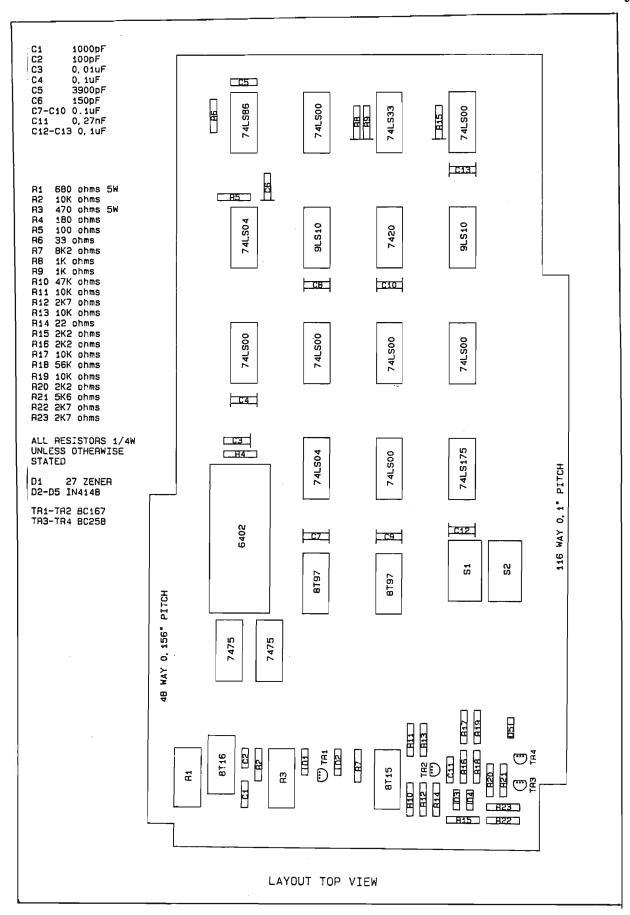

| B.1        | Timing Diagram for the Timing Generator    | 93  |

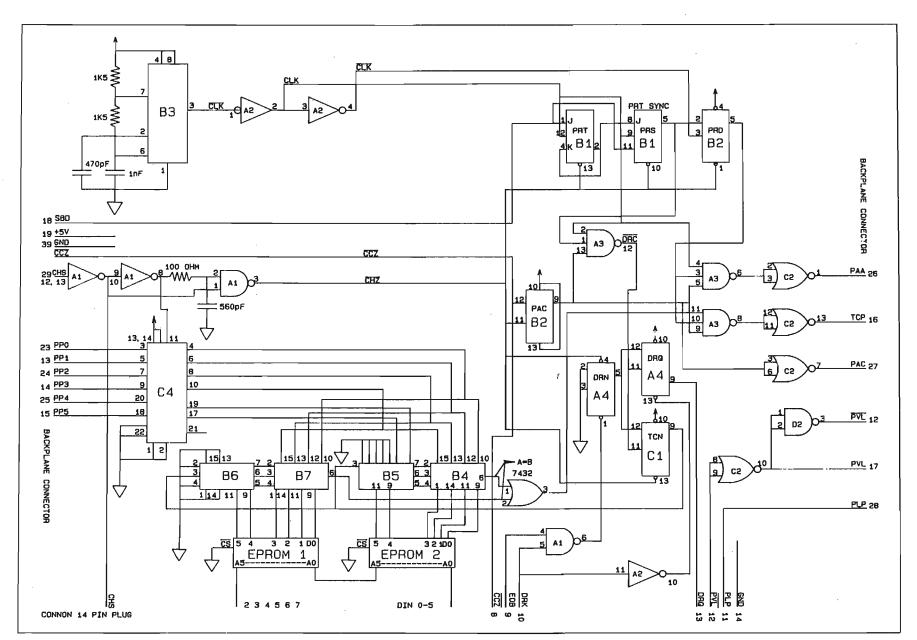

| <b>B.2</b> | Timing Generator Module Schematic          | 94  |

| B.3        | Printer Controller Module Schematic        | 97  |

| C.1        | Printer control programme. Module Layout   | 99  |

| C.2        | Print Request Record Format                | 102 |

| D.1        | The Hexadecimal to ASCII coding scheme     | 106 |

| E.1        | RMUX Hardware Block Diagram                | 109 |

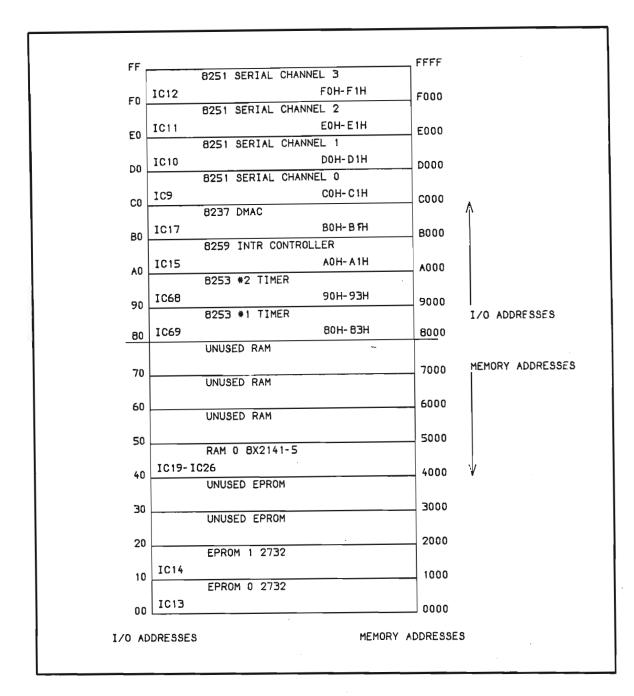

| E.2        | RMUX Address Map                           | 113 |

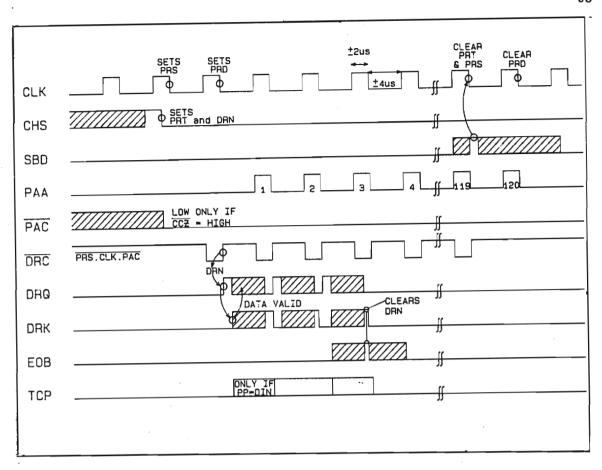

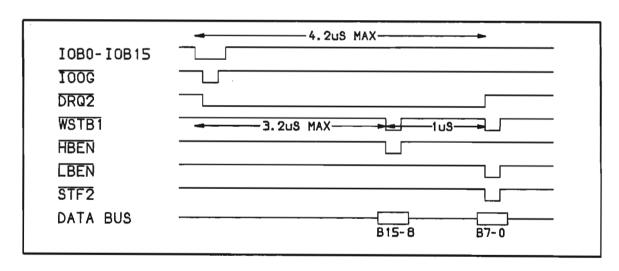

| E.3        | Backplane Data Input Timing                | 116 |

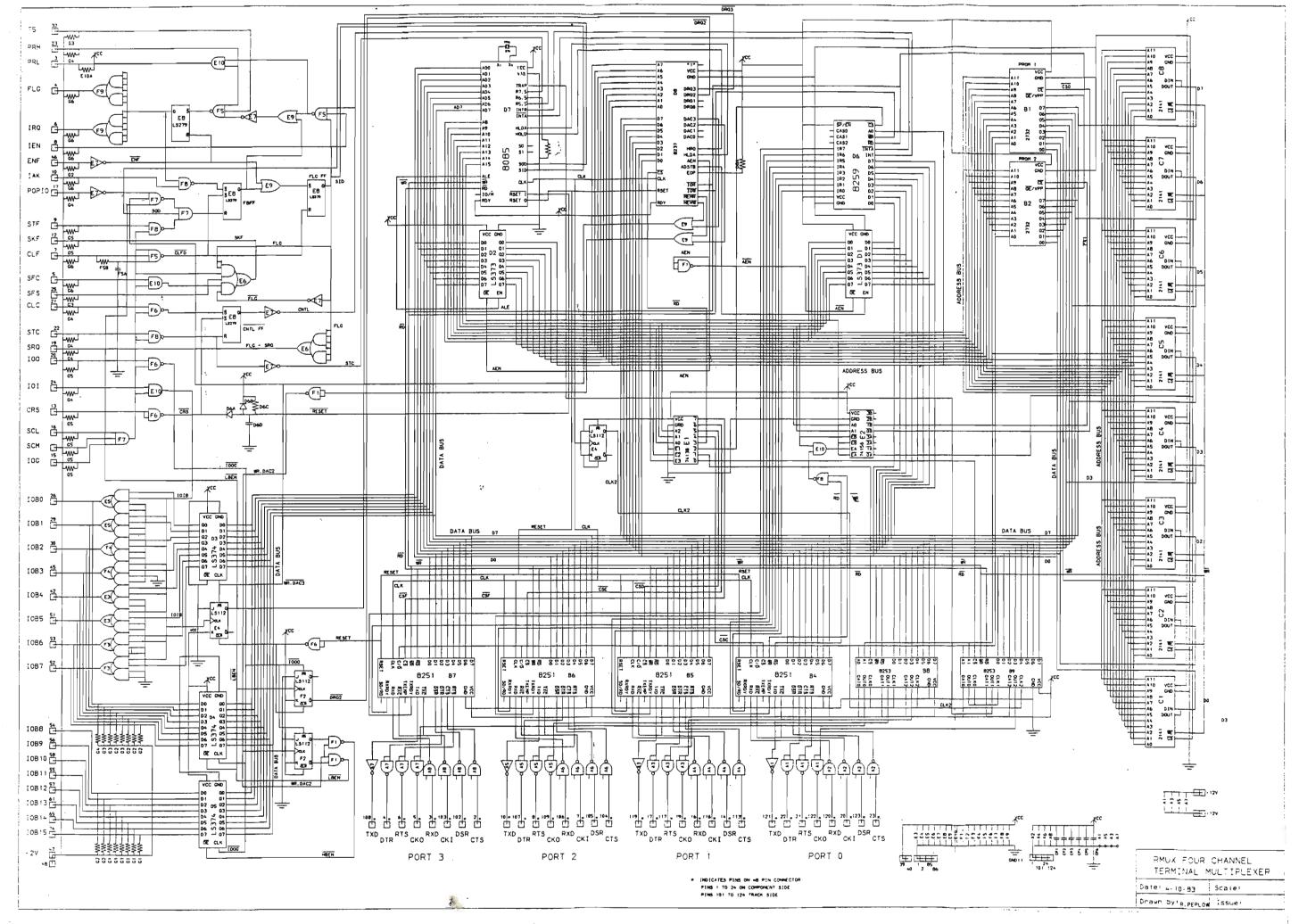

| E.4        | RMUX Multiplexer Schematic                 | 123 |

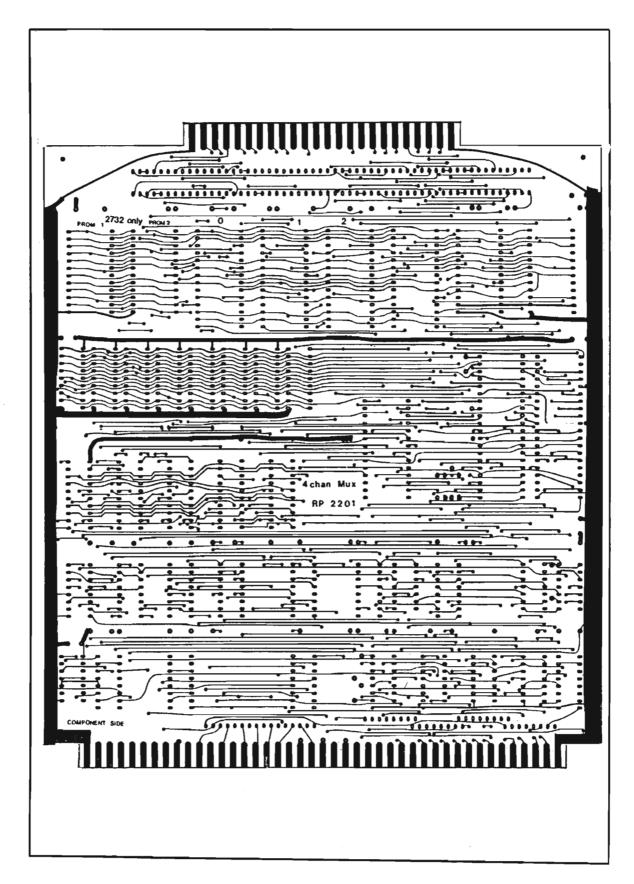

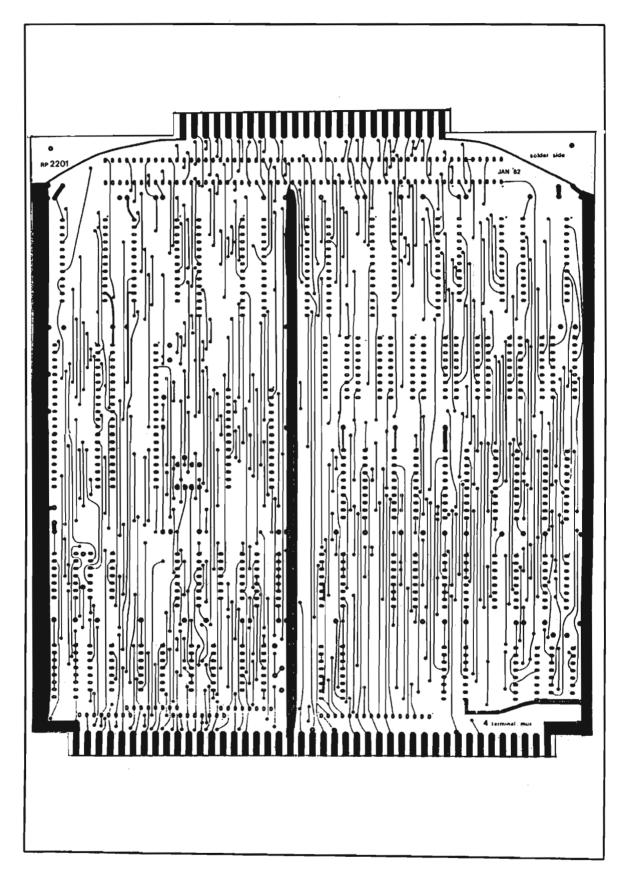

| E.5        | Component Side Track Layout                | 124 |

| E.6        | Solder Side Track Layout                   | 125 |

| F.1        | Exchange Format                            | 127 |

| F.2        | Format of an Exchange Table Entry          | 129 |

| F.3        | Task Control Block Format(TCB)             | 130 |

| F.4        | Message Queue Header Table                 | 131 |

| F.5        | Memory Buffer Format                       | 132 |

| F.6        | Sample Master Control File                  | 142 |

|------------|---------------------------------------------|-----|

| G.1        | RMUX Multiplexer Message Flow Diagram       | 144 |

| G.2        | Flow Chart for STC INT Interrupt Routine    | 146 |

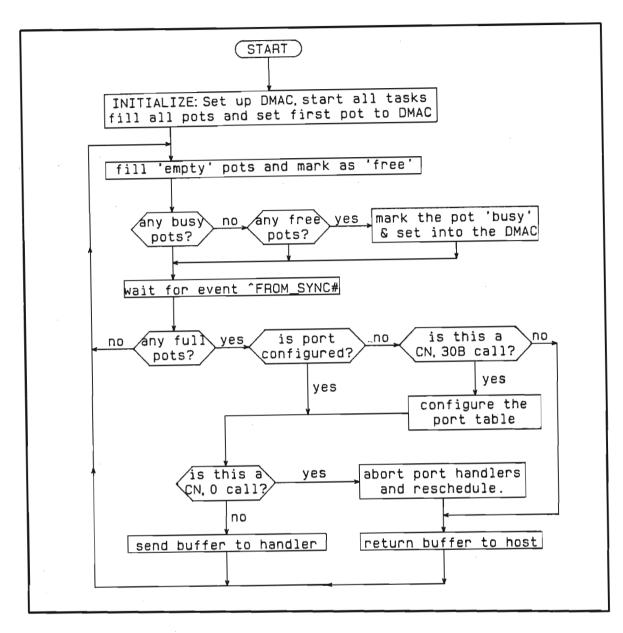

| G.3        | Flow Chart for the FROM HOST Routine        | 148 |

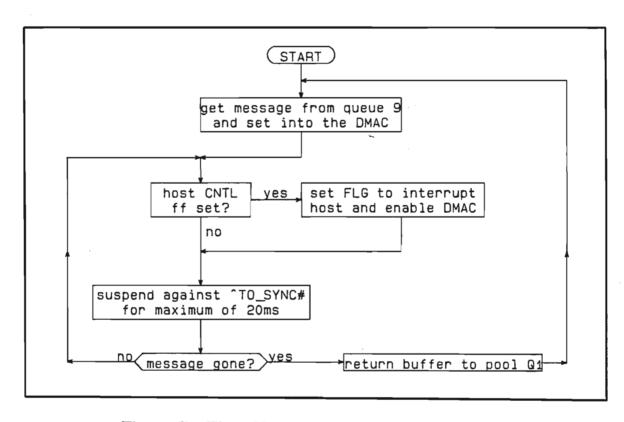

| G.4        | Flow Chart for the 'TO HOST Routine         | 149 |

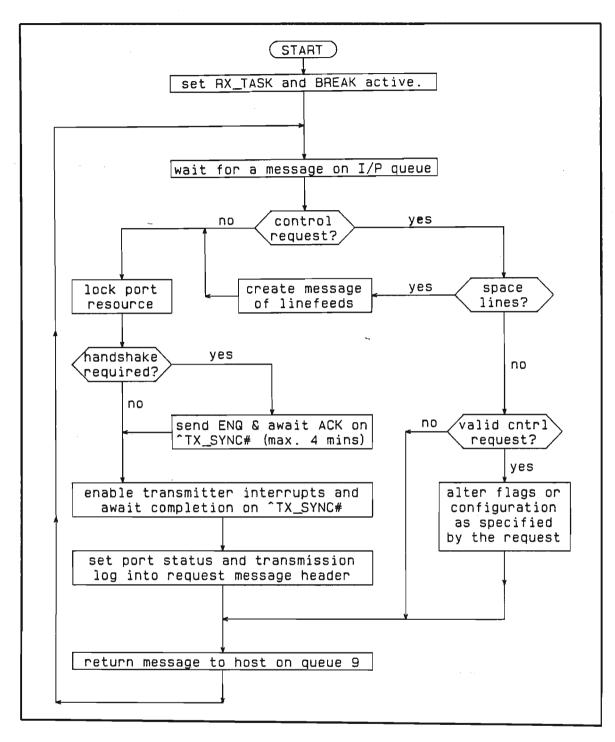

| G.5        | Flow Chart for Terminal Task TX TASK        | 151 |

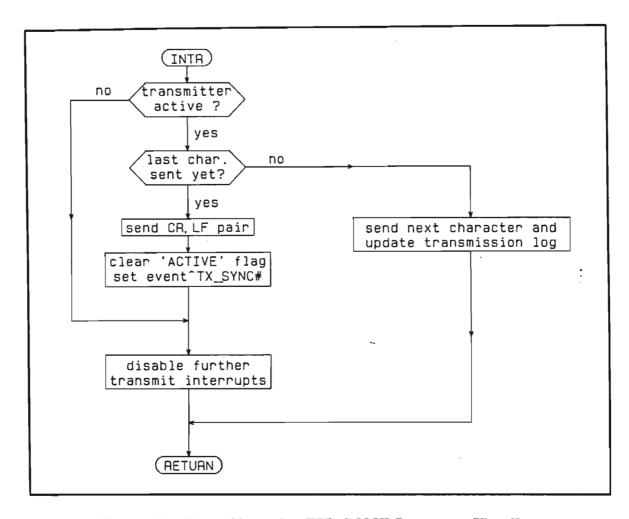

| G.6        | Flow Chart for TX CONT Interrupt Handler    | 152 |

| G.7        | Message Buffer Format                       | 153 |

| G.8        | Receive Interupt Handler Flow Chart         | 156 |

| G.9        | Flow Chart for BREAK Task and Interupt      | 158 |

| H.1        | Equipment Table Entry Format                | 163 |

| I.1        | Read/Write request message format           | 170 |

| I.2        | Control request message format              | 171 |

| I.3        | Message packet input flow                   | 177 |

| <b>I.4</b> | Message packet output flow                  | 178 |

| I.5        | EQT entry usage by DVX05                    | 179 |

| I.6        | Status bits in EQT5                         | 179 |

| I.7        | Driver return error codes (B5-3 of EQT5)    | 180 |

| I.8        | Read/Write Conword bit definition           | 180 |

| I.9        | Control request conword bit definition      | 180 |

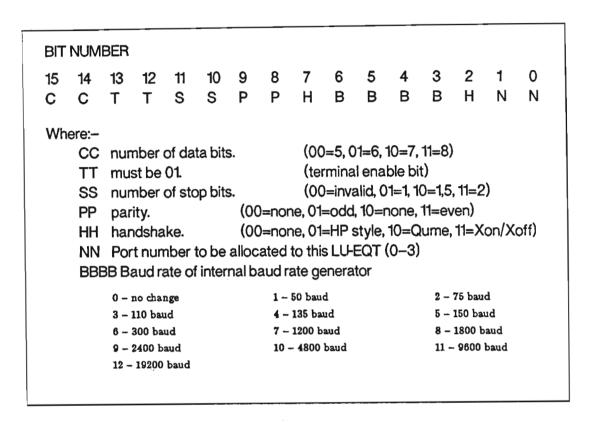

| K.1        | Control 30B call configuration parameter    | 198 |

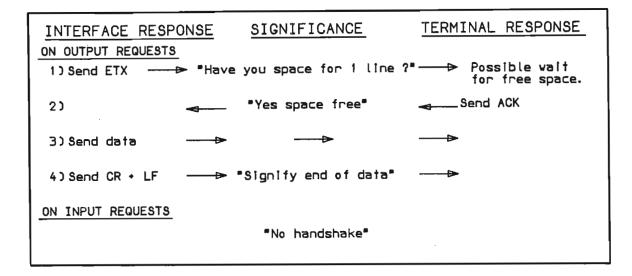

| K.2        | XON/XOFF style handshake protocol           | 199 |

| K.3        | HP style handshake protocol                 | 199 |

| K.4        | QUME style handshake protocol               | 200 |

| K.5        | Special character processing for normal     | 210 |

| K.6        | Control calls for the RMUX interface        | 202 |

| K.7        | Read and write calls for the RMUX interface | 202 |

## **TABLES**

| 7.1        | Interface Timing Results                      | 75  |

|------------|-----------------------------------------------|-----|

| 7.2        | Host Efficiency with different Interfaces     | 78  |

| A.1        | 48 pin Terminal Connector Assignments         | 89  |

| <b>A.2</b> | 116 pin Interface backplane signals           | 90  |

| B.1        | Printer Signal Definitions                    | 98  |

| C.1        | Print Record Control Characters               | 101 |

| E.1        | Serial Port Address and Pin Assignments       | 115 |

| <b>E.2</b> | 48 pin Peripheral Connector Assignments       | 120 |

| E.3        | 86 way Backplane Connector Assignments        | 121 |

| E.4        | Parts list for RMUX Multiplexer               | 122 |

| G.1        | Conword Option bits for Read and Write Calls  | 159 |

| G.2        | Control Request Options                       | 160 |

| G.3        | Configure Request Format (control 30B call)   | 160 |

| G.4        | Special Character Processing for Read Request | 161 |

| K.1        | Signal pinouts on terminal interface          | 204 |

| K.2        | DTE connections according to RS232C           | 206 |

## Glossary

ACK ASCII character for acknowledge. Value 05H. (CNTRL F).

ADSTB Address strobe. A signal strobe generated by the INTEL 8237 DMA controller.

AEN Address enable. A signal strobe generated by the INTEL 8085 microprocessor.

ASCII American Standard Code for Information Interchange.

ASMI The original 8085 cross assembler that ran on the HP1000 computer.

AUTOR The power fail – auto re-start programme used by RTE-IVB.

BACI Buffered Asynchronous Communications Interface for HP1000 series mini-

computers.

BS ASCII character for back space. Value 08H. (CNTRL H).

CCZ Character Count Zero. A logic signal used in the Honeywell line printer controller.

CHS Character Strobe. A logic signal used in the Honeywell line printer controller.

CIC Central Interrupt Control. The interrupt control programme used by RTE-IVB.

CLC Clear Control. A logic signal and an assembler instruction used in the HP1000.

CLF Clear Flag. A logic signal and an assembler instruction used in the HP1000.

CMOS Complementary Metal Oxide Semi-conductor.

CNTL Abbreviation for control. Applied to the control key of an ASCII keyboard

CNTRL see CNTL.

CNWRD Abbreviation for the Control Word in an EXEC call as used in RTE-IVB.

CONWRD see CNWRD. (alternate abbreviation)

CONWRD see CNWRD. (alternate abbreviation)

CR ASCII character for Carriage Return. Value 0DH. (CNTL M)

CRS Controlled Reset. A logic signal used in the HP1000 I/O device interfaces.

CTCBAD Current Task Control Block Address. A variable used in the MTX executive.

CTCBID Current Tack Control Block Identifier. A variable used in the MTX executive.

CTS Clear To Send. A logic signal defined for the RS-232-C serial interface.

DCPC Dual Channel Port Controller. The DMA logic card in the HP1000.

DEL The ASCII character for Delete. Value 7FH.

DMA Direct Memory Access.

DMAC Direct Memory Access Controller. The mnemonic used by INTEL for their 8237

controller IC.

DRQ DMA Request. A logic signal.

DSR Data Set Ready. A logic signal defined for the RS-232-C serial interface.

DTE Data Terminal Equipment. An RS-232-C term used to refer to the terminal devices

in a terminal to modem link.

DTR Data Terminal Ready. A logic signal defined for the RS-232-C serial interface.

EIA Electronic Industries Association.

ENF Enable Flag. A logic timing signal (T2) used in the HP1000 I/O system.

ENQ The ASCII character for Enquire. Value 05H. (CNTL E)

EOB End Of Block. A logic signal generated by the DMAC.

EOT The ASCII character for End Of Tape. Value 04H. (CNTL D).

EPROM Electrically Programmable Read Only Memory. A term applied to a popular class

of memory IC's.

EQT Equipment Table. A major table in the RTE-IVB system.

ESC The ASCII character for Escape. Value 1BH. (CNTL [).

ETX The ASCII character for End Of Text. Value 03H. (CNTL C).

EXCHG Exchange. A major data structure in the MTX executive.

EXEC The subroutine call used to access all RTE-IVB system features.

FF The ASCII character for Form Feed. Value OCH. (CNTL L).

FIFO First In - First Out memory system.

FLBF Flag Buffer Flip Flop. A logic flip flop on the HP1000 interface subsystem.

FLG Flag Flip Flop. A logic flip flop on the HP1000 Interface subsystem.

FMGR File Manager. The name given to the RTE-IVB command line interpreter and file

management subsystem.

GLITCHES A slang term commonly used to refer to brief unwanted voltage spikes on logic

signals.

GND A term applied to the logic signal ground or zero volts.

HASHING A technique for storing symbols in a table by computing the storage location from

the symbol itself.

HBEN High Byte Enable. A logic signal used on the RMUX.

HED The 8085 cross assembler directive code to specify a heading.

HOLDA Hold Acknowledge. A logic signal used by the 8085 processor.

HOLDR Hold Request. A logic signal used by the 8085 processor.

HP A registered abbreviation for Hewlett Packard.

IAK Interrupt Acknowledge. A logic signal used in the HP1000 I/O system.

IDS80 The model name for the main CAD system produced by GERBER SYSTEMS

TECHNOLOGY prior to 1984.

IEN Interrupt Enable. A logic signal used in the HP1000 I/O system.

IFNZ If Not Zero. An assembler directive used in the A8085 cross assembler. IFX If 'X'. An assembler directive used in the HP1000 RTE-IVB assembler.

IFZ If Zero. An assembler directive used in the A8085 cross assembler.

INTA Interrupt Acknowledge. A logic signal used by the 8085 processor.

INTR Interrupt Request. A logic signal used by the 8085 processor.

IOG I/O group. A logic signal used in the HP1000 I/O system.

I/O Input. A logic signal used in the HP1000 I/O system.

I/O Output. A logic signal used in the HP1000 I/O system.

I/O Read. A logic signal generated by the 8085 processor.

I/O Write. A logic signal generated by the 8085 processor.

IRQ Interrupt Request. A logic signal used in the HP1000 I/O system.

JMP Jump. An assembler instruction for the 8085.

JSB Jump Subroutine. An assembler instruction for the 8085.

KBAUD Abbreviation for Kilo-Baud, the signal frequency of a data line. Commonly used

(incorrectly) in place of bits per second.

KBIT Kilo-bit. 1024 bits of data.

KBYTE Kilo-byte. 1024 bytes (8 bits) of data.

KHZ Kilo-hertz. 1000 Hertz or cycles per second. A unit of frequency.

LBEN Low Byte Enable. A logic signal used in the RMUX.

LDA An assembler mnemonic for load accumulator used in both 8085 and HP1000

assemblers.

LF The ASCII character for Line Feed. Value 0AH. (CNTL J)

LIA Load into A. An assembler instruction for the HP1000.

LSB An abbreviation for the Least significant bit/byte.

LSI Large Scale Integration.

LU Logical Unit. A number used in the RTE-IVB system to describe any addressable

device.

LXI An assembler instruction for the 8085 processor to load a double register with a

constant.

MEMR Memory Read. A logic signal used by the 8237 DMA controller.

MEMW Memory Write. A logic signal used by the 8237 DMA controller.

MERG An assembler directive defined for the A8085 cross assembler to merge files.

MHF Manual Head of Form. A logic signal used by the Honeywell line printer.

MHZ Mega-Hertz. 1 000 000 hertz or cycles per second. A unit of frequency.

MIA Merge into A. An assembler instruction for the HP1000.

MPU Micro-processor Unit.

MSB An abbreviation for the Most significant bit/byte.

MSI Medium Scale Integration.

MSS Manual single space. A logic signal used in the Honeywell line printer.

MTX The name given to the small multi-tasking executive written for the RMUX.

MVI Move Immediate. An assembler instruction for the 8085.

NAMR The term used to fully describe a file in RTE-IVB which includes several sub-fields.

NAND Negative AND. A standard boolean logic gate.

NS Nano-seconds. A unit of time.

NSEC see NS.

NSEG New segment. An assembler directive defined for the A8085 assembler.

NYBBLES A term used to describe 4 bits of data.

OE Output Enable. A logic signal used by many logic devices.

OOF Out Of Forms. A logic signal used in the Honeywell line printer.

OPCODE A term used for the operation code in any assembler instruction.

ORG Origin. An assembler directive used to set the value of the programme counter.

OTA Output A. An assembler instruction used in the HP1000.

PAA Print Address Advance. A logic signal used in the Honeywell line printer.

PAC Print and Compare. A logic signal used in the Honeywell line printer.

PCB Printed Circuit Board.

PES Printer Emergency Stop. A logic signal used in the Honeywell line printer.

PIC Programmable Interrupt Controller. The Intel 8259 IC.

PLP Paper Line Pulse. A logic signal used in the Honeywell line printer to signal the

movement of the paper.

POPIO Power On Preset for I/O. A logic signal used in the HP1000 I/O section.

PPLS Printed circuit Pattern Layout System. A Sperry Univac programme for the layout

of pcb's.

PRH Priority High. A daisy chained logic signal used in the HP1000 I/O section.

PRL Priority Low. see PRH.

PRMPT The unsolicited input handler in the RTE-IVB system.

PSW Programme status word. The flags and accumulator can be combined on the 8085

into a single 16 bit register for stack pushes and pops.

PVH Paper Velocity High. A logic signal used in the Honeywell line printer to drive the

paper feed moter at high speed.

PVL Paper Velocity Low. (see PVH).

RAM Random Access Memory. A term usually applied to read and write memory.

RESNET Resistor Network. A network of thick film resistors which are usually very closely

matched thermally.

RET Return. An assembler instruction to return from a subroutine call.

RMX The name of the Intel multi-tasking executive for use on 8085 processors.

ROM Read Only Memory.

RSEG Replace Segment. A special assembler directive defined in the A8085 cross assembler.

(see also NSEG).

RTE Real Time Executive. The name of the Hewlett Packard real time operating system

for HP1000 series computers.

RTIOC Real Time I/O Controller. The name of the RTE processor used to handle all I/O

requests in RTE.

RTS Request To Send. A logic signal defined in the RS-232-C standard for serial

communication.

RXD Receive Data. A negative true logic signal defined in the RS-232-C standard for

serial communication.

RXRDY Receiver Ready. A logic signal generated by the Intel 8251 serial communication

chips.

SBD Sentinal Bit Detect. A logic signal used in the Honeywell line printer controller to

indicate the end of a print buffer.

SC Select Code. A term applied to the I/O address in the HP1000 system.

SCL Select Code Low. A logic signal used in the HP1000 to select devices that match the

low digit of the octal I/O address.

SCM Select Code Most. A logic signal used in the HP0100 to select devices that match the

high digit of the octal I/O address.

SEL Select. A logic signal generated in the RMUX when both the SCL and SCM

addresses match the interface address.

SFC Skip if Flag Clear. A logic signal and assembler instruction of the HP1000.

SFS Skip if Flag Set. (opposite effect to SFC).

SHLD Store HL direct. An assembled instruction for the 8085.

SID Serial In Data. The single bit input of the 8085 processor.

SKF Skip on Flag. A logic signal used in the HP1000 I/O system.

SKP Skip. An assembler directive to skip a page on the list device.

SPC Space. An assembler directive to skip lines on the list device.

SRQ Service Request. A logic signal used in the HP1000 I/O system.

SSI Small Scale Integration.

STA Store Accumulator. An assembler instruction for both the 8085 and the HP1000.

STC Set Control. A logic signal and an assembler instruction in the HP1000.

STF Set Flag. A logic signal and an assembler instruction in th HP1000.

SVPC Save Programme Counter. An assembler directive defined in the A8085 assembler

for segment manipulation.

SYN The ASCII character for Sync. Value 16H. (CNTL V).

TCB Task Control Block. A 72 byte data structure used in the MTX executive.

TCP True Compare. A logic signal used in the Honeywell line printer.

TLOG Transmission Log. A count of the characters sent. Used in the RTE-IVB I/O

system.

TTL Transistor transistor logic.

TTY Teletype. An abbreviation for a simple terminal as typified by the products of the

Teletype Corporation of America.

TXD Transmit Data. A negative true logic signal defined in the RS-232-C standard for

serial communication.

UART Universal Asynchronous Receiver Transmitter.

UNL Unlist. An assembler directive used to control the listing.

USA User save. An assembler instruction used in the HP1000 to save the user mapping

registers.

USART Universal Asynchronous/Synchronous Receiver Transmitter.

WR Write. A logic signalused in the RMUX.

WVA The location prefix used in the Honeywell line printer to specify the printer logic

frame.

XOFF Transmit off. The ASCII DC3 signal (CNTL S) is usually used for this in band flow

control method.

XON Transmit on. The ASCII DC1 signal (CNTL Q) is usually used for this in band flow

control method. (see XOFF).

## Chapter 1

#### 1.1 Introduction

Three separate developments all aimed at improving or extending the Input/Output facilities offered on the Hewlett Packard HP1000 series minicomputers are described.

The first project, to extend the number of terminal ports, was developed using discrete logic for all functions. It consisted of a specialized backplane extender to hold up to sixteen interface cards. These interfaces were designed to emulate exactly the standard HP12531 teletype card, but made use of modern MSI and LSI devices to reduce component count and centralize control.

The second project, used as a test bed project for incorporating a microprocessor peripheral controller into a larger system, was the development of a controller for a 300 line per minute line printer. This project illustrated the potential of the microprocessor, as the resulting controller handled nearly every aspect of the printer control, allowing much of the original discrete logic in the printer itself to be removed.

The third and major project was to produce an intelligent, single board terminal multiplexer to connect to four independent asynchronous terminals. A microprocessor and several sophisticated microprocessor peripheral controller chips were used in the design, resulting in a terminal interface that was not only four times as dense as the standard teletype interface but also some thirty times more frugal in its demands on the host machine's time, and offered a far wider range of features.

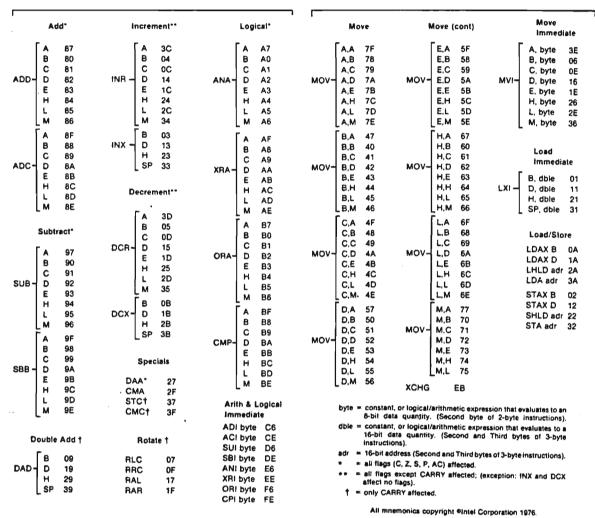

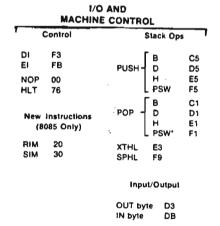

Chapters five and six describe the software developed for this multiplexer, which consisted of an Intel 8085 cross assembler to run on the HP1000 computer, a semaphore driven multitasking operating system for the 8085, the fifteen communication tasks used to control all the interface functions, and finally, the special two part driver needed to enable the Hewlett Packard RTE-4B operating system to accept four fully independent terminal ports on one interface card.

The report finally describes some of the tests that were carried out on the interface performance. The results obtained show that this interface offers a significant reduction in host machine overhead, even when compared to Hewlett Packard's more sophisticated and expensive interfaces.

As with most development projects, hindsight can produce many new ideas and better ways of implementing something and this project was no exception. Thus, the concluding chapter describes some of the possible options that could be incorporated in the interface, as well as some improvements that could be made in the initial design, now that more sophisticated devices are available.

The first model of this interface has been installed for some five years, and at time of writing, there were more than twenty production versions in operation, indicating that the philosophy of an intelligent multi-terminal interface has produced an effective product.

The remainder of this chapter gives a brief outline of the history of computers with specific reference to the use of intelligent controllers to reduce CPU overhead in peripheral transactions. It is on the basis of this history that this particular project evolved.

### 1.2 A Brief look at Peripheral Control in Computers

Computers are generally accepted as belonging to one of three categories, namely, mainframe, mini—, and micro-computers. This classification is based roughly on the size of the machine, but is rather vague with many areas of overlap.

Mainframes evolved from the original computers and still tend to occupy several large cabinets of electronics, consume large amounts of power, and require special computer rooms with carefully controlled environments. Their operating systems are usually suited to batch mode processing where the CPU can be kept busy, while their I/O system is suited to moving large quantities of data rapidly between a very small range of peripherals such as discs, magnetic tapes, and line printers.

As computerised control of machinery became a reality, the high cost of mainframe computers when coupled with their high speed and their limited variety of I/O systems made them unsuitable for most control applications. As a result, the minicomputer was born, initially to act as a slave I/O controller for a mainframe, and ultimately as a computer in its own right.

These minicomputers were characterised by small size (typically only one small cabinet), low cost and very versatile I/O systems. They were designed to run real time control programmes using their versatile interrupt systems to capture data which was then passed onto the host mainframe for processing.

In time, these real time programmes developed into real time operating systems, and the minicomputer developed its own market for computing, complementing rather than competing with the mainframe market.

While minicomputers grew from dedicated controllers into fully fledged computer systems, following the same growth path that mainframes had taken, the integrated circuit revolution gave birth to the microprocessor, a small, limited function computer on a single chip of silicon. Initially developed without a goal, the microprocessor was soon recognised to be an ideal substitute for a minicomputer in many small control applications.

The situation had now evolved where mainframes were too large for control supervision activities, being more suited to running accounts, orders and all other administrative functions of an organization, while the minicomputer had grown sufficiently to be able to control large sections of a plant. The microprocessor then became the ideal candidate for small control problems, and in this field the microprocessor has flourished.

It is interesting to note that while mainframe manufacturers were quick to incorporate minicomputers into their mainframes as dedicated I/O controllers, the minicomputer manufacturers, traditionally loathe to accept any ideas from their big brothers, were slow to incorporate microprocessors into their machines. In fact the microprocessor manufacturers themselves were far quicker to apply the multiprocessing concept and have produced some very sophisticated peripheral controller chips each incorporating its own microprocessor. The availability of these easy to use, sophisticated support chips has made the microprocessor into an extremely powerful device; now, a scant ten years after its invention, the microprocessor is being used in every form of computing imaginable. It is no longer merely looked upon as a useful I/O controller.

While it was stated that minicomputer manufacturers themselves were slow to adopt the microprocessor as a peripheral controller, many independent manufacturers of minicomputer peripheral controllers have incorporated microprocessors into their products, often with dramatic improvements in cost, speed, size, and ease of use.

The development of the four-terminal intelligent multiplexer was undertaken in order to produce a product which was not available from Hewlett Packard and which would offer improved features due to its programmability.

## Chapter 2

## An I/O Expander for Terminal Interfaces

#### 2.1 Introduction

The Hewlett Packard HP1000 series minicomputer used by the Department of Electronic Engineering of the University of Natal (Durban), has a maximum I/O addressing capability of 56 device interfaces, of which only 14 may be installed in the computer cabinet itself—any further interfaces requiring an extender cabinet. With the advent of the multi-user operating systems of RTE-3 and RTE-4B, the need for terminals quickly exhausted the available slots in the mainframe. The solutions were either to buy an extender and the required terminal interfaces from Hewlett Packard, or to design a suitable extender and build it. To save funds, and also to provide a medium for an in depth study of the HP1000 I/O system, the latter approach was adopted and a 16 card terminal extender system was developed.

The interface cards were designed to emulate the standard HP12531 teletype interface from both the computer's and the terminal's point of view. Although this saved writing driver software, the resultant card which used an LSI UART (Large Scale Integration Universal Asynchronous Receiver/Transmitter) required that several UART features had to be ignored or even overridden to produce the desired compatibility. In retrospect, this was not the wisest solution to the I/O extension as the extender became obsolete after only four years due partly to its poor performance forced by the emulation.

The remainder of this chapter describes briefly the development of this extender with the principal emphasis on those aspects which influenced the final multiplexer project.

#### 2.2 The HP I/O System

This section describes only those aspects of the HP I/O system that are pertinent to the peripheral controller itself: in this case the serial I/O device. For a more detailed description of the I/O system, see Appendices A and H and the HP reference manual.<sup>[1]</sup>

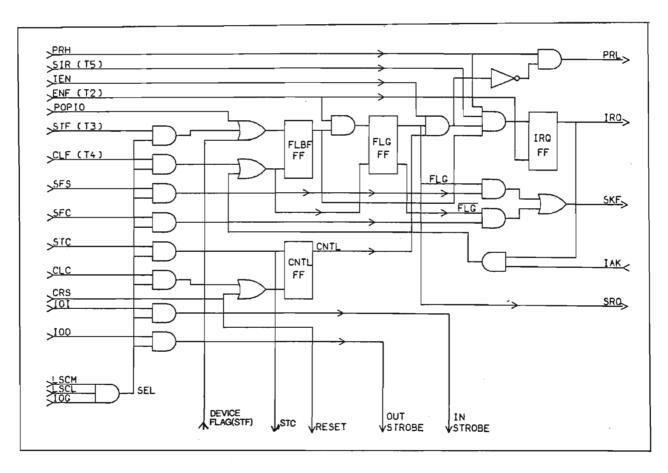

Any HP1000 series interface can be divided into two major sections: the section which contains the specific I/O controller, and the section needed to implement the CPU's interrupt and priority structure which is distributed over all interface cards. This latter section (shown in Fig.2.1) uses some 30 logic gates and typically requires 8 or 9 SSI TTL packages to implement. From this interrupt logic block, an STC strobe, an output strobe (IOO) and an input strobe (IOI) emanate, while a single interrupt input (STF) exists. These are the only signals available for controlling the peripheral section which also has access to a 16 bit bi-directional data bus. The function of the STC strobe is to enable the CPU to command the peripheral section to perform some action without requiring any data transfer.

The limitation of only having one interrupt per device, and no extra signal bits for interrupt source identification, results in the I/O system limiting all I/O to half duplex communication, irrespective of the peripheral section requirements.

Figure 2.1 Standard HP I/O interface control logic

### 2.3 The HP12531 Teletype Interface

This interface, driven by the driver DVR00, was, at the time of the extender development, the most common serial interface for HP1000 series minicomputers, hence the decision to design the new terminal extender to be compatible. The most important features of this interface which influenced the design are covered briefly below, but for full details see the HP12531 interface specification.<sup>[2]</sup>

The serial I/O side of the HP12531 is implemented using a single 11-bit shift register for both input and output, which enforces the half duplex nature of the interface and requires some means of programming the direction of transfer. This is done by using an IN/OUT flip flop programmed from the upper (otherwise unused) bits of the data word. Thus, to program the interface, a data word is output with bit 15 set to act as a program enable bit. To stop the lower 8 bits of this word being transmitted however, the logic was designed so that the output instruction merely latches the data into the output shift register and an STC instruction is required to initiate the actual transmission.

In order to be able to detect any input characters arriving during output, the input to the shift register is left connected to the data line and the shift register contents are examined after each character transmission. Should any input character have arrived during this time, then the shift register would not contain all ones, as it would have had it just clocked in an idle line. Although this feature does not enable the input character to be determined, it is used by DVR00 to determine when a user wishes to interrupt an output stream, an otherwise difficult problem in a half duplex system such as this.

Another problem which can arise from such a simple system with no data buffering is that of an overrun error which occurs when a new character arrives at the serial input of the interface before the CPU has read the previous character. This situation is dealt with in the HP12531 plus DVR00 setup by gating the input to the shift register once a character has arrived, and leaving it closed until the character has been read. This stops any further input from corrupting the character already in the shift register. In order to detect the arrival of another character, a flip flop is set whenever the input line changes to a zero (e.g. as for a start bit) and the state of the flip flop is read back as bit 15 of the returned data, thus acting as an overrun indicator. Since there is no buffering on this card, the CPU only has one half of a stop bit time in which to respond before the next character may start, a limitation which causes frequent overrun errors.

#### Other features of the card were:

- (a) On card crystal controlled baud rate clock.

- (b) RS232 and 20mA current loop inputs and outputs.

- (c) Capability to turn on either printer or punch on a teletype.

- (d) Ability to run from an external clock of 8 times the data rate.

- (e) No facilities for MODEM control.

#### 2.4 The Expander Mainframe

In developing the 16 slot terminal expander, it was decided to:

- (a) Make as much use of MSI and LSI as possible.

- (b) Centralize as many functions as possible rather than replicating them on each card.

- (c) Customize the extender mainframe specifically for terminal interfaces.

- (d) Make the unit daisy chainable so several extenders could be added if required.

The extender was designed to connect to the computer via the HP Multiplexer I/O Accessory kit<sup>[3]</sup>, which brings out all the backplane signals, buffered, onto a 100 way edge connector. A 50 pair cable connected this card to the extender, on which was mounted another 'T'-connected 100-way edge connector for the daisy chaining of extenders. The signals were also connected to the extender control card, which buffered all the signals onto the extender backplane (see Appendix A).

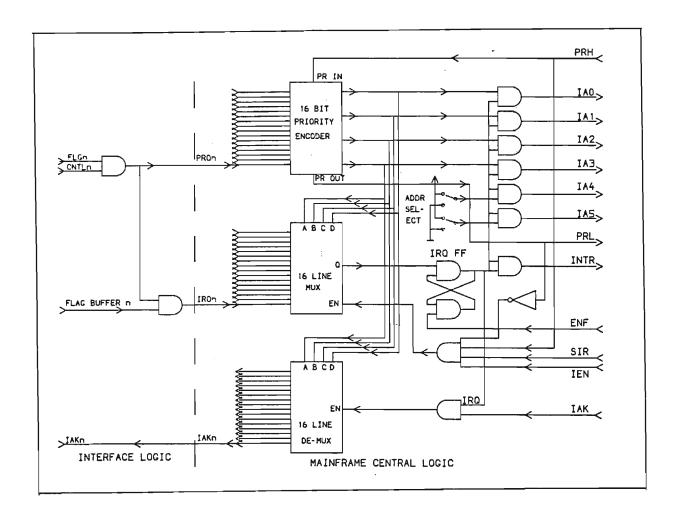

In an effort to reduce component count on the interface cards themselves, the interrupt request logic and priority encoding logic was moved to a master control card as shown in Fig.2.2. This achieved a saving of 2 to 3 chips on each interface card at the cost of about 5 extra chips on the master control card. More significant was the time saving that was achieved in the priority logic by using a priority encoder rather than a discrete gate on each interface. This reduced priority settling time from 16 gate delays to 3 gate delays. To save having individual baud rate generators on each interface card, a central baud rate generator was included on the master control card, common baud rate clocks being produced and wired down the backplane. Finally address selector links were added to the master card so that it could be set to answer to any block of sixteen consecutive addresses.

Figure 2.2 Master control card schematic.

The extender frame itself consisted of a standard 4 unit high RETMA rackmount cabinet with the power supply in the front section and the interface cards plugging into the rear section from the top. This concept of using top insert cards was only adopted to cope with the large connector hoods used on standard HP12531 interfaces, an otherwise poor idea owing the problem of plugging cards in when the unit is installed in a full rack. Either the unit needed to be slide mounted and have plenty of cable slack to allow the unit to slide out, or there had to be plenty of room above the extender, so wasting rack space.

#### 2.5 The Terminal Interface

The interface card itself was built using a 40 pin LSI UART (Universal Asynchronous Receiver Transmitter) as the main functional unit. This UART performs every peripheral function required of a non modem compatible RS232 serial interface, and had the interface not been designed to emulate an HP12531, this UART alone would probably have been all that was necessary.

To allow for the output command to latch the data and an STC instruction to initiate transmission, an extra 8 bit latch had to be included between the data bus and the UART, while to supply an "all ones" return character whenever there was no valid character to read, required the addition of an extra eight bit tri-state buffer. This buffer was only enabled for the duration of the first read command subsequent to each received character. Thus, should the host execute a read command with no data available, the floating tri-state data bus would return the "all ones" result required by DVR00.

Due to the fact that the UART has completely separate transmit and receive sections, both double buffered, the overrun error problem which was so obvious with the HP12531 was much less so with the UART since the CPU has an entire character time to respond to an interrupt and read the character before the next input character can interfere. However to maintain exact compatibility with the HP12531, a BUSY IN flip flop was added to the interface and connected to return bit 15. This flip flop, as in the HP12531, gets cleared whenever a character is correctly received and set again whenever the input data line drops to a zero, thus allowing DVR00 to determine whether a character was arriving during a read of the previous character. Since the UART could be programmed for parity, stop bits and data word length (all features unavailable on the HP12531) switches were added to the interface to allow these options to be selected. This, while not compatible, did not interfere with DVR00 operation and could still be set to be compatible should the need arise.

The baud rate selection was implemented using a 12-way set of DIP rocker switches, allowing selection of any one of the 10 preset baud rate clocks from the backplane, or an 8 times or 16 times external clock. Since the UART requires a 16 times clock, and the HP12531 an 8 times clock, a frequency doubler had to be included on the interface. Fortunately, the UART was found to be almost totally insensitive to the mark-space ratio of the clock, allowing a simple exclusive-nor, edge sensitive pulse generator to be used for the doubling. Another non compatible feature which could be added since it did not affect DVR00 operation

was to return the three UART error signals, Framing Error, Overrun Error and Parity Error in bits 14-12. This was included to allow for possible use by some future driver, should one ever be written.

#### 2.6 Conclusion

This project succeeded in its aims in that it supplied fourteen extra terminal interfaces which were used for four years, at about eight percent of the cost of a comparable system from Hewlett Packard, as well as providing an incentive for a thorough investigation into the HP1000's I/O system. Perhaps more than anything else, the half duplex nature of this entire system was highlighted by installing a full duplex device and then having to add extra logic to degrade the functions of this cheap and effective LSI UART in order to achieve compatibility.

In packaging the extender, several small but nevertheless important lessons were learnt:

- a) Using a manually taped PCB master resulted in excessive tolerance on edge connector fingers such that the circuit boards could be inserted so as to cause shorts or missed connections.

- b) The backplane connectors were of the "cut to length" variety in which the end stops are inserted after cutting. These connectors exhibit excessive tolerance such that when the cabinet was twisted in any way, the resultant movement of the cards invariably resulted in connector shorting.

- c) Using a layout which required a top insertion board was not a good idea at all, and so boards should be made for front or rear insertion.

- d) No edge connectors were gold plated and when the power was switched off each night, the thermal cycling and its attendant expansion and contraction cycles caused connectors to "shuffle" giving many bad connection problems. The solution was to gold plate the connector fingers and to leave the power applied continuously.

This expander did produce a useful addition to the computer's complement of terminals, and remained in service for some four years until it was made obsolete by the four terminal multiplexer described later on in this report.

## Chapter 3

### An Intelligent Controller for a Drum Printer

#### 3.1 Introduction

The investigation into DVR00 and its HP12531 teletype interface, plus an isolated effort at working on the Centronics line printer driver (DVR12), illustrated clearly how intimately involved the CPU had to become with each of the peripherals it used. It was certainly a long way from the ideal situation where the host should expect the peripheral to manage all the peripheral dependent features. Now while this attitude was understandable in the past due to the expense and difficulty in producing "ideal" peripheral controllers, the arrival of the cheap and powerful microprocessor should enable "ideal" peripheral controllers to be built cheaply.

To test this view and gain some experience before attempting the final project of an intelligent four terminal multiplexer, the author designed a controller for a 300 line per minute Honeywell drum printer which had been donated, controller-less, to the Department of Electronic Engineering. This printer contained a rack of some 30 circuit boards, each 100mm square; it should also have had a controller of unknown size and, after all this, the Honeywell host CPU was still required to output the entire line of characters to be printed sixty three times, once for each character row on the print drum. This task, which meant that the CPU had to output a character every 6 microseconds, must have kept the original CPU fully occupied for the entire 200 milliseconds taken to print a line, an obvious waste of CPU time.

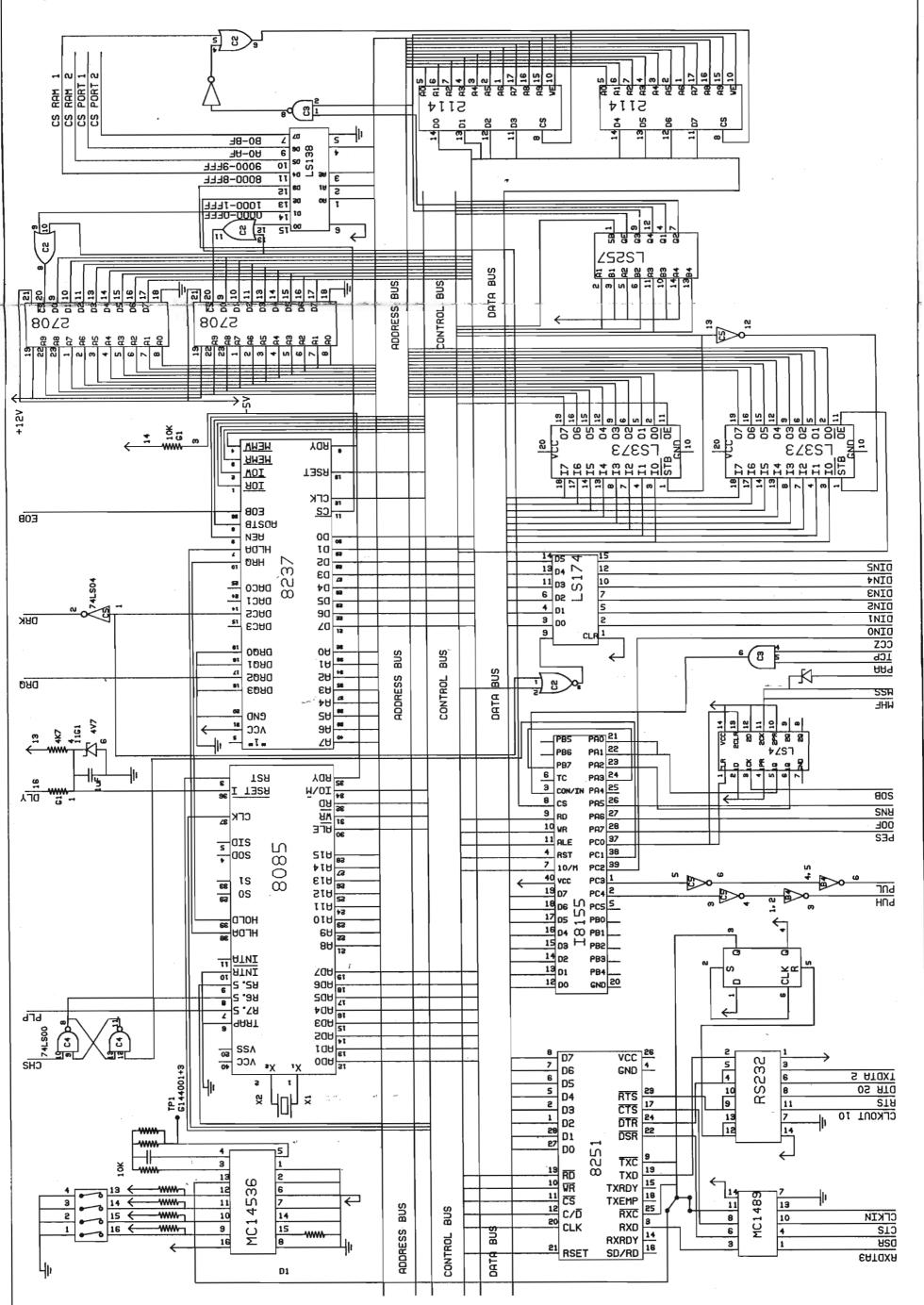

The final design used an 8085 microprocessor situated in the printer and communicating with the host (HP CPU) over a serial line using a very simple message protocol which was chosen to be almost completely device independent. Thus, the custom driver written for the HP was short, simple and contained no code specifically related to handling a line printer.

Since the printer controller was basically designed as a test bed for ideas to be incorporated into the final multiplexer project, and since both the printer and the printer controller were relatively complex, this Chapter covers these factors very superficially and concentrates mainly on the software layout, the use of a DMA controller and the message protocol. Appendices B, C and D cover the hardware, software and driver in more detail.

### 3.2 Printing on a Drum Printer

The Honeywell 112 printer is a drum printer capable of printing 300 lines per minute. To accomplish this, the printer contains a character drum rotating at 300 rpm directly in front of the paper. The drum has 63 rows of raised characters, each row containing 132 identical characters, one in each column position. Behind the paper, a row of 132 solenoid driven hammers is situated, while an inked ribbon passes between the paper and the print drum. To print a line of text, as each different row of characters comes up in front of the print hammers, the hammers are fired only in those column positions where the particular character is desired. Thus, the logic has to scan the line of text to be printed each time a new character line appears under the hammers, and decide which hammers are to be fired. Since a new line of characters appears every 3,2 ms and a print line may contain 132 characters, each character comparison would have to be performed in 24 microseconds. In practice, this time is reduced to 6-9 microseconds since much of the 3,2 ms interval must be devoted to the actual printing process of setting up and firing the hammers. Thus, any controller would have to execute the following sequence for every line of text to be printed:

- (a) Fetch the text line to be printed and store it in the scan buffer.

- (b) Await a strobe which indicates that a new line of characters is about to come up under the hammer.

- (c) Determine which character it is that is about to come under the hammer and be printed.

- (d) Scan the scan buffer, checking for the print character and where found, shift a '1' into a 132 bit print buffer, while for every false comparison shift a '0' into the print buffer.

- (e) Once the scan buffer has been completely scanned, pad the print buffer with '0's until all 132 positions are full.

- (f) Send a strobe to initiate the hammer firing process.

- (g) Check if all the characters in the scan buffer have been printed if so, go to (a) for the next line after moving the paper, if not, return to (b) for the next print character.

This cycle occurs every 3,2 ms.

The controller would also have to look after all the paper feed control and page formatting. To do this, it was required to become part of the servo loop and control the paper feed motor speed depending upon how many lines of paper were to be skipped. This fortunately was a simple problem as the paper feed motor only possessed two speeds.

#### 3.3 The Controller Hardware

It was obviously impossible for a microprocessor to perform the print line scanning under software, so it was decided to incorporate a hardware comparator driven by data from a DMA controller and timing signals from a small timing logic circuit. This left the microprocessor software to handle all the data input, data sorting, printing setup and paper formatting.

### The Timing Logic Card

The timing and comparison logic was included on a separate card from the processor module, with signals arranged so that a simple test module could be used to test the printer in place of the microprocessor module. The logic and timing diagram of this card are shown in Appendix B (Figures B1 and B2).

The timing logic starts a sequence by first synchronising the character strobe (CHS) from the print drum with its own nine microsecond clock and then issuing the first DMA request (DRQ). This would cause the DMA controller to output the first character of the scan buffer which is then passed through two mapping eproms (described below) and two comparators. On the next clock pulse, the result of this comparison (TCP) is clocked into the print shift register (in the existing printer logic) by the printer address advance signal (PAA) while the next DMA request is issued. This sequence continues for the entire line until the shift register "sentinel" bit stops the process. On the next character strobe (CHS), the DMA controller resets to the start of the scan buffer and repeats the sequence from the start of the line again.

The dual comparators with mapping eproms were included to allow over-printing of characters since the print drum was missing several special characters which had to be made up (e.g. A "\$" was made up from an "S" and an "I"). Thus when the DMA logic outputs a "\$" code, the mapping eproms change it to an "S" and an "I" to feed the two comparators.

#### The Processor Module

Apart from the microprocessor itself and a DMA controller, the following major chips were included:

- (a) A serial interface UART to control communications with the host.

- (b) One kilobyte of RAM to contain a circular data buffer.

- (c) Four kilobytes of EPROM to contain the operating code.

- (d) A combination I/O ram chip which supplied a counter for counting the characters as they are printed, a 5 bit output port, a 7 bit input port and 256 bytes of RAM used to store all operating variables.

- (e) A six bit output port to hold the character output by the DMA controller.

- (f) A baud rate generator and RS232 data buffers for the serial communications line.

Although the code occupied less than 2K of eprom, a 4Kbyte 2732 chip was chosen since it was easy to programme and allowed room for possible expansion while the difference in cost between the 2Kbyte and 4Kbyte chips was about R2.00.

The RAM although only 1K in length was given a 4K address space so that it could be treated as a circular buffer by the DMA controller. Thus when the DMA controller addressed past the end of the first 1K, the beginning of the RAM would respond again, giving the so-called circular effect.

The counter was used to count all the TCP (true compare) pulses, and when all printable characters in the line had been printed, the counter output was used to inform the processor. This was required since the printing process was under control of the DMA controller and could not otherwise be monitored by the CPU.

The I/O lines of the I/O port chip were used to monitor the front panel control signals and to drive various control signals within the printer such as the paper feed motor amplifier.

The entire processor circuitry (see Fig.B3) including the serial I/O connector was incorporated onto a single 100 mm square wire wrap board which was plugged into the main card frame.

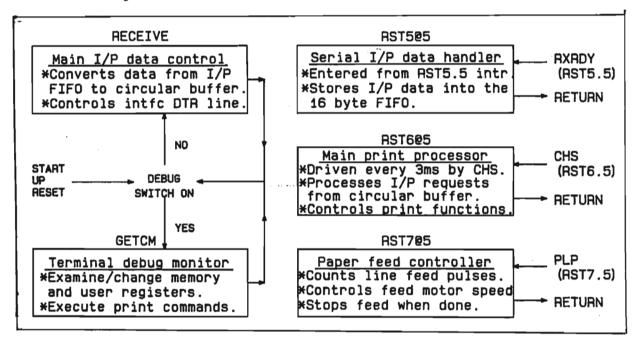

#### 3.4 The Printer Controller Software

The software written to control the line printer was initially conceived as two separate processes, the data producer being the receive input handler, and the data consumer being the actual printer handler with the only junction between them being the 1K circular data buffer and a few flags. To co-ordinate these two essentially independent tasks, the producer was run continuously in a background mode, while the consumer was run every 3,2 ms in a time base interrupt driven mode.

#### The Data Producer

The main receive data handler (RECEVE) was split into two parts:

- (a) The normal input processor was to accept print requests from the host via the serial line, store them in a circular buffer, and stop the flow of data from the host should the buffer ever become too full to handle another complete print request. Transmission would then be held in suspension until such time as only two print requests remained in the circular buffer. This approach was designed to keep the line busy in large blocks and hence reduce programme swapping in the host. The only other function of RECEVE was to convert incoming text data from the ASCII code used by the host to the Honeywell code used by the printer, and to count the number of printable characters in each request record. This printable character count was used as explained in Section 3.3 to determine the end of the printing process.

- (b) A terminal debug monitor (GETCM) which could be run in place of RECEVE allowing the contents of memory to be examined and/or altered. A single bit switch, attached to one of the input port lines was used at power up time to direct the processor to GETCM instead of the normal processor RECEVE. By using GETCM, it was possible to place data requests into memory, alter pointers and counters and then monitor the printing process as these requests were processed. This was used during the development phase to aid in debugging the code, and was subsequently used whenever some hardware failure occurred in the printer logic.

#### The Data Consumer (RST6.5)

This routine, driven from the 3,2 ms character strobe interrupt constituted the most significant process in the controller as it had to supervise and co-ordinate the entire printing process.

Upon entry, each 3,2ms, it was required to first determine what state (or phase) the printer was in which was done by means of several flags (see Appendix C). If in the print phase, the character counter was checked to see whether the phase was complete, while if paper feeding was in process, then the remaining line count was examined to determine the motor speed required or to delay the necessary settling time after the motor had been stopped. If neither printing nor paper feed was in operation, then the input buffer would be examined for any new requests. All new requests were parsed to determine the desired action and then either the printing or the paper feeding process initiated.

The printer control process was used for several other minor tasks, some of the more interesting being:

- (a) To allow for the analogue paper feed servo loop to settle, the routine was entered 3 times after the paper feed motor had been stopped before starting any printing. This allowed a 10ms stabilising time.

- (b) Front panel controls were monitored so that should the printer be placed "OFF LINE" then the remaining front panel controls of "LINE FEED", "FORM FEED" and "SINGLE ORDER BUTTON" were enabled.

- (c) The page position was monitored to maintain the perforation skipover function (if enabled) and to stop multiple form feeds from wasting paper.

#### Interrupt Tasks

Two other interrupt driven tasks were included in the system, one driven by the paper feed motor position indicator to count lines as the paper moved and the other to fetch the input characters from the host.

Since the host could transmit at up to 19200 bits per second, characters could arrive every 500 microseconds but with the consumer process being interrupt driven, and able to run for longer than 500 microseconds, the background task (RECEVE) was incapable of polling the UART and reading all characters. Thus the UART was made to generate an interrupt with each input character and the interrupt handler then stored these characters into a sixteen character FIFO which was emptied by RECEVE. This character buffering effectively overcame the timing problem resulting from having one major task interrupt scheduled and the other running continuously.

### 3.5 The Message Transfer Protocol

Each request from the host was sent with a fixed format starting with an ASCII ENQ character to synchronise the message reception. Following the ENQ the host then sent the data field length, coded into two ASCII characters, in order that the printer controller could check available space left in the data buffer. Should insufficient space exist for the entire print request, the DTR line of the serial interface would be set false. This condition was to stop the host from sending any further data until such time as space became available whereupon the DTR line was set true again.

The next datum sent was a single control character derived directly from the host equipment table entry (EQT) (see Appendix H), and used to indicate the request type. Following this was the print data (if any) terminated by a Return (CR).

#### 3.6 Conclusion

The completion of this project produced several valuable lessons to be applied to any future project, these being related to the message format, the usage of DMA in micro-processors and the software system structure.

The data message format chosen had the advantage of being an almost direct transfer from original request format of length, type and data, through the host EQT and driver, down the serial data line and into the circular buffer. Thus, the only time that any action was taken on the data content was at the printing stage in the controller itself. This made the driver and the message format essentially peripheral independent which was felt to be an important aspect in reducing host CPU load in peripheral handling.

The DMA controller as used in this project demonstrated the simplicity of adding a complex function such as DMA to a microprocessor system, and also showed how, with the addition of little extra logic, a DMA controller could make feasible a project which would be completely impossible to implement in software alone.

The major lesson in this project related to the difficulty of coping with independent concurrent tasks without an operating system to control them. Since only two tasks were involved in this project, and one of them (the Data Consumer) was very time dependent, the solution opted for was adequate to

afford each task a sufficient share of the resources. The only problem resulting from this approach was that of character input which was easily solved with the FIFO buffer. However, the number of flags used to coordinate these two activities was quite large for such a simple interaction and left a very vivid picture of how complex it could become were more tasks to be included in the structure.

## Chapter 4

### The RMUX Terminal Multiplexer—Design aims

#### 4.1 Introduction

This Chapter sets out the design aims and objectives of the RMUX intelligent four terminal multiplexer, starting with a brief look at the features offered by standard interfaces existing at that time. Following this, the overall schematic of an "ideal" multiplexer is presented, containing all the features felt to be both desirable and possible. Due primarily to space limitations, not all these features could be included in a practical design, so the final design concept is then presented with reasons for all the features removed or reduced.

The conclusion of this chapter then attempts to explain how these required features influenced the hardware design and forced the selection of certain components. The final hardware design is presented in detail in Appendix E.

#### 4.2 A Survey of Standard Interface Features

At the time of starting the design of the RMUX interface, Hewlett Packard produced two standard serial asynchronous terminal interfaces, the HP12531 teletype interface described in Chapter 2 and Appendix A, and the HP12966 Buffered Asynchronous Communications Interface (BACI).

The HP12531 offered the following features:

- (a) Both RS232 and 20mA current loop signal levels.

- (b) Only 8 bit data words without any parity option.

- (c) Five link selectable baud rates plus an external 8 times clock.

- (d) Half duplex transmission only.

- (e) Every character caused a host CPU interrupt.

- (f) Driven by DVR00 which occupied only 700 words of memory.

- (g) The driver overhead processing time for a single character interrupt of 350 microseconds resulted in a maximum character rate for DVR00 of 2880 characters per second for a fully extended host CPU.

The HP12966 BACI was a more modern interface which in an effort to reduce CPU loading contained a 128 character FIFO and a 128 character content addressable RAM for special character recognition. This interface in conjunction with its driver (DVR05) offered the following features:

- (a) RS232 signal levels only.

- (b) Modem control signals compatible with the Bell 103 standard.

- (c) Programmable number of stop bits, parity and data character length.

- (d) Wire jumper or programme selection of one of 14 baud rates or a 16 times external clock.

- (e) Half duplex transmission only.

- (f) Could be set to interrupt on every character, or when the FIFO becomes half full (64 characters), or upon the recognition of one of the programmable special characters.

- (g) The interface driver DVR05 occupied 1500 words of memory.

- (h) The average driver processing time for long records resulted in a maximum character rate of about 10 000 characters per second before the host became saturated.

Of the two interfaces, the DVR05/HP12966 set offered far more features and reduced CPU loading by almost four times compared to the DVR00/HP12531 pair. The FIFO buffering on the HP12966 resulted in lines shorter than 64 characters long needing only one interrupt per line of text, rather than one per character, hence offering a considerable potential increase in speed. Unfortunately, much of this potential was lost due to the complexity of the processing needed to service this extremely complex discrete logic card.

In order for DVR05 to be able to programme the HP12966 as well as pass it data, while only having a single 16 bit I/O data path, the top four bits of any word sent to the card are used to specify the data function. This feature adds to the CPU overhead and also requires that the CPU unpack all characters prior to output. Similarly, for input from the HP12966, the upper byte of the returned word contains status information which has to be checked, while the lower byte contains the data character which requires packing into the user buffer. This extra processing required for each character eliminated much of the advantage gained by reducing interrupts to one per block.

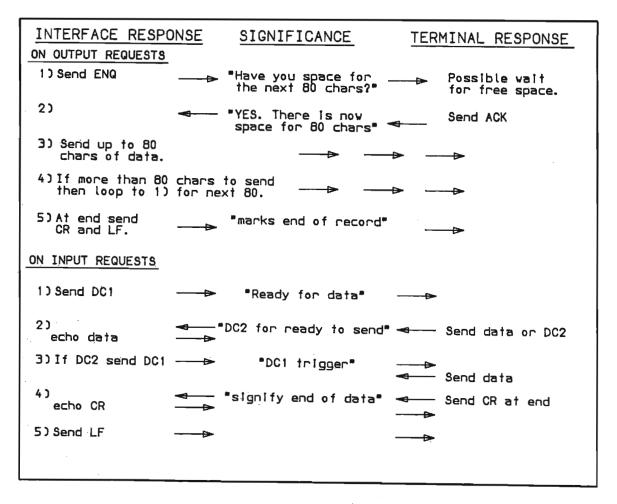

DVR05 uses handshake sequences with the terminal for both input and output in order to determine the state of readiness of the terminal. On output, which is typically the major traffic direction in terminal I/O, the handshake consists of an enquiry character (ENQ) sent every 33 characters to which the terminal must reply with an acknowledge (ACK) when it has space to accept the data. On input, DVR05 first issues a trigger character (DC1) before setting the interface card into a read mode. This is done so as to inform the terminal that it may send data. Both these handshake sequences add several extra interrupts to each record, further increasing the average CPU time per character.

The terminals that DVR05 was designed to drive can be quite complex units with separately addressable keyboards, alphanumeric screen, graphics screen overlay, printer, plotter and cassette tape drives. Furthermore, data from the terminal can be transferred character by character, record at a time in block mode, or a full screen at a time in page block mode. All these options and variations make DVR05 an exceptionally long and complex driver by HP standards, there being virtually no other driver in the system of this length.

## 4.3 Objectives for an "Ideal" Interface

From observing the way that users tend to interact with terminals, and from noting the types of terminal in common use in many installations, several observations could be made:

- (a) A very high proportion of terminal usage time is spent reading or editing alphanumeric text

- (b) Text editing benefits from frequent re-displays of the text around the most recently edited data resulting in frequent page outputs and hence, very high output data rates compared to input data rates. This input to output ratio for editing typically lies between 1:100 and 1:1000.

- (c) Since full feature terminals are expensive and their extra features appear to seldom be used in most installations (e.g. printers and cassette tapes), the majority of terminals used are straightforward text editing terminals.

- (d) During large streams of output it is often necessary for the user to interrupt the output, gain the system's attention and perhaps take some corrective action to stop the output. This should be done by pressing a single "BREAK" key of some form. Due to its half duplex nature, the HP12966 seldom notices a "BREAK" key-in and the resultant panic key bashing of a frustrated user is damaging to both user and terminal.

These factors, when taken in conjunction with the features described in Section 4.2, plus a strong desire to produce an efficient interface with straightforward host interaction resulted in the following design objectives:

- (a) All requests from the host should use a common format when being forwarded to the interface.

- (b) All requests should be passed to or from the interface in single burst mode block transfers.

- (c) Transfers in either direction should be 16 bits wide and capable of running very fast. Ideally, the full DMA burst mode rate of 1 million 16 bit words per second should be possible.

- (d) The interface should perform all request parsing and command interpretation, leaving the host driver merely to act as a medium for passing the requests back and forth.

- (e) All requests whether read, write, control or status should originate from the host and be acknowledged when the interface has completed processing them.

- (f) All handshake sequences should be handled by the interface quite independently from the host.

- (g) The interface need only handle text editing type terminals using either character or line mode transfers and need not attempt a full emulation of all DVR05 functions.

- (h) It should handle four terminals, all running at at least 9600 bits per second without any degradation in performance compared with running a single terminal.

- (i) User "break" interrupts should supply immediate response and should not be missed at all.

- (j) All standard line edit functions such as backspace and delete should be handled by the interface.

These objectives split naturally into two groups, those that would determine how the software handled messages, and those that would determine the hardware; while the hardware layout itself split naturally into three areas:

- (a) The standard HP flag, control and interrupt logic.

- (b) The microprocessor and its peripherals.

- (c) The interface between the HP host and the microprocessor.

Of these three hardware design areas, the first two were relatively trivial and predetermined, but the design of the interface between host and slave offered an interesting challenge.

## 4.4 The Host-Slave Interface Philosophy

The desire to have the interface pack and unpack the 16 bit data from the host meant that the upper byte of each word could not be used for control or status information and since no other signals exist in the HP I/O structure, control and status information would have to be packaged serially with the data. This meant that messages would have to have some means of synchronisation built into them. Furthermore, since up to four independent requests could be active at any time, it was essential to ensure that each request would be transferred as a discrete block with its synchronisation and identification fields, to eliminate any possible mix up of requests that could occur should request transfers be interrupted in the middle and interleaved.

In order to reduce host driver processing time to a minimum, it was necessary that the slave always be ready to accept requests from the host at any speed that the host requires. Further, when the slave has a return request available for the host, it should make this available for the host to fetch at any speed, before informing the host.

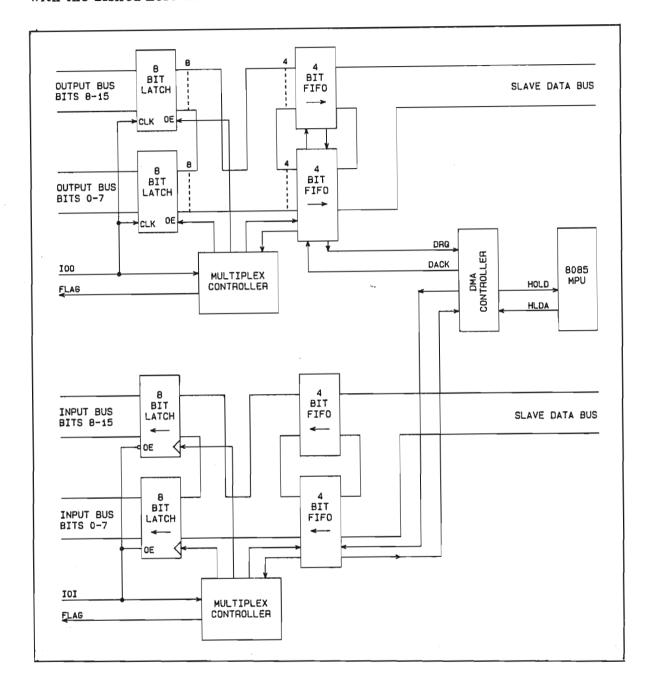

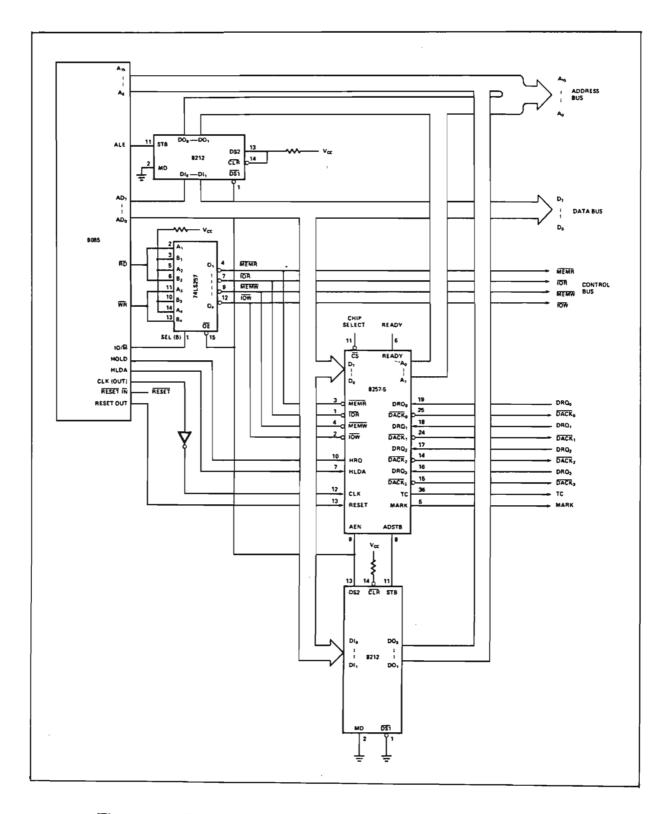

To satisfy these desires, the slave had to include a Direct Memory Access (DMA) channel capable of accepting 16 bit data from the host at any time and unpacking it into slave memory at speeds of up to 2 M bytes per second. Thus the DMA controller should at all times be primed to accept data into a free request buffer and only when a request has been fully transferred, both header and data, should the slave be interrupted by the host. The slave response time to remove the full buffer and re-prime the DMA controller with a new empty buffer should be less than the minimum time that the host can take to initiate sending a new request. To cope with the return data path, a second DMA channel capable of 2 M bytes per second transfers and packing 16 bit data words, should be primed with the return buffer before interrupting the host.

Figure 4.1 illustrates these two independent data transfer processes in pseudo code form.

```

Procedure FROM HOST;

Begin

Fetch_free buffer (Buffer_address);

Prime_dma_controller (Buffer_address, Buffer_Length);

DO Forever

Old buff address := Buffer address;

Fetch free buffer (Buffer address);

Wait for interrupt (From_Host interrupt);

Prime dma controller (Buffer_address, Buffer_Length);

Post buffer (Old buffer_address);

END

END;

Procedure TO HOST;

Begin

DO Forever

Fetch return buffer (Buffer_address);