## **BUILT-IN TESTS**

## **FOR A**

## **REAL-TIME EMBEDDED SYSTEM**

by

# PETER ANDREW OLANDER

## **VOLUME I**

Submitted in partial fulfilment of the requirements for the degree of Master of Science, in the Department of Computer Science, University of Natal

Durban

1991

#### ABSTRACT

Beneath the facade of the applications code of a well-designed real-time embedded system lies intrinsic firmware that facilitates a fast and effective means of detecting and diagnosing inevitable hardware failures. These failures can encumber the availability of a system, and, consequently, an identification of the source of the malfunction is needed. It is shown that the number of possible origins of all manner of failures is immense. As a result, fault models are contrived to encompass prevalent hardware faults. Furthermore, the complexity is reduced by determining syndromes for particular circuitry and applying test vectors at a functional block level.

Testing phases and philosophies together with standardisation policies are defined to ensure the compliance of system designers to the underlying principles of evaluating system integrity. The three testing phases of power-on self tests at system start up, on-line health monitoring and off-line diagnostics are designed to ensure that the inherent test firmware remains inconspicuous during normal applications. The prominence of the code is, however, apparent on the detection or diagnosis of a hardware failure.

The authenticity of the theoretical models, standardisation policies and built-in test philosophies are illustrated by means of their application to an intricate real-time system. The architecture and the software design implementing the idealogies are described extensively. Standardisation policies, enhanced by the proposition of generic tests for common core components, are advocated at all hierarchical levels.

The presentation of the integration of the hardware and software are aimed at portraying the moderately complex nature of the task of generating a set of built-in tests for a real-time embedded system. In spite of generic policies, the intricacies of the architecture are found to have a direct influence on software design decisions. It is thus concluded that the diagnostic objectives of the user requirements specification be lucidly expressed by both operational and maintenance personnel for all testing phases. Disparity may exist between the system designer and the end user in the understanding of the requirements specification defining the objectives of the diagnosis. It is thus essential for complete collaboration between the two parties throughout the development life cycle, but especially during the preliminary design phase. Thereafter, the designer would be able to decide on the sophistication of the system testing capabilities.

## **PREFACE**

The practical work described in this thesis was carried out at UEC Projects (Pty) Ltd., Mt. Edgecombe, Natal from November 1988 to April 1990 under the management of Mr Ian Harris and the supervision of Mr Douglas Law-Brown.

These studies represent original work by the author and have not been submitted in any form to another University. Where use was made of the work of others it has been duly acknowledged in the text.

## **ACKNOWLEDGEMENTS**

The author is indebted to the management of UEC Projects (Pty) Ltd. for providing the opportunity and privilege to submit the work contained herein. Special thanks must be extended to the staff of the Displays and Personnel Departments, but in particular to the following people:

lan Harris whose support rendered this thesis possible.

Douglas Law-Brown whose expertise as an electronics engineer and competence as a project leader proved extremely valuable and to whom a great deal of credit is due.

Michael Baudin who was responsible for the hardware design of the card cage and spent a significant amount of time and effort in explaining the intricacies of this design.

Michael Stege who laid the foundation within the department with respect to the research into built-in test policies and philosophies.

Alexander Polmans who assisted in the design and development of portions of the code.

Athol McClean and his team who were responsible for the hardware design of the console. In particular, thanks must be given to Nitin Mehta whose assistance in understanding the design and whose aid in the development of the applicable software is greatly appreciated.

Grant Robertson and colleagues at the Personnel Department who arranged the financing through the UEC Projects (Pty) Ltd. Study Assistance Scheme.

In addition, thanks must be bestowed upon Professor Alan Sartori-Angus of the Computer Science Department, University of Natal, Durban who supervised the writing of this thesis.

## LIST OF CONTENTS

| 1 INTRODUCTION                                      | 1  |

|-----------------------------------------------------|----|

| 1.1 SCOPE                                           | 1  |

| 1.2 PREVIOUS STUDIES IN THE FIELD OF BUILT-IN TESTS | 3  |

| 1.3 OBJECTIVES                                      | 7  |

| 2 THEORY                                            | 8  |

| 2.1 INTRODUCTION                                    | 8  |

| 2.2 FAILURE MODES                                   | 8  |

| 2.3 PHYSICAL COMPONENT FAILURES                     | 9  |

| 2.3.1 Malfunctioning manufactured components        | 9  |

| 2.3.2 Malfunctioning operational components         | 10 |

| 2.4 CIRCUIT FAILURES                                | 11 |

| 2.5 FAULT MODELLING                                 | 11 |

| 2.6 TESTING METHODOLOGIES                           | 13 |

| 2.6.1 Functional level testing                      | 14 |

| 2.6.2 Random testing                                | 20 |

| 2.7 SUMMARY                                         | 21 |

| 3 PHILOSOPHIES                                      | 23 |

| 3.1 INTRODUCTION                                    | 23 |

| 3.2 BUILT-IN TEST PHILOSOPHY                        | 23 |

| 3.2.1 Power On Self Test (POST)                     | 24 |

| 3.2.2 On-line diagnostics and health monitoring     | 26 |

| 3.2.3 Off-line diagnostics                          | 27 |

| 3.3 STANDARDISATION PHILOSOPHY                      | 28 |

| 3.3.1 System level standardisation                  | 29 |

| 3.3.2 Component level standardisation               | 31 |

| 3.3.2.1 Test generation for microprocessors         | 32 |

| 3.3.2.2 Test generation for ROM                     | 36 |

| 3.3.2.3 Test generation for RAM                     | 38 |

| 3.4 SUMMARY                                         | 41 |

|                                               | ٧  |  |  |  |

|-----------------------------------------------|----|--|--|--|

| 4 A REAL-TIME EMBEDDED SYSTEM                 | 42 |  |  |  |

| 4.1 INTRODUCTION                              | 42 |  |  |  |

| 4.2 THE CONSOLE                               |    |  |  |  |

| 4.3 THE CARD CAGES                            | 47 |  |  |  |

| 4.4 THE MAIN APPLICATIONS PROCESSOR CARD CAGE | 49 |  |  |  |

| 4.4.1 Main system bus and termination         | 49 |  |  |  |

| 4.4.2 Local bus extension                     | 51 |  |  |  |

| 4.4.3 The CPU card                            | 51 |  |  |  |

| 4.4.3.1 The microprocessor                    | 51 |  |  |  |

| 4.4.3.2 Clock generation and reset circuitry  | 54 |  |  |  |

| 4.4.3.3 Numeric coprocessor                   | 55 |  |  |  |

| 4.4.3.4 On-board memory                       | 55 |  |  |  |

| 4.4.3.5 Serial I/O interface                  | 55 |  |  |  |

| 4.4.3.6 Timers                                | 56 |  |  |  |

| 4.4.3.7 Interrupt controllers                 | 57 |  |  |  |

| 4.4.3.8 Diagnostic status latch               | 58 |  |  |  |

| 4.4.3.9 Time-out circuitry                    | 58 |  |  |  |

| 4.4.4 The EPROM/RAM card                      | 59 |  |  |  |

| 4.4.5 The System Data Bus Controller card     | 60 |  |  |  |

| 4.4.6 Bus terminator unit                     | 61 |  |  |  |

| 4.4.7 Dynamic RAM card                        | 62 |  |  |  |

| 4.4.8 Applications processor interface card   | 64 |  |  |  |

| 4.4.9 Serial communications to Multibus card  | 66 |  |  |  |

| 4.4.10 Graphics interface modules             | 67 |  |  |  |

| 4.4.11 Mass storage controller card           | 68 |  |  |  |

| 4.5 SUMMARY                                   | 70 |  |  |  |

|                                                        | Vİ |

|--------------------------------------------------------|----|

| 5 SOFTWARE DEVELOPMENT                                 | 71 |

| 5.1 INTRODUCTION                                       | 71 |

| 5.2 SYSTEM LEVEL STANDARDISATION                       | 72 |

| 5.3 SUBSYSTEM LEVEL STANDARDISATION                    | 74 |

| 5.3.1 Standardising the CPU cards                      | 74 |

| 5.3.2 Standardising the EPROM/RAM cards                | 75 |

| 5.3.3 Standardising the graphics interface modules     | 75 |

| 5.4 DESIGNING THE STANDARDISED CODE                    | 77 |

| 5.4.1 Detection of a "warm start"                      | 79 |

| 5.4.2 Testing of on-board peripheral chips             | 80 |

| 5.4.3 Testing the remaining standard computing segment | 82 |

| 5.5 DESIGNING THE SUBSYSTEM-SPECIFIC CODE              | 85 |

| 5.6 APPLICATIONS CONSOLE FUNCTIONAL DEMONSTRATIONS     | 92 |

| 5.7 SUMMARY                                            | 93 |

|                                                        |    |

| 6 CONCLUSION                                           | 94 |

|                                                        |    |

| 7 REFERENCES                                           | 97 |

|                                                  | vii         |

|--------------------------------------------------|-------------|

| APPENDICES                                       |             |

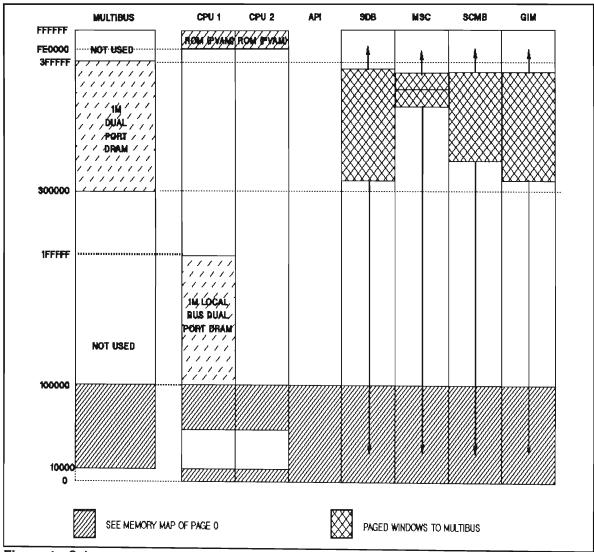

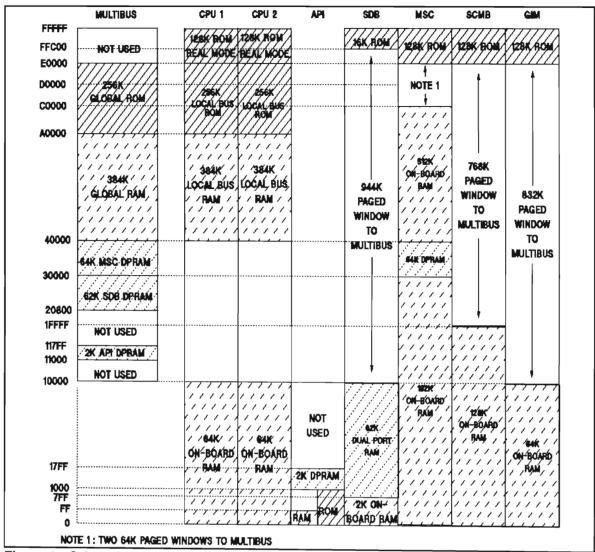

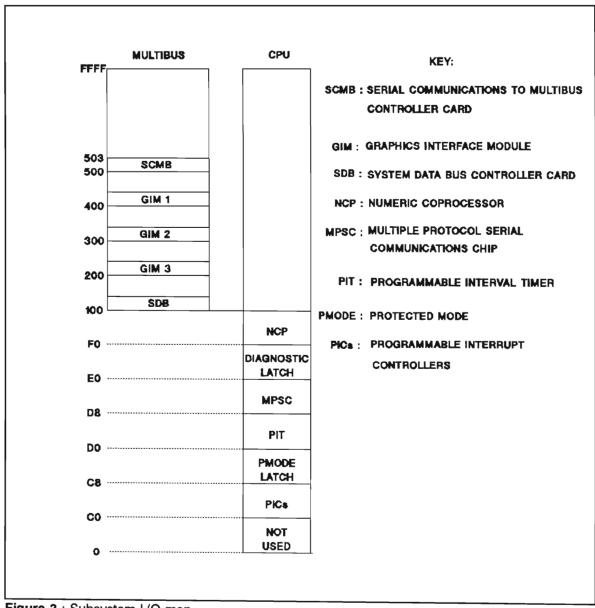

| APPENDIX A : SYSTEM MAPS                         | <b>A</b> -1 |

| APPENDIX B : STANDARDISED CODE LISTINGS          | B-1         |

| APPENDIX C : SUBSYSTEM-SPECIFIC CODE LISTINGS    | C-1         |

| APPENDIX D : CREATION OF THE EPROMS              | D-1         |

| APPENDIX E : OPERATIONAL DEMONSTRATION PROCEDURE | E-1         |

## **LIST OF TABLES**

| Table I    | : Analysis of the output function of an OR gate with typical stuck-at faults | 13 |

|------------|------------------------------------------------------------------------------|----|

| Table II   | : Fault table for a typical functional block                                 | 18 |

| Table III  | : Combined fault table for a typical functional block                        | 18 |

| Table III  | : Sample set of micro-orders for a typical microprocessor                    | 33 |

| Table IV   | : Test algorithm to detect faults in a typical microprocessor                | 35 |

| Table V    | : Core instruction set test procedure                                        | 36 |

| Table VI   | : Generic ROM checksum algorithm                                             | 37 |

| Table VII  | : Generic system RAM test algorithm                                          | 39 |

| Table VIII | : Address generator algorithm for generic system RAM tests                   | 40 |

| Table IX   | : Generation of addresses to check the validity of the address lines         | 40 |

| Table X    | : Firmware resident system description                                       | 72 |

| Table XI   | : Standardised code interpretation of the system description                 | 73 |

| Table XII  | : Dynamic allocation of graphics interface modules                           | 76 |

| Table XIII | : Main initialisation routine of the standardised code                       | 77 |

| Table XIV  | : Fault-pattern-test-pattern event space for the CPU card peripheral chips   | 81 |

| Table XV   | : Off-board access fault-pattern-test-pattern event space                    | 83 |

## LIST OF FIGURES

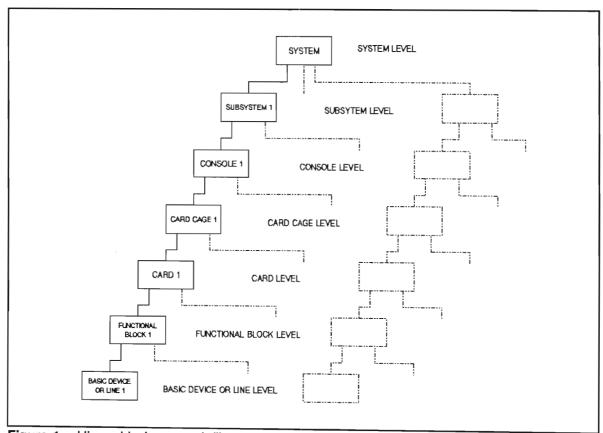

| Figure 1: Hierarchical approach illustrating the functional block concept.       | 15 |

|----------------------------------------------------------------------------------|----|

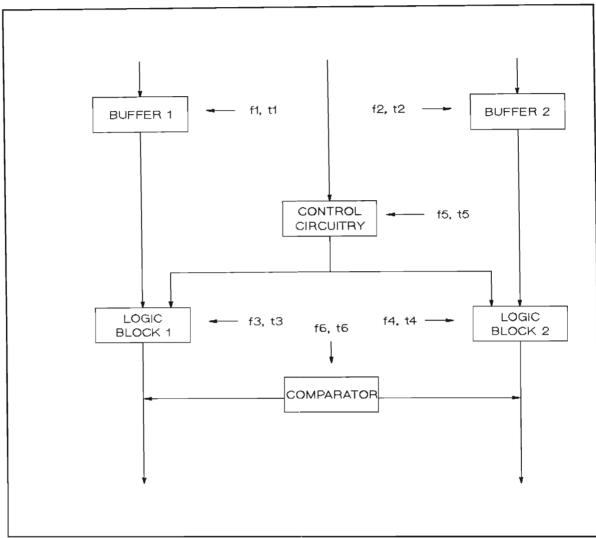

| Figure 2 : Typical functional block                                              | 17 |

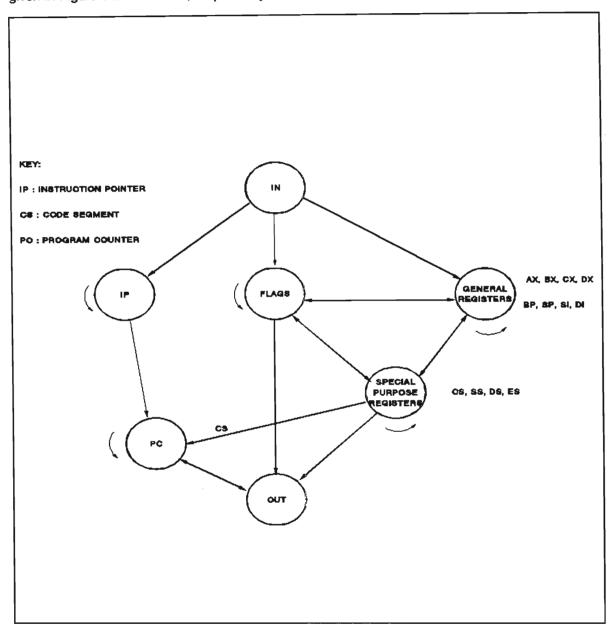

| Figure 3 : Data transfer graph representing the Intel 8086 microprocessor family | 33 |

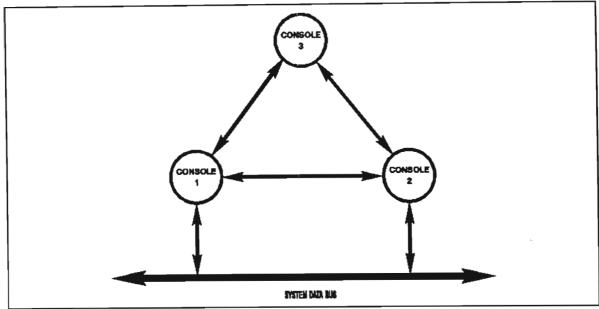

| Figure 4 : Real-time system overall view                                         | 42 |

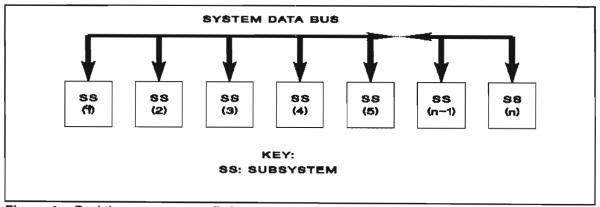

| Figure 5 : Subsystem block diagram                                               | 43 |

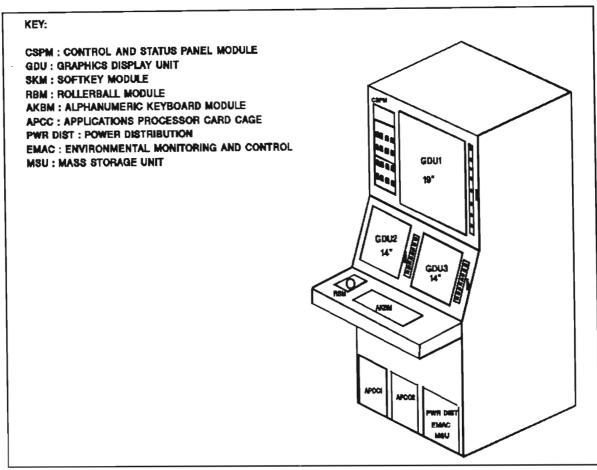

| Figure 6 : Pictorial view of the console                                         | 44 |

| Figure 7 : Status and control panel                                              | 45 |

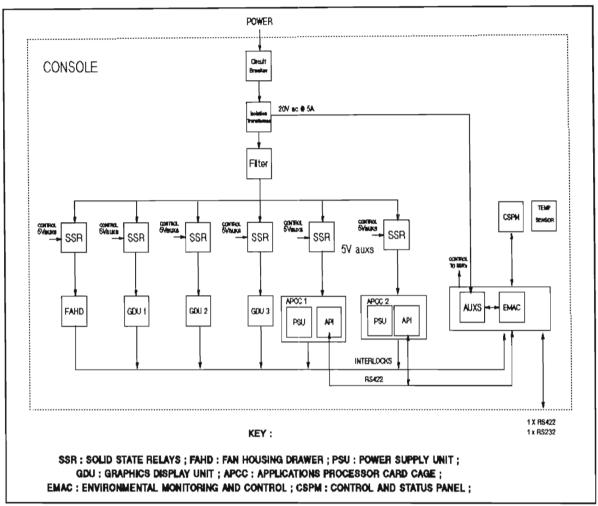

| Figure 8 : Power routing and environmental monitoring and control                | 46 |

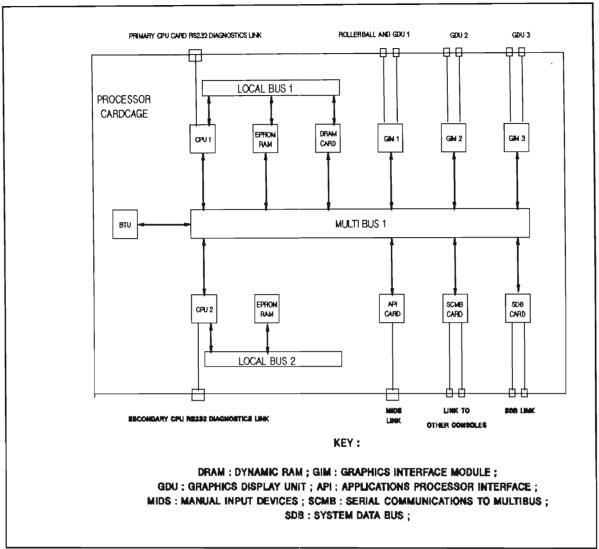

| Figure 9 : Processor card cage layout                                            | 48 |

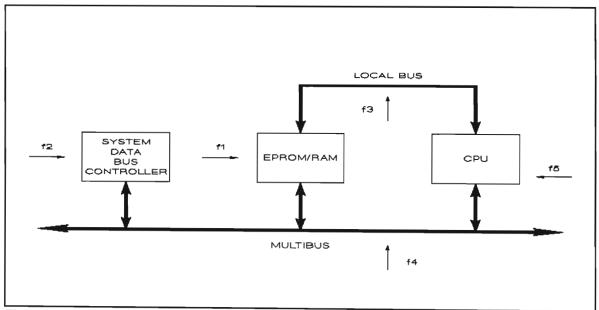

| Figure 10 : Processor card cage interconnection diagram                          | 50 |

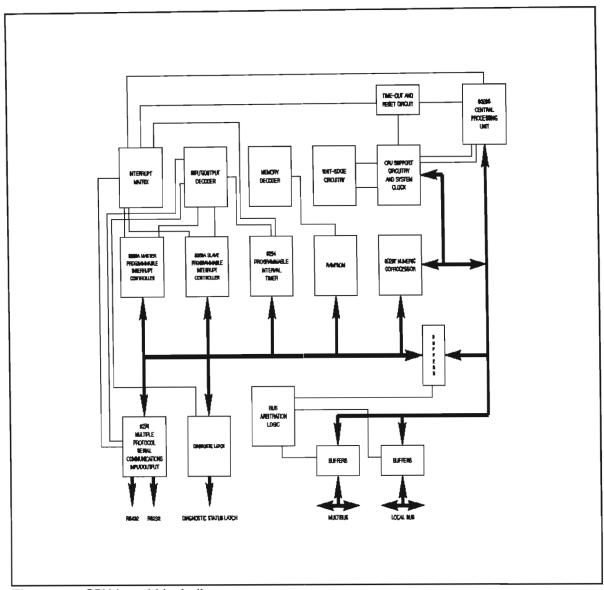

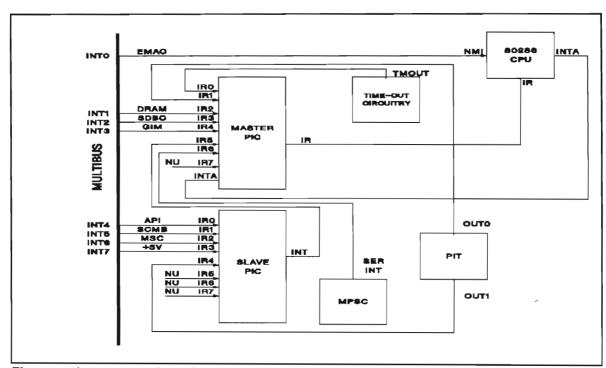

| Figure 11 : CPU board block diagram                                              | 52 |

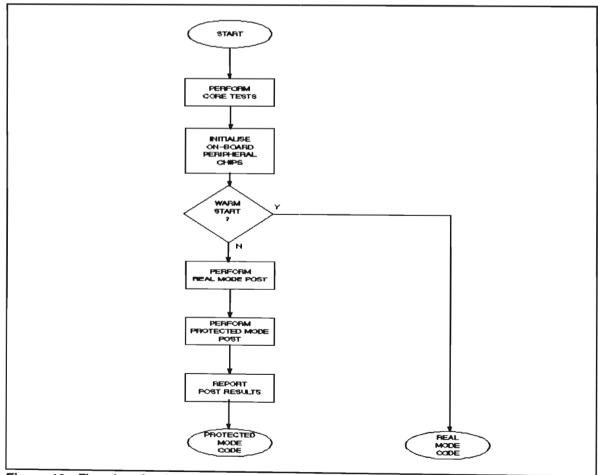

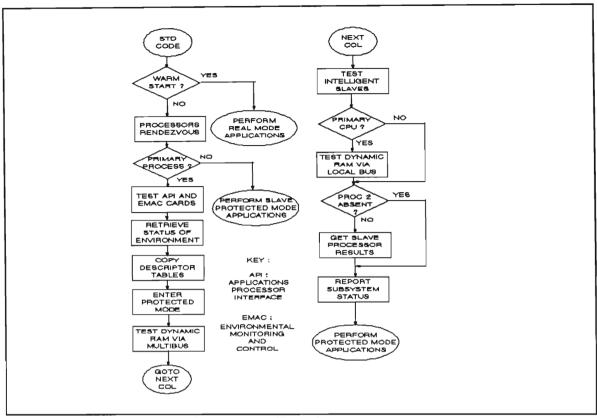

| Figure 12 : Flowchart for the main applications process                          | 71 |

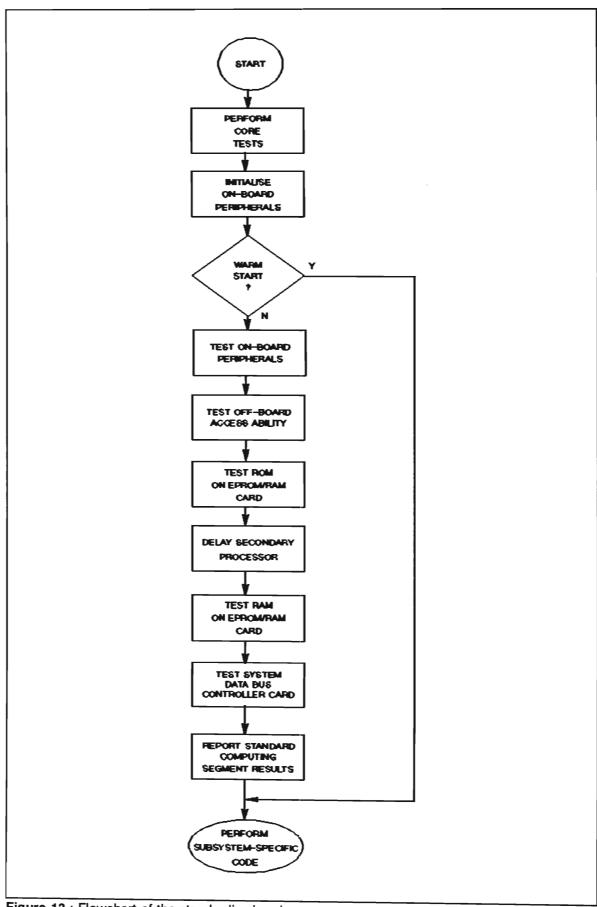

| Figure 13 : Flowchart of the standardised code                                   | 78 |

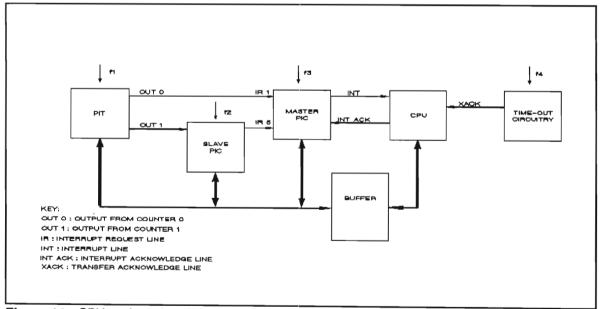

| Figure 14 : CPU on-board peripheral chips interaction diagram                    | 80 |

| Figure 15 : Standard computing segment functional block                          | 82 |

| Figure 16 : Flowchart of the subsystem-specific code                             | 86 |

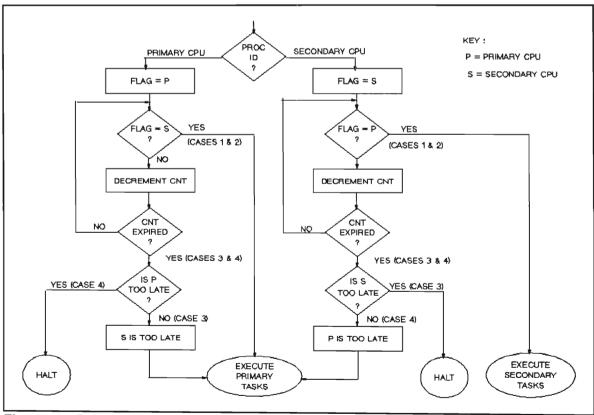

| Figure 17 : Dual processor task allocation flowchart                             | 86 |

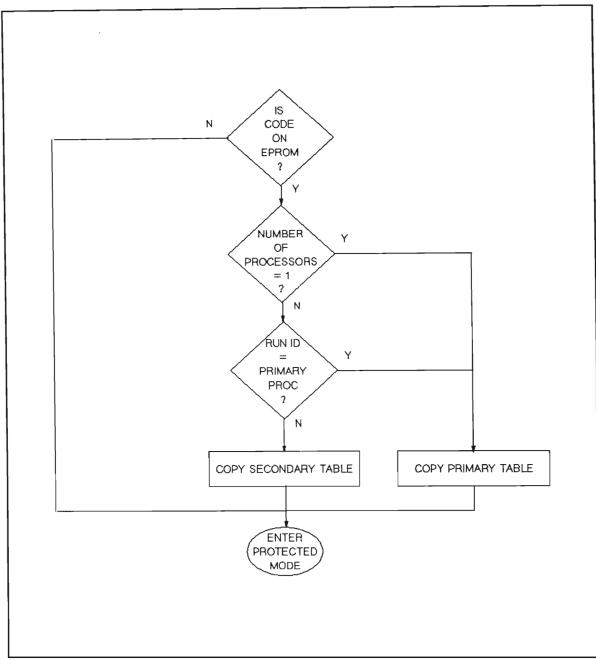

| Figure 18 : Flowchart to create RAM based descriptor tables                      | 90 |

### LIST OF SYMBOLS

AKBM Alphanumeric Keyboard Module

ALU Arithmetic Logic Unit

APCC Applications Processor Card Cage

API Applications Processor Interface

BCD Binary Coded Decimal

BIT Built-In Tests

BITE Built-In Test Equipment

BTU Bus Terminator Unit

CCITT International Consultative Committee for Telegraphs and Telephones

CPU Central Processing Unit

CRC Cyclic Redundancy Code

CS Code Segment

CSPM Control and Status Panel Module

DRAM Dynamic Random Access Memory

EMAC Environmental Monitoring and Control

EPROM Electrically Programmable Read Only Memory

FAHD Fan Housing Drawer

FET Field Effect Transistor

FTMP Fault Tolerant Microprocessor

GDU Graphics Display Unit

GIM Graphics Interface Module

GKS Graphics Kernel System

HDLC High-Level Data Link Control

IP Instruction Pointer

LED Light Emitting Diode

MIDS Manual Input Devices

MPSC Multi-Protocol Serial Communications Chip

MSCC Mass Storage Controller Card

MSU Mass Storage Unit

PIC Programmable Interrupt Controller

PIT Programmable Interval Timer

POST Power-On Self Test

PSU Power Supply Unit

PVAM Protected Virtual Address Mode

RAM Random Access Memory

RBM Rollerball Module

ROM Read Only Memory

SCMB Serial Communications to Multibus

SCSI Small Computer Systems Interface

SDB System Data Bus

SIFT Software-Implemented Fault Tolerance

SKM Softkey Module

SS Subsystem

SSR Solid State Relays

### 1 INTRODUCTION

### 1.1 SCOPE

A real-time system usually consists of two distinct parts, namely the controlled system and the controlling system. The controlled system is the hardware which makes up the system and interfaces with the environment. If the controlling system is designed to cause the controlled system to respond to any changes in this environment, then it must be able to do so within a reasonable time. The definition of "a reasonable time" depends entirely on the application of the system. For example, a thermostat controlling the temperature of a room need not react as instantaneously as a missile that is flying towards a mobile target.

In most microprocessor applications, the integrity of the controlling system is extremely important. Real-time systems must ensure a high availability and it is essential that any fault should be reported as soon as possible. Ideally, a real-time system will perform in a fault-free manner throughout its life time. In reality, however, this is rarely the case because hardware systems fail when their components degrade. During execution of the applications task of the real-time system, such failures could cause unexpected situations to arise. It is important, therefore, that any real-time system should possess total control over all possible eventualities and situations that may arise in its environment, whatever the cause. Correctness and completeness are vitally important in the design of any real-time system and suitable decisions should be made by the controller to cater for these unexpected situations. The more catering that is done for such situations, the greater the system availability factor.

The availability requirements can vary considerably from application to application. Continuous operation of computers aboard unmanned missiles or spacecraft is essential to a successful mission, since defective units cannot be repaired. In many space or military applications, the personnel are already burdened with more urgent tasks, and repairing a faulty computer system should be a quick and easy process. Most commercial computers, however, are accessible to maintenance personnel. Although it is inconvenient if a failure occurs, it is not catastrophic, and may be repaired with relatively little cost involved.

Maintenance and availability have become increasingly important in the design of real-time systems, due mainly to labour cost increases and the particular application of the systems designed. More automatic methods have had to be provided to detect and diagnose faults in modules, thus enabling less skilled technicians to repair defective units more quickly. Since hardware failures are a practical reality, methods have been devised to improve system availability. In addition to catering for

unexpected situations during the execution of the applications task, system designers are aiming to include techniques to detect execution errors. These errors may be caused by numerous factors and system designers are faced with the problem of deciding whether or not to include any form of testability in their system, and to what extent and level of sophistication.

In cases where software is an integral part of the real-time system, diagnostic routines have been written that isolate faulty hardware. The problem, however, is that errors could be caused by hardware and/or software and are often not discrete in nature. In addition, increasingly complex integrated circuits impose severe limitations with regards to accessibility, thus making the problem of test generation more and more difficult. A significant aspect of designing for testability, especially in the early planning stages, is the specification of features to be incorporated in the hardware that are designed to aid and enhance the diagnostic capabilities of the system.

The decisions made will depend ultimately on the design under consideration. The requirements specification relating to the real-time system should ideally describe the action that the system is to take for every possible situation that may arise. All requirements of the design should be carefully analyzed and appropriate decisions implemented based on these specified requirements. The generation of such a specification is probably the most difficult part of the design of any system, and generally a well-written requirements specification results in a well-designed system.

The writing of a suite of built-in tests for a computer system requires a real understanding of a large and complex set of interrelated subjects. These include such fields of study as reliability, maintainability, availability and testability. A brief discussion of factors encroaching upon these areas is necessary in order to present the applicable built-in test philosophies and concepts. A detailed discussion of the above engineering fields is, however, beyond the scope of this study, and, where necessary further references are cited.

Test philosophies presented are pertinent to the two phases of system operational testing and system maintenance testing. The tests are aimed at facilitating rapid system repair during a mission or at a repair centre. Although the theory pertinent to the generation of test patterns at the electronic level are not considered in any detail in this text, they do form a foundational basis, particularly in the study of design for testability. Some excellent references [CHANG et al, 1970; BREUER and FRIEDMAN, 1976; KRAFT and TOY, 1981] provide insight into essentially four techniques that have been used

extensively, viz. the path sensitising technique, the so-called D-algorithm, the Boolean difference method and Poage's technique. Some of these classical testing methodologies have been extended to a higher level of integrated circuitry, but the detail and complexity involved in applying the theory renders these approaches impractical, particularly during operational testing.

The theory presented works to pave the way for the implementation of practical techniques. In the writing of the text, the author has attempted to model faults that are likely to occur in a typical real-time embedded system, and to decide on a philosophy to detect such faults.

## 1.2 PREVIOUS STUDIES IN THE FIELD OF BUILT-IN TESTS

Since about 1965, test generation for logic circuits has been the subject of extensive research. It is one of the oldest areas of the study of fault-tolerant computing, a broad discipline that encompasses all aspects of sophisticated computer design. Diverse areas of fault-tolerant study range from failure mechanisms in integrated circuits to the design of robust software. The main objective of most of these studies has been to develop a systematic approach to the derivation of test procedures that will expose all manner of faults in typical logic circuits. Generally, the philosophy has been to apply a test sequence of input vectors to a particular logic circuit that causes the output(s) to differ from the normal, fault-free condition.

High reliability and availability in computer design was first achieved through so-called fault avoidance techniques, which involved computer design that used high-quality, thoroughly tested components. Sometimes, simple redundancy techniques were used to achieve limited fault tolerance. Automated recovery techniques were seldom used as there was little confidence in the hardware. The drastically increased reliability requirements, together with the increased computer speed quickly made manual recovery obsolete. For example the 1964 *Saturn V* launch computer had a reliability requirement of only 0.99 for 250 hours compared to the late 1970s FTMP (fault tolerant microprocessor) and SIFT (software-implemented fault tolerance) computers that had reliability requirements of 10-9 failures per hour over the 10 hour mission time [PRADHAN, 1986, p. xiii; SIEWIOREK, 1986, p.460].

Circuit testability, however, has to continually undergo rapid revamping to keep pace with the nearly revolutionary changes in circuit technology. While the number of components that can be supported on a chip is increasing, the chip itself is becoming susceptible to a more diverse variety of failures, ranging from internal open circuits and shorts to encapsulation and bonding failures. Research into these problems have resulted in a sounder understanding, yielding newer fault models, such as bridging faults, stuck-at faults and crosspoint faults.

Carefully formulated modelling techniques for treating fault diagnosis became firmly established in the mid-1960s [BRULE et al, 1960; JOHNSON, 1960; POAGE, 1963; CHANG, 1965; KAUTZ, 1968; KIME, 1986]. Since hardware was composed of discrete and small-scale integrated circuits, diagnosis of faults to the individual gate or line level was of particular interest. For this reason, many models dealt with stuck-at-faults in combinational networks. As the number of gates per board increased, larger line-replaceable units were created, and diagnosis to board level became an important element in the overall diagnosis philosophy. Efforts were made to design system diagnosis procedures and to analyze test data in a systematic manner [AGNEW et al, 1965; FORBES et al, 1965; HACKL and SHIRK, 1965; CHANG and THOMIS, 1967; KIME, 1986]. Early theoretical work [PREPARATA et al, 1967; RAMAMOORTHY, 1967; KIME, 1970; KIME, 1986;] and moves to employ redundancy at higher levels were motivated by these efforts of systematic approaches. Evidence of this is portrayed in dynamic redundant fault-tolerant systems that have switchable modules at board or component level, rather than at on-chip registers.

In the late 1970s, IBM introduced the so-called level-sensitive scan design technique which permits access to the internal nodes of a circuit without requiring a separate external connection for each node accessed. Since this is made possible at the cost of additional logic circuitry used primarily for testing, designing for testability has evolved to a stage of receiving far more attention as a design criterion than was initially envisaged.

Over a period of ten to fifteen years, various fault diagnosis models were developed, often appearing to be unrelated to each other. It has been shown [KIME, 1979], however, that if the concepts of "fault" and "test" are treated from a hierarchical point of view, a new model can be derived that is broad enough to encompass past diagnostic modelling efforts as well as many contemporary diagnosis practices.

Over the last few decades, several factors have influenced the computer industry and these recent trends have been the major driving forces behind the research of reliability, maintainability, availability and testability. The major factors are:

a) Systems have been exposed to harsher and more polluted environments resulting in greater fluctuations in temperatures, humidity and electromagnetic interference. Consequently, the need for more robust hardware has arisen.

- b) Due to the increasing computer market size, the majority of users have become less knowledgeable regarding the actual operation of the system. This results in systems needing to be more user-friendly and tolerant to abuse.

- c) Escalations in labour costs and decreases in hardware costs have also had an enormous effect on the industry. The greatest impact here is that it often becomes cheaper to replace faulty hardware, rather than to troubleshoot it.

- d) Systems have become larger, resulting in more components and thus the increased overall failure rate. To hold these overall failure rates at an acceptable level, the failure rates of the individual components have had to be decreased and more redundancy has had to be introduced.

- e) More competitive computer markets have resulted in manufacturers needing to supply better and more reliable products.

Most of the conducted research has arisen from the practical implementation of existing systems. These systems may be identified in terms of four gradings of availability requirements. Firstly, at the bottom of the scale are the general-purpose commercial systems, where availability is not of paramount importance. This is followed by high availability systems, where the loss of a single user is acceptable, but a system-wide crash is not. In these systems, research has shown [SIEWIOREK, 1986] that limited diagnostic fault coverage should ideally be implemented. The second-highest availability grading is that of long-life systems, such as those of the STAR and Voyager spacecraft systems. In these systems, diagnostic coverage is extensive and redundancy is high.

At the top of the scale is that of real-time control systems, where faults can jeopardise human life or have an immense economic impact. In such cases, correctness and preciseness is extremely important. The development of systems such as SIFT designed by SRI International and FTMP by Draper Labs [SIEWIOREK, 1986], both of which were designed for real-time control of aircraft have led to studies and implementation of software and hardware designs that achieve ultra-high reliability and availability. The approach taken in FTMP was to design special hardware with concurrent error detection capabilities so that incorrect data never leaves a faulty module, whereas SIFT had to mathematically prove the correctness of the system. Besides this, the SIFT project had to solve a number of challenging problems, including distributed clock synchronisation and reaching consensus on system health in the presence of faults [WENSLEY et al, 1978; SIEWIOREK, 1986, p.460-463].

In a somewhat similar manner to SIFT, the space shuttle software [COOPER and CHOW, 1976; SKLAROFF, 1976; AWST, 1981; SIEWIOREK, 1986] consists of five voters, all responsible for guidance, navigation, control, system management, payload management, pre-launch and pre-flight checks. During critical missions, four of the five computers execute redundant tasks, while the fifth performs non-critical tasks and acts as a backup to the primary system. Each computer compares its own output with the other three via software. If a disagreement is detected, the disagreeing output is signalled out, and a vote is cast regarding the disagreement. If the disagreeing unit is voted out, then the redundancy management unit removes its computer from service. A total of three failures can be tolerated. To minimise the probability of a common software bug, two independent companies were responsible for the writing of software packages that met the same requirements specification.

### 1.3 OBJECTIVES

A theoretical investigation into built-in test policies and philosophies and the illustration of the practical implementation of these techniques provides useful experience for the design of built-in tests for future systems. The objectives in presenting the material contained herein are:

- (a) to provide a base for a general understanding of relevant built-in test policies

- (b) to investigate the built-in test requirements for a real-time embedded system

- (c) to illustrate that features designed to aid and enhance the diagnostic capabilities of a system should be specified during the preliminary design phases of the development cycle

- (d) to show that the development of a comprehensive built-in test philosophy enables the coherent development of the built-in test capabilities

- (e) to provide an example of the integration and practical implementation of the researched principles during the development of a typical real-time embedded system

- (f) to illustrate the complexity involved in the generation of a set of built-in tests for a typical hardware system

- (g) to demonstrate the feasibility of generating a practical set of tests that are both comprehensive and unobtrusive during normal operation, whilst simultaneously allowing a high degree of availability to be maintained

- (h) to show the attaining of the built-in test requirements by means of fault simulation on the real-time embedded system

The concepts presented in this material may be extended quite readily to the design of various types of small computers that have different architectures, special-purpose digital controllers or large-scale processors designed with high availability features. In particular, the text has been written as a design guideline for the practising electronic engineer or computer scientist developing embedded tests for a small computer system.

### 2 THEORY

#### 2.1 INTRODUCTION

This chapter outlines some of the theoretical aspects pertaining to hardware failures and the corresponding faults that these failures may cause. Specifically discussed are some of the reasons why hardware failure is a practical reality. The text includes an overview of the basic theoretical issues relating to the modelling of faults together with techniques applicable to software tests on hardware.

### 2.2 FAILURE MODES

Typically in the development of a large project, the system will experience considerable reliability growth. During early development, the achieved reliability of a new design is much lower than its final predicted reliability because of initial engineering deficiencies as well as manufacturing flaws [ANDERSON et al, 1982, p. 28:12]. The reliability growth of a hardware item is a test-fail-correct process with the aim of designing the hardware to realise its full reliability potential. Engineers will analyze hardware in a manner aimed at identifying basic faults at the part level and determining their effects at higher levels of assembly. This iterative documented process, known as failure mode effects and corrective actions, can be performed with actual failure modes from field data, hypothesised failure modes derived from design analyses, reliability-prediction activities or experience of how parts fail.

In addition to providing insight into failure cause-and-effect relationships, the failure mode and effects analysis provides the disciplined method for proceeding part by part through the system to assess failure consequences. Failure modes are analytically induced into each component and the severity and frequency of occurrence are evaluated and noted. The entire process of introducing failure modes into a system causes a snowball effect, since the resulting failure effect becomes, in essence, the failure mode that affects the next higher level. If the process is iterated for all failure modes, the ultimate effect may be established at system level. In this fault-tree analysis, failure at the root may thus be caused by a failure mode at any one of several leaf nodes.

The use of computational techniques to analyze basic faults, determine failure-mode probabilities and establish criticalities allows for the formulation of corrective suggestions, which, when implemented will eliminate or minimise critical faults. This corrective action is most effective during preliminary system design and after final design before full-scale production is under way. In order to achieve a high system reliability and availability, it is essential that the hardware design engineer, the diagnostic software engineer and the reliability engineer work together to identify and eliminate all potential failure modes.

## 2.3 PHYSICAL COMPONENT FAILURES

Part failures can be broadly divided into two classes, namely malfunctioning manufactured components and malfunctioning operational components. Although most assembly lines do have quality control checks on delivered items, some malfunctioning parts will inevitably escape initial detection. The classes are therefore not exclusive, since faulty manufactured components may only fail during the mission.

Manufacturers are very concerned, however, about reducing the incidence of fabrication-related failures in order to increase the yield and thus lower the cost of integrated circuits. For example, recently high-density memory chips are being manufactured with redundant elements that can be switched into operation to replace faulty elements by the use of current pulses or a laser beam [ABBOTT, 1981; SUD, 1981; ABRAHAM and AGARWAL, 1986, p. 6].

## 2.3.1 Malfunctioning manufactured components

Manufacturing defects can be caused by several factors, such as defects in oxide pinholes, photoresist or etching defects, conductive debris, scratches, weak bonds or partially cracked chips or ceramics. Some causes of manufacturing defects are cited below [ABRAHAM and AGARWAL, 1986, p. 6-7]:

- a) Defects in the crystalline structure of silicon cause devices in the region of the defect to be faulty.

- b) Improper doping profiles can result in devices with unwanted characteristics, which in turn can result in intermittent or permanent faulty behaviour.

- c) Poor encapsulation can result in the penetration of moisture into the package, resulting in long-term corrosion-related failures.

- d) Impurities in the packaging could result in low-level radiation which can lead to run-time data on the chip being lost.

- e) Aluminum metal can be subject to corrosion, resulting in long-term failures.

- f) High current densities in thin wires can result in metal migration, eventually resulting in a break in the wire.

- g) Formation of spurious "whiskers" can lead to resistive shorts.

- h) Migration of alkali ions can cause a shift in the thresholds of transistors, which will manifest themselves as intermittent failures, eventually becoming permanent.

- i) High field intensities can impart energy to electrons, causing these "hot" electrons to move into and be trapped in the gate oxide in MOS transistors, also causing shifts in threshold voltages.

- j) The defects may also be caused by assembly operations or even an assembly line worker's learning, motivation, fatigue or negligence.

Failures of integrated circuits due to electrostatic discharge during assembly operations have become more significant as technological advances have produced devices with smaller geometries and thinner dielectrics. Studies [ANDERSON et al, 1982] have shown that CMOS and linear integrated circuits are the most sensitive to improper handling which can result in input gate breakdown caused by static electricity.

## 2.3.2 Malfunctioning operational components

Operational malfunctions occur as a result of system operation, where simply the old age of the part causes the physical or chemical structure of electron devices or components to deteriorate. Systems may also be called upon to operate beyond their design capabilities due to an unusual mission requirement, which could be detrimental to the functioning of the system and cause part failure.

Degradation in inherent reliability can also occur as a result of excessive handling from frequent preventative maintenance or poor corrective maintenance activities. The replacement of analog by digital circuits, aims at reducing the requirement for frequent preventative maintenance, while the substitution of faulty hardware in a real-time system at a board level tends to reduce poor corrective maintenance activities.

#### 2.4 CIRCUIT FAILURES

Circuit faults may be classified as logical or parametric. A logical fault is one that causes the logic function of a circuit element or an input signal to be changed by some other logic function, whereas a parametric fault alters the magnitude of a circuit parameter, causing a change in some factor such as circuit speed, current or voltage [FUJIWARA, 1985, p. 8].

It has been established [ANDERSON <u>et al</u>, 1982] that semiconductor circuit malfunctions generally arise from two sources, namely transient circuit disturbances and component burnout. The transient spike or "hazard" is more common because it occurs at much lower energy levels.

Malfunctions associated with timing are due mainly to circuit delays. Although all inputs to asynchronous circuitry should be constrained to change only when the memory elements are in stable conditions, delay faults could affect the timing operation of the circuit. Since an asynchronous circuit is assumed to have a finite, positive delay, bad circuit design can result in the generation of both transient spikes or race conditions. If either is input to a flip-flop or Schmitt trigger, or interpreted as a control signal, this may result in an incorrect state.

### 2.5 FAULT MODELLING

Problems arise when attempts are made to formalise and classify all manner of faults that are likely to occur in a set of electronic devices. The discussion above has shown that several types of failures can occur both during the manufacture and operational life-time of a component. The types of failures that are seen also vary with technology. For example, bipolar circuits usually have a higher device power dissipation, are more likely to exhibit hot spots and temperature-related problems, and are also prone to metal migration problems because of high current densities.

As technology changes and existing problems are solved, new problems arise, thus making it impossible to list all possible failures that can be used to derive tests for circuits. Another problem with obtaining information pertaining to long-term failures is the fact that the upgrade rate for integrated circuits is so high that many new devices have not been in use for very long.

It can be seen that a practical approach to testing should avoid working directly with physical failures, due to their large number and complex nature. Generally speaking, people are not interested in the detail to basic device level of the cause of a failure, and some level of abstraction is needed. A physical failure that changes the function of a circuit can be detected by applying an appropriate sequence of tests to the input and monitoring the output for errors. When tested with fault models

of this nature, many different physical failures may cause the same error. If, however, the fault model accurately describes all the physical failures of interest, then it is only necessary to derive tests that detect all the faults of the fault model. In this way, the number of primitive entities to be considered in deriving a test is reduced considerably. Quite often, the details of the physical failures are unknown or are too numerous to consider and a fault model can be hypothesised to cover most of the possible failures. Another advantage of this approach is that the tests may become generic and totally independent of the current technology.

When designing hardware or software with test capabilities in mind, it is necessary to consider what is most likely to fail. To provide an answer to this question is, of course, not trivial. The types of faults that are known to occur from past experiences need to be considered and applied to the various functional blocks. For example, an n-p-n transistor implementing an inverter with an open base or collector would cause the output on the collector to be permanently high or stuck-at-1. Conversely, a short-circuit between the collector and the emitter would cause the output to be permanently low or stuck-at-0.

Short-circuits (known as bridging faults) generally result in stuck-at-faults. These faults are usually the most common, but it has been revealed [FUJIWARA, 1985, p. 8-12] (i) how a CMOS two-input NAND gate with p-MOS and n-MOS FETs can cause combinational circuits to become sequential and (ii) how extra or missing devices in programmable array logic circuits at a particular crosspoint in the array can upset the logical output. These may or may not be able to be modelled by the classical stuck-at-fault.

In determining a set of input vectors for a nonredundant logic circuit with n inputs, it is possible to adopt a brute force philosophy by applying all  $2^n$  possible input combinations to the circuit. As n becomes large, however, this approach becomes extremely inefficient. Examination of the physical behaviour of the circuit reveals a smaller set of tests which will be sufficient to detect all likely occurring faults. As an example, consider a two-input OR gate with output function F = A + B. The analysis of typical stuck-at faults for input A is depicted in Table I. As can be seen from this illustration, faults on input A will only be detected when all inputs are zero and when A is high and the other input is low.

Table I : Analysis of the output function of a two-input OR gate with typical stuck-at faults.

| Inputs<br><i>AB</i> | Input A<br>stuck-at | Expected output | Actual output | Fault<br>detected |

|---------------------|---------------------|-----------------|---------------|-------------------|

| 00                  | 0                   | 0               | 0             | No                |

| 00                  | 1                   | 0               | 1             | Yes               |

| 01                  | 0                   | 1               | 1             | No                |

| 01                  | 1                   | 1               | 1             | No                |

| 10                  | 0                   | 1               | 0             | Yes               |

| 10                  | 1                   | 1               | 1             | No                |

| 11                  | 0                   | 1               | 1             | No                |

| 11                  | 1                   | 1               | 1             | No                |

Thus, for faults on a two-input OR gate, the input test vectors are:

(i) A = 0, B = 0: tests all stuck-at-1 faults

(ii) A = 0, B = 1: tests input B for stuck-at-0

(iii) A = 1, B = 0: tests input A for stuck-at-0

By induction, for an n input OR gate the input vectors will be (i) all inputs low and (ii) a "walking" one on each respective input line with the rest of the (n - 1) inputs low. Similarly, for an n input AND gate the input vectors will be the complement of the test vectors used in checking the OR gate. The test for a NOT gate is trivial, because this is simply the complement of the input.

## 2.6 TESTING METHODOLOGIES

There are basically three techniques that can be applied to the generation of a test set for circuitry, namely structural level test generation, functional level test generation and random testing. Firstly, the structural level test generation aims at testing the circuitry mainly during the fabrication process. Each line of a module is tested for classical faults at a electronic level. This method is therefore not applicable to the operational testing of an embedded system and is not considered any further here. Functional level test generation and random testing methodologies are, on the other hand, applicable to the design under consideration and are discussed below.

## 2.6.1 Functional level testing

Since all logic circuits may be decomposed into NOT, AND or OR functions, it is possible to test for the classical stuck-at-faults. For complex systems where the majority of the circuitry is comprised of integrated circuits, the process of decomposing all circuitry into these basic functions would be an impossible task. In other complex systems where no integrated circuitry exists, the decomposition may still be far too difficult to achieve. A higher level of testing needs to be established and agreed upon. Ideally, the implementation of built-in tests only need to resolve circuit behaviour to functional block level. Although many of the internal gates of functional blocks are not directly influenced by variations in I/O signals, these would be tested indirectly by the varying I/O signals of juxtaposed gates. Thus, if a functional block is tested with sufficient input signals to test all possible functional operations of that block and the output corresponds to what is expected for each input, then the functional block is operating in a fault-free manner. This approach greatly reduces the complexity of the task of writing a suite of built-in tests for any system. The objective of testing complete system integrity is still achieved, however, provided that the built-in tests check every possible functional operation of each block.

The functional testing approach is often the only method by which some circuits are tested. It is very difficult to grade the quality or fault coverage of these tests, however, and it has been observed [ABRAHAM and AGARWAL, 1986, p. 50] that in many cases these tests do not detect existing failures. This is because the faults could cause the system to apparently perform its function correctly, while simultaneously performing other spurious tasks. As an example, if a multiplexer contains a stuck-at or bridging fault, an incorrect data line (in addition to a correct one) could be selected. The performance of these spurious tasks are undesirable and it is important that the test procedure detect such side effects.

Two rules have been laid down [ABRAHAM and AGARWAL, 1986, p. 50] that should be followed when using a functional block testing approach which will detect the most likely physical failures, viz.

- (a) A test must verify that no unintended function was performed together with the intended function.

- (b) Information about the structure and the faulty behaviour of the system in addition to the functional information should be available in order to generate tests of a reasonable length for a complex system.

Unfortunately, for a complex system, the number of possible erroneous functions to be checked is extremely large, and the test would be both prohibitive and complicated. If no information is available regarding the structure or faulty behaviour, it becomes imperative to reduce the size and complexity of the test, which places the amount of fault coverage in jeopardy.

For the reasons discussed, the term "functional-level test generation" is defined to mean an approach whereby a higher level fault model is first derived for the system under test to include the most likely circuit failures. Test sequences are then derived to detect faults in this fault model. Structural information about the system is utilized to reduce the size of the test set when this theory is applied to the system.

The functional-level test generation is illustrated in the hierarchy of Figure 1. Tests can be generated in relation to any level of the hierarchy, provided that the test detects a significant portion of the faults potentially present at the lowest level in the hierarchy. Test result details can help to more clearly separate faulty components for a variety of lower-level faults that can occur. This detail can be lost, however, in moving up a level in the hierarchy, so careful thought must be given by the diagnostic designer in deciding on circuit subdivisions.

Figure 1: Hierarchical approach illustrating the functional block concept.

The fault model for the functional block consists of a fault set  $FS = \{f_1, f_2, ..., f_m\}$ , for m possible faults, where  $f_i$  is present if the ith unit is faulty [KIME, 1986]. To simplify the model, an assumption is made that only one fault is present at any given time, and that this fault is "solid" (i.e. determinate). The fault pattern set is therefore  $F = \{F_0, F_1, ..., F_m\}$ , where  $F_0 = 0$  and  $F_1 = \{f_1\}$ ,  $F_2 = \{f_2\}$ , etc.

Tests are modelled from the same hierarchical viewpoint as faults. The levels in the test hierarchy, to some degree, coincide with those of the fault hierarchy. A test set for a fault set FS is denoted by  $TS = \{t_1, t_2, ..., t_n\}$ , where  $t_i$  is test i for a set of n tests. A test pattern  $TP = \{T_0, T_1, ..., T_p\}$  (where  $p \le n$ ) is defined as a subset of TS consisting of the set of all tests that failed on application of test set TS. The set of all test patterns that are expected to occur is  $T = \{T_0, T_1, ..., T_n\}$ .

A vector notation may be used to describe test patterns. In this notation,  $T_v = \{t_1, t_2, ..., t_n\}$ , where  $t_i = 1$  if the *i*th test fails, and  $t_i = 0$  if the *i*th test passes. For example, in the test pattern  $T_{eq} = (0,1,0,1)$ , test  $t_1$  and test  $t_3$  have passed, while tests  $t_2$  and  $t_4$  have failed.

Figure 2 shows an example of a functional block, consisting of duplicated computational blocks whose outputs (OUT<sub>1</sub> from the first logic block and OUT<sub>2</sub> from the second logic block) are compared by a self-checking equality comparator. Data from an external source is buffered and the control circuitry provides control signals for the computational blocks. The equality comparator, which is used for concurrent fault detection during normal operation, is used here to compare the outputs of the computational blocks under the applied test. The tests to be considered are software tests applied by hardware external to the functional block.

The fault and test patterns are related to each other via a fault-pattern-test-pattern event space. To illustrate the relationship, suppose that in Figure 2 the fault pattern set F is restricted to consist of a good functional block plus functional blocks containing exactly one of the faults of the fault set  $FS = \{f_1, f_2, ..., f_6\}$ , i.e.  $F = \{F_0, F_1, ..., F_6\}$ .

The test set is  $TS = \{t_1, t_2, ..., t_6\}$ , where each  $t_i$  corresponds to testing for each  $f_i$ . Determining the associated test patterns is achieved by examining the behaviour of each test for each fault pattern. The event space is then formulated as per Table II and Table III. As an example, assume that the control circuitry is faulty. On  $OUT_1$ , the results of tests  $t_1$  and  $t_3$  will be indeterminate. Similarly, the results of tests  $t_2$  and  $t_4$  on  $OUT_2$  will also be indeterminate. Test  $t_5$  will register a failure on both outputs, while the comparator test  $t_6$  will not be affected and will consequently pass.

Figure 2: Typical functional block

Table III may be used to perform diagnosis by assembling the actual test results into a test pattern, known as a syndrome. The syndrome is then compared with each of the tabulated test patterns. If a match occurs, the fault pattern corresponding to the test pattern may be present. For example, if the syndrome is 111110, then the corresponding fault pattern indicates that fault  $f_5$  is present, and the syndrome has enabled the diagnosis of faulty control circuitry. However, if the syndrome is 101010, then it is indeterminate whether fault  $f_3$  (logic block 1 faulty) or fault  $f_5$  (control circuitry faulty) is present.

Table II : Fault table for a typical functional block.

| Faulty<br>circuitry               | Fault<br>pattern | Test pattern (OUT <sub>1</sub> )<br>$T_{v1} = (t_1t_3t_5t_6)$ | Test pattern (OUT <sub>2</sub> )<br>$T_{v2} = (t_2 t_4 t_5 t_6)$ |

|-----------------------------------|------------------|---------------------------------------------------------------|------------------------------------------------------------------|

| None                              | $F_0$            | 0000                                                          | 0000                                                             |

| Buffer 1                          | F <sub>1</sub>   | 1X00                                                          | 0000                                                             |

| Buffer 2                          | $F_2$            | 0000                                                          | 1X00                                                             |

| Logic Block 1                     | $F_3$            | X1X0                                                          | 0000                                                             |

| Logic Block 2                     | $F_4$            | 0000                                                          | X1X0                                                             |

| Control logic                     | F <sub>5</sub>   | XX10                                                          | XX10                                                             |

| Comparator                        | F <sub>6</sub>   | 0001                                                          | 0001                                                             |

| 0 = Test passed; 1 = Test failed; |                  |                                                               |                                                                  |

Table III: Combined fault table for a typical functional block

| Faulty<br>circuitry | Fault<br>pattern | Test pattern (OUT1 and OUT2)<br>$T_v = (t_1t_2t_3t_4t_5t_6)$ |

|---------------------|------------------|--------------------------------------------------------------|

| None                | F <sub>o</sub>   | 000000                                                       |

| Buffer 1            | F,               | 10X000                                                       |

| Buffer 2            | $F_2$            | 010X00                                                       |

| Logic Block 1       | $F_3$            | X010X0                                                       |

| Logic Block 2       | F <sub>4</sub>   | 0X01X0                                                       |

| Control logic       | F <sub>5</sub>   | XXXX10                                                       |

| Comparator          | F <sub>6</sub>   | 000001                                                       |

|                     |                  |                                                              |

$<sup>0 =</sup> Test \ passed ; 1 = Test \ failed ; X = "Indeterminate"$

X = "Indeterminate"

The syndrome for the functional block may be written as a Boolean expression from the fault table of Table III. This yields the syndrome :

$$S = f_{1} (t_{1} t_{2}' t_{4}' t_{5}' t_{6}')$$

$$+ f_{2} (t_{1}' t_{2} t_{3}' t_{5}' t_{6}')$$

$$+ f_{3} (t_{2}' t_{3} t_{4}' t_{6}')$$

$$+ f_{4} (t_{1}' t_{3}' t_{4} t_{6}')$$

$$+ f_{5} (t_{5} t_{6}')$$

$$+ f_{6} (t_{1}' t_{2}' t_{3}' t_{4}' t_{5}' t_{6})$$

[where  $t_{i}' = not (t_{i})$ ]

In order to see how this expression may be used in diagnosis, suppose that the test results are  $t_1 = 1$ ,  $t_2 = 1$ ,  $t_3 = 1$ ,  $t_4 = 1$ ,  $t_5 = 1$  and  $t_6 = 0$ . The syndrome expression yields  $S = f_5$ , indicating the control circuitry faulty. Alternatively, for test results  $t_1 = 1$ ,  $t_2 = 0$ ,  $t_3 = 1$ ,  $t_4 = 0$ ,  $t_5 = 1$  and  $t_6 = 0$ ,  $S = f_2 + f_5$ , showing that either of these faults may be present.

The theory presented above can effectively be applied to represent any fault-pattern-test-pattern event space. However, some real diagnosis problems arise in the attempt to formulate this event space, including test completeness, test invalidation, and test result information loss. A "complete" test is one that fails for exactly one fault from the set present, while passing for all absent faults [KIME, 1986, p. 587]. Therefore, a test must detect all underlying faults in the hierarchy that manifest themselves in the fault under consideration. As an example, consider buffer 1 of Figure 2. If the test t<sub>1</sub> for this buffer was designed to test for all data line stuck-at faults, and instead a bridging fault occurred between two lines, then there is a strong possibility that this fault would go undetected. Thus, if bridging faults are assumed to occur at a lower hierarchical level and the test was not designed to detect them, then the test is incomplete. In general, test completeness, although assumed in the theory presented, is difficult to achieve in practice.

Another problem is that of test invalidation. A complete test is defined to be "valid" if it always fails when one or more of the faults for which the test is complete exists, and always passes when all faults for which the test is complete are absent. What this definition is saying is that, ideally, the result of a test on one or more faults is not influenced by the presence or absence of other faults. Unfortunately due to circuitry interaction, this is usually not the case in reality.

A third diagnostic problem is that of information loss. In performing any form of diagnostics, there is a distinct trade-off between the complexity involved and the amount of information lost. As an example, suppose that two tests  $t_1$  and  $t_2$  have the same results for fault pattern  $F_1$  (00 or 11) and complementary results for fault pattern  $F_2$  (01 or 10). If this was the only method of distinguishing between the two faults and this fact was overlooked by the modeller (i.e. the test results were modelled as "don't cares" for both fault patterns), then important test result information would have been lost in the diagnostic design process.

## 2.6.2 Random testing

The studies of functional-level test generation have exposed several problems associated with the practical implementation of the theory. Another approach, which can be applied independently or together with the functional approach, is that of random testing. This is probably the simplest approach to the test generation problem. Instead of basing test vectors with specific fault models in mind, the tests are chosen independently according to some fixed probability distribution and applied to the circuit under test. The functional operation of the circuitry is considered, and a test is generated based on this functional operation. The output is then compared with an expected error-free reference vector.

Although simplifying the task of generating a suite of tests, this method immediately poses three queries, namely:

- (a) What is the number of test vectors to be randomly applied to a particular circuit?

- (b) What is the size of the fault coverage for a particular circuit?

- (c) What is the level of confidence that can be placed on the test results?

The determination of the length of the random sequence that is required to obtain a satisfactory fault coverage can entail an analysis which can be more complicated than the deterministic test generation procedure being replaced [SHEDLETSKY, 1977; ABRAHAM and AGARWAL, 1986, p. 72]. Although an analytical method of estimating fault coverage would be preferable, it has been revealed [SHEDLETSKY, 1977] that none of the techniques yet developed are capable of getting accurate fault coverage estimates without a great deal of computation. During system development it may be necessary, therefore to use fault simulation techniques to determine fault coverage.

### 2.7 SUMMARY

This chapter has provided an introductory discussion of failure modes and the physical failure of components resulting from defects during manufacturing or failure during operation. In addition, a discussion of parametric and logical circuit faults was also provided. The formalisation and classification of all manner of faults for a complex real-time embedded system was shown, however, to be impractical. It was established that a better approach to generating tests is to apply some level of abstraction to the system under test. For this reason, the discussion dealt with a hierarchical approach to fault modelling and test generation. An example was introduced in an attempt to convey the complexities involved in designing a suitable test for typical circuitry. The example illustrated that the number of input test vectors that detect a known classical fault for a particular circuit may be reduced considerably if the physical behaviour of the circuit is examined.

Three testing methodologies were introduced, namely that of structural-level test generation, functional-level test generation and random testing. The electronic level of the structural-level test generation technique rendered this method inapplicable.

A fairly lengthy discussion was presented regarding the functional-level testing methodology. Applying this technique, the designer decomposes the system under test until a functional block remains. All classical faults in this functional block then form a fault set. Under the assumption that only one fault is present at any one particular instant, the test set is generated. Each test is designed to test for a corresponding fault. Consideration is given to the logic output corresponding to the application of each test and a fault-pattern-test-pattern event space is constructed. The syndrome that enables fault diagnosis from the fault and test patterns applied to the functional block may either be determined from the fault-pattern-test-pattern event space or from the resulting Boolean expression.

Random testing, on the other hand, considers the test generation problem from a more statistical viewpoint. Tests are chosen independently according to some fixed probability distribution. A brief discussion of the advantages and disadvantages of this approach was included in the text.

Several problems associated with the testing techniques that face the diagnostic designer were described. These included test completeness, test invalidation and test result information loss. In addition, queries concerning the determination of the number of test vectors, establishing the fault coverage and determination of the level of confidence in the test results were posed.

The testing methodology applied will depend ultimately upon the system under consideration. A logical approach is to combine the theories of functional level test generation and those of random testing in order to devise non-deterministic test vectors for some cases. Although the functional test generation technique should be the main approach, some of the classical faults should also be borne in mind in designing the tests. This would enable a higher level of testing to be applied whilst simultaneously maintaining a reasonable level of confidence in the system integrity.

#### **3 PHILOSOPHIES**

## 3.1 INTRODUCTION

Up to this point, not much has been said concerning the policies and philosophies that should be adhered to throughout the development of a system with testable features. This chapter aims to introduce and describe those idealogies. The built-in test features may be divided into three modes of operation, viz. (i) Power On Self Tests at system start up, (ii) on-line diagnostics and health monitoring and (iii) off-line diagnostics. Philosophies applicable to each mode are discussed in the ensuing sections.

Standardisation policies are discussed at both system and component levels. The component level standardisation discussion presents theoretical issues and generic routines pertinent to the generation of tests for common hardware components.

#### 3.2 BUILT-IN TEST PHILOSOPHY

A real-time system must be able to provide a service that can be closely defined in terms of guaranteed minimum mean time between failures and mean time to repair. If faced with a hardware failure, the system should, if possible, provide a useful degraded service that still enables quick and easy fault diagnosis. Built-in test equipment (BITE) and built-in tests (BIT) are designed in such a manner that systems may test themselves, providing both diagnostic capabilities and a confidence check of the system. BITE is the hardware built into the circuitry that provides fault detection, whereas BIT is the fault detection or diagnostic routine that utilizes BITE and/or test sequences to facilitate the task of locating defective units.

The incorporation of BIT and BITE in system design is essential in detecting and diagnosing all manner of failure modes in both the development and applications of a real-time system. In order to maintain a high system availability during a mission, the trend in system design is to incorporate enough testability that checks the entire system integrity, whilst simultaneously not causing an excess on system overhead.

Both BITE and BIT apply a sequence of input patterns that produce erroneous responses when faults are present and then compare the responses with expected ones. In order to design a complete test sequence for a specific circuit, the test conditions must be oriented toward checking the circuit at the level of the components themselves, rather than at the level of the microinstruction set.

The existence of fault models at the various levels of a hierarchical design is useful for finding the effects of faults and deriving tests in a hierarchical fashion, treating the testing problem in much the same way as the original design problem. Principles normally associated with the design for testability theory are applicable to the test generation process in such a case. Two guidelines should be used throughout the implementation of the BIT for a real-time system. Firstly, it should be attempted to adhere as far as possible to the enhancement of controllability and observability in the division of circuits into subcircuits, since it has been established [FUJIWARA, 1985, p. 145-149] that the testability of a circuit is closely related to these two factors. Secondly, the top-down approach of "divide and conquer" should be incorporated. The system as a whole should be partitioned into smaller and smaller constituents until a functional block remains. It has been shown [FUJIWARA, 1985, p. 145] that the computer run time to generate tests is approximately proportional to the number of gates to the power of three. Thus, dividing a circuit in half, reduces the BIT task to one eighth for each of the two subcircuits.

## 3.2.1 Power On Self Test (POST)

To ensure confidence that the system will perform reliably before entering a normal operational environment, initial "sanity" tests should be performed by the resident firmware. This start-up testing serves to validate the hardware and provide the operator with advisory notifications of critical hardware failures that would prevent normal system operation. Tests should be run in a sequence that examines as much circuitry as possible as quickly as possible.

At system start up, the embedded firmware should execute diagnostics on the integrity of the real-time system in an "expanding kernel" manner, i.e. basic critical tests should be initially performed, followed by further tests based on the former results. Certain functional units should be defined to be critical, and, in the event of failure, the error should be reported, if possible, and the system halted. If a non-critical unit fails a power-on self test, it should ideally report the failure to the operator, but operation should be able to continue at the discretion of the operator.

Normally in a real-time embedded system, a single board computer is executing as master, and in the "expanding kernel" fashion this card would initially test the processor ROM and RAM followed by other on-board peripheral chips. The basic idea is to start evaluating a small section of the processor card and to expand the diagnostic process to include more and more hardware with each succeeding step until the entire card has been completely tested. If no critical faults have been detected, off-board tests should be performed in a logical order. Ideally, these off-board tests should be to poll the presence status of the various cards in the system, followed by integrity tests based upon the presence results. Intelligent units should simultaneously perform their own POST and report their

results to global or dual ported RAM locations. These locations, together with units equipped with BITE circuitry that can report aspects of their operational status may then be interrogated and their status recorded. Usually some degree of checking can be applied to external devices and interfaces. For example, it may be possible to loop outputs back to inputs, thus testing through the interface packages to the peripheral side.

Ideally, no tests should be performed that rely on the functionality of untested units. The bootstrap approach of testing the integrity of the core of the system first can be based on one of two philosophies. Firstly, the designer may build the core using sufficiently reliable components that the BIT may assume the core to be fault-free. With this approach, the BIT may neglect the testing of the core and immediately proceed to examine the rest of the system. In general, this is an extremely poor assumption, because all electronic components have a finite life-time. The alternative and more realistic philosophy is to specify that the core must first be validated. Ideally, however, the philosophy employed in the implementation of BIT for a system should be a combination of the above two approaches. Therefore, the integrity of the processor, ROM and RAM should all be tested, and the components used in the design of the core should comply with relatively high reliability requirements. In a real-time embedded system it is not possible to test the functionality of the core without relying on the functionality of untested units, and, hence some faith must be placed in the core of the system being operational. Thus, in order for the system to test itself, quite a bit of the hardware must already function correctly. In this sense, the POST does tend to be of rhetorical significance, but, if the system passes all tests, it does provide the operator with confidence that the system is indeed operational. Beyond this, however, it should be realised that system self tests do have severe limitations in some cases.

The POST is required to test as many of the system functions and interfaces as possible, while simultaneously minimising the time from system start-up to full operational status. If the POST is suspicious with regards to the correct operation of certain hardware functions, these should be reported, since this indicates a potential problem. The onus should then be on the operator to perform more extensive off-line diagnostic testing.

## 3.2.2 On-line diagnostics and health monitoring

Whilst continuing to perform its main applications task, a real-time system should be performing some form of health monitoring, especially in circumstances where availability is of paramount importance. In these environments, for example, railway signalling, telephone switching or process control, space or military applications, triple redundancy schemes have been designed. In such a configuration, three complete systems operate in synchronism and periodically compare results. Democracy rules in such an instance, because any unit which produces a result at variance with the results of the other two is out-voted and ignored. In some sophisticated systems, limited corrective measures are taken by the BIT, pending operator intervention, and the out-voted system either disconnects itself from the network, or is disconnected by one of the other two. In nearly all redundancy configurations, maintenance action can be undertaken even if the system continues operation by means of its backups. Standby machines do not contribute any useful work except in emergencies. In order to gain full advantage of the redundancy and to improve availability, any fault should be reported immediately so that repairs can commence as soon as possible.

The disadvantage associated with on-line testing is the overhead involved in interrupting the main applications task of the system. This overhead must be weighed against the possibility of a failure occurring in the interval during which the test sequences are not being run. Such a failure will not be detected by the BIT, and the system may produce erroneous results. To minimize the likelihood of this happening, the frequency of the health monitoring tests may need to be increased. Some systems [KRAFT and TOY, 1981, p. 212-214] avoid the need to increase the frequency of testing by implementing a "duplication and match" philosophy. In such instances, redundant systems act as "shadow processors", matching critical outputs. When these outputs disagree, fault diagnosis routines are called to establish which system is at fault.

In addition to the firmware, the hardware also performs on-line diagnostics by means of integrated circuitry designed for the automated detection and indication of fault conditions (BITE). BITE can be designed to provide immediate notification of hardware failures as they occur. The operator should be aware of the techniques of fault indication employed by the system hardware, as these may be by visual or audio alarms [STEGE, 1988].

It can be seen from the above discussion that two major classes of redundancy exist, namely active redundancy and passive redundancy. The latter requires that external elements detect, make a decision, and switch to another element or path as a *substitute* for a failed element or path, whereas for active redundant circuits this is not the case. The decision to use redundancy must be based on a careful analysis of the trade-offs involved. Usually the introduction of redundancy increases safety

and mission reliability and availability, but reduces the mean time between failures. When methods of part improvement are shown to be more expensive than duplications or when other ways of improving system availability have been exhausted, redundant design techniques may be the only answer. It may be advantageous to use a redundant design when preventative maintenance is desired with no system down-time or when maintenance is impossible (e.g. an unmanned missile). In such cases, the prolonged real-time response caused by the redundancy needs to be carefully considered. Other disadvantages that also need consideration are increases in weight, space, cost, design time and complexity, which, in turn, results in an increase of unscheduled maintenance actions.

# 3.2.3 Off-line diagnostics

The off-line diagnostics are usually executed via menu-driven dialogue at an operator I/O device. They may be run individually, in sequences, cyclically, or interactively under the control of the operator. The operator may initiate off-line diagnostics at any time to confirm or analyze more closely a suspected failure detected by the POST or on-line health monitor. An advantage that off-line testing has over the background health monitor is the facility of more rigorous and controlled test conditions, because the module under test is isolated from operational mode conditions which may or may not be confusing the health monitor. Another advantage is that the off-line tests may also be used to commission a newly replaced module before it enters operational service.