# Implementation of a WCDMA AAA Receiver on an FPGA based Software Radio Platform

By

Saju P. Korah

University of Natal

November 2001

Submitted in fulfilment of the academic requirements for the degree of Master of Science in Engineering in the Programme of Electronic Engineering,

University of Natal, Durban, South Africa.

Dedicated to my beloved parents

and most to my savior and lord

Jesus Christ

## Preface

The research work in this thesis was performed by Mr. Saju P. Korah under the supervision of Mr. S. A. McDonald in the Programme of Electronic Engineering at the University of Natal, Durban, South Africa. This work was partially sponsored by Alcatel Altech Telecoms and Telkom SA as part of the Center of Excellence programme at the Centre for Radio Access technology.

Parts of the work documented in this thesis have been presented by the student author at following conferences:

- IEEE APBEM, SATCAM 2000, Cape town, South Africa.

- SATNAC 2000, Cape town, South Africa

- SATNAC 2001, Wild Coast, South Africa

- VTC 2001, IEEE Spring Conference (53<sup>rd</sup>), Rhodes Island, Greece

The whole thesis, unless specifically indicated to the contrary in the text, is the author's work, and has not been submitted in part, or in whole to any other university.

As the candidate's supervisor, I have approved this thesis for submission

| Name: S.A. McDonald |

|---------------------|

| Signed:             |

| Date:               |

## Acknowledgements

First and foremost my sincere thanks to almighty God who showered blessings and strengthened me during this project.

Secondly, I would like to thank Mr. S.A. McDonald for his help, encouragement and constructive criticism during the past years. His patience and support have been truly appreciated. I would also like to express my gratitude to Prof. F. Takawira for his valuable advice and comments for the completion of this project.

I wish to express my sincere appreciation to my parents for their patience, prayer, encouragement and full support over the past years. I would also like to thank my brothers and sisters.

Thanks are also owed to Telkom SA Ltd, Alcatel Altech Telecoms and THRIP for their valued financial support for the completion of this project. I would like to extend this thanks to Agilent Technologies for the donation of Advanced Design System (ADS) software, which has allowed me to simulate the complete project before implementation and Alcatel for the donation of a software radio, otherwise this project could not have become a reality.

Last, but not least, I would like to express my appreciation to my colleagues and friends for their assistance and invaluable friendship. In particular, special thanks to my former colleague Mr. Kelesh Roopram for proof reading this thesis and finally to Tim and Bret for the technical support.

i

# Contents

| Chapter 1 | Ch | ia | p | te | r | 1 |

|-----------|----|----|---|----|---|---|

|-----------|----|----|---|----|---|---|

| 1.1 Motivation                           | 1-1  |

|------------------------------------------|------|

| 1.2 Focus of the thesis                  | 1-6  |

| 1.3 Original contribution of the thesis  | 1-7  |

| 1.4 Published work                       | 1-10 |

| Chapter 2                                |      |

| 2.1 Introduction                         | 2-1  |

| 2.2 Spread spectrum                      | 2-2  |

| 2.2.1 Multipath protection               | 2-2  |

| 2.2.2 Increased privacy and security     | 2-3  |

| 2.2.3 Multiple access                    | 2-3  |

| 2.2.4 Antijamming capability             | 2-3  |

| 2.2.5 Low probability of intercept (LPI) | 2-4  |

| 2.3 Pseudorandom noise sequences         | 2-6  |

| 2.4 Physical layer overview of CDMA      | 2-9  |

| 2.4.1 Forward link                       | 2-9  |

| 2.4.2 Reverse link                       | 2-12 |

| 2.5 Benefits of CDMA                     | 2-14 |

| 2.6 WCDMA                                | 2-15 |

| 2.6.1 MAC and Radio link control         | 2-18 |

| 2.7 Summary                              | 2-18 |

| 2.8 Conclusion                           | 2-20 |

#### Chapter 3 3.1 Introduction 3-1 3.2 Antenna arrays in mobile communication 3-3 3.3 Adaptive antenna arrays 3-4 3.4 Beam steering or beamforming 3-5 3.3.1 Analogue beamforming 3-8 3.3.2 Digital beamforming 3-9 3.4 Least mean square algorithm 3-12 3.5 Applications of antenna arrays in mobile communications 3-13 3.6 Benefits of using antenna arrays 3-18 3.7 Conclusion 3-22 Chapter 4 4.1 Introduction 4-1 4.2 AAA receiver 4-3 4.2.1: Mathematical representation 4-4 4.2.2: Simulation 4-8 4.2.2.1: Matched Filter 4-8 4.2.2.2: PSA Channel estimation and beamforming 4-10 4.2.2.3: RAKE combing and symbol decision 4-11 4.3 System model 4-12 4.3.1: The transmitter 4-14 4.3.1.1: Framing 4-14 4.3.1.2: Convolutional coding 4-15 4.3.1.3 Interleaving 4-16 4.3.1.4: Spreading 4-17 4.3.2: The channel 4-17 4.3.2.1: Vehicular environment 4-19 4.3.2.2 Indoor environment 4-19

|                                                       | CONTENTS |

|-------------------------------------------------------|----------|

| 4.3.2.3: Outdoor to Indoor and Pedestrian environment | 4-20     |

| 4.3.3 PSA RAKE receiver                               | 4-21     |

| 4.4 Performance evaluation                            | 4-22     |

| 4.4.1: Discussion of simulation results               | 4-27     |

| 4.5 Power control                                     | 4-28     |

| 4.5.1 Open-loop power control                         | 4-30     |

| 4.5.2 Closed-loop power control                       | 4-30     |

| 4.6 Conclusion                                        | 4-34     |

| Chapter 5                                             |          |

| 5.1 Introduction                                      | 5-1      |

| 5.2 Benefits                                          | 5-2      |

| 5.3 FPGA in software radio                            | 5-3      |

| 5.4 System overview of the test bed                   | 5-4      |

| 5.4.1 PC interface                                    | 5-5      |

| 5.4.2 The DSP layer                                   | 5-5      |

| 5.4.2.1 System access functions                       | 5-7      |

| 5.4.2.2 Processor Access Functions                    | 5-8      |

| 5.4.2.3 Transport Access Functions                    | 5-8      |

| 5.4.2.4 Peripheral access functions                   | 5-8      |

| 5.5 Alcatel altech telecoms software radio platform   | 5-9      |

| 5.6 The interfaces                                    | 5-11     |

| 5.6.1 DSP layer and PC platform interface             | 5-11     |

| 5.6.1.1 Physical layer                                | 5-11     |

| 5.6.1.2 Data transfer layer                           | 5-11     |

| 5.6.1.3 Command transfer                              | 5-12     |

| 5.6.2 The SWR platform and the DSP platform interface | 5-14     |

| 5.6.2.1 SCI                                           | 5-14     |

| 5.6.2.2 SDI                                           | 5-15     |

| 5.7 VHDL                                              | 5-17     |

|                                            | CONTENTS |

|--------------------------------------------|----------|

| 5.8 Conclusion                             | 5-20     |

| Chapter 6                                  |          |

| 6.1 Introduction                           | 6-1      |

| 6.2 Implementation overview                | 6-1      |

| 6.3 SC-Bus signals                         | 6-4      |

| 6.4 Framing and packing                    | 6-9      |

| 6.5 Spreader and despreader                | 6-11     |

| 6.6 Filtering (Transmitter and receiver)   | 6-15     |

| 6.6.1 Transmitter filter                   | 6-18     |

| 6.6.2. Receiver filter                     | 6-20     |

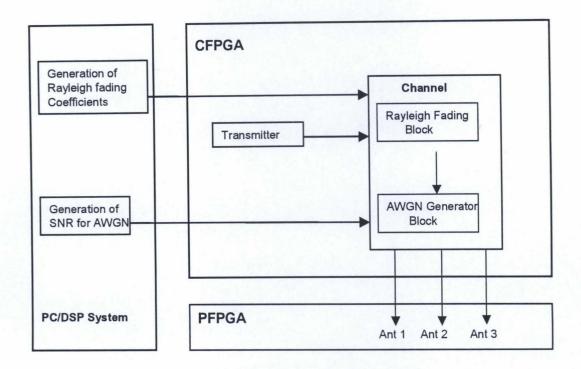

| 6.7 Channel                                | 6-23     |

| 6.7.1:Rayleigh Fading                      | 6-24     |

| 6.7.2: AWGN                                | 6-28     |

| 6.8 Receiver                               | 6-31     |

| 6.9 Evaluation of the implemented receiver | 6-39     |

| 6.10 Conclusion                            | 6-43     |

| Chapter 7                                  |          |

| 7.1 Summary and conclusions                | 7-1      |

| 7.2 Future development of the system       | 7-4      |

| References                                 | 8-1      |

| Appendices                                 | 9-1      |

# List of Figures/Tables

| Cha | pter | 2 |

|-----|------|---|

|-----|------|---|

| Figure. 2.1: Stage linear feedback shift register                           | 2-6  |

|-----------------------------------------------------------------------------|------|

| Table 2.1: Register stages and outputs                                      | 2-7  |

| Figure 2.2: PN sequences                                                    | 2-8  |

| Figure 2.3: CDMA channel overview                                           | 2-9  |

| Figure 2.4: Forward link pilot channel                                      | 2-10 |

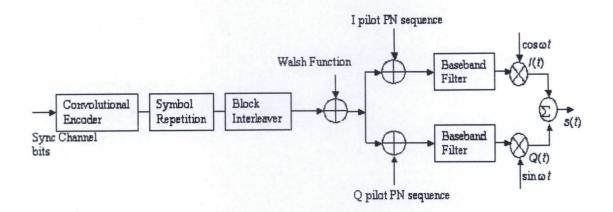

| Figure 2.5: Forward link sync channel                                       | 2-11 |

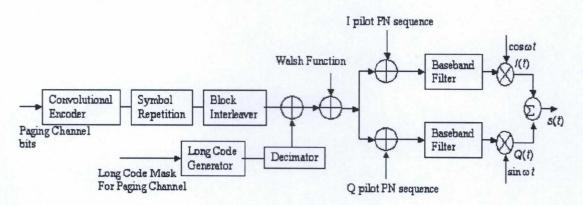

| Figure 2.6: Forward link paging channel                                     | 2-11 |

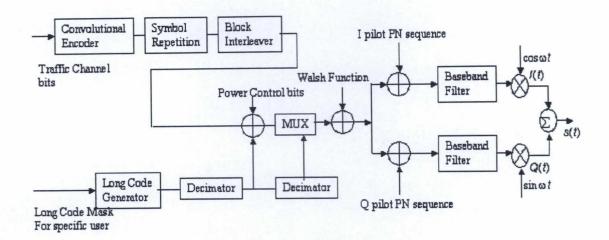

| Figure 2.7: Forward link traffic channel                                    | 2-12 |

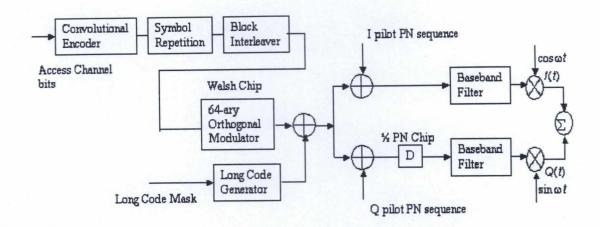

| Figure 2.8: Reverse link access channel                                     | 2-13 |

| Figure 2.9: Reverse link traffic channel                                    | 2-14 |

| Figure 2.10: Coherent RAKE receiver structure                               | 2-17 |

| Table 2.2: Parameters of WCDMA                                              | 2-19 |

| Table 2.3: Link parameters used for simulation                              | 2-20 |

| Chapter 3                                                                   |      |

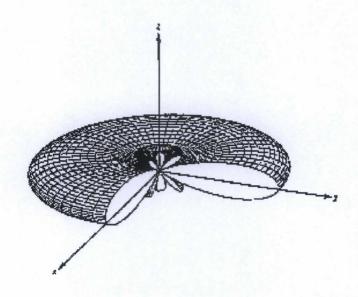

| Figure 3.1: Broadside array pattern for a linear array placed on the z-axis | 3-2  |

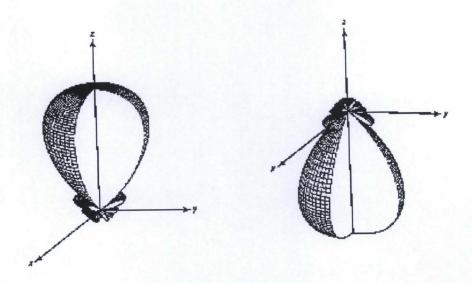

| Figure 3.2: End-fire array patterns for a linear array placed on the z-axis | 3-3  |

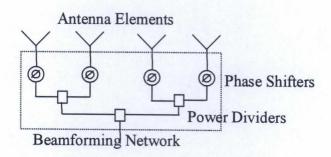

| Figure 3.3: An analog beamforming network                                   | 3-8  |

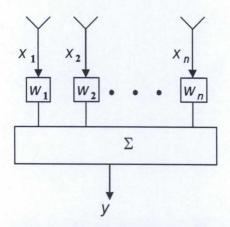

| Figure 3.4: Digital beamforming network                                     | 3-10 |

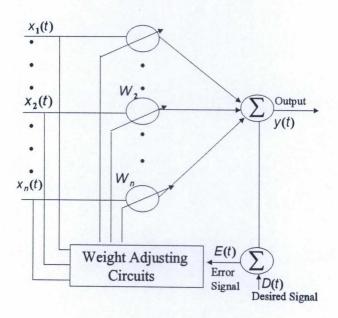

| Figure 3.5: Adaptive beamforming network                                    | 3-11 |

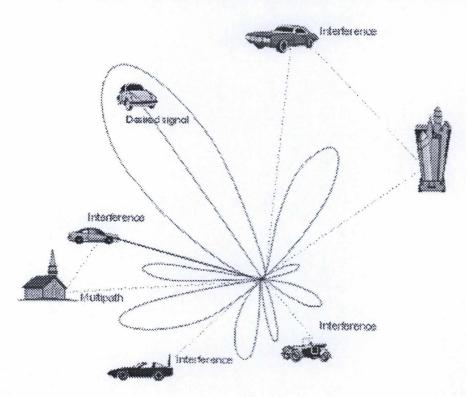

| Figure 3.6: Antenna array pattern                                           | 3-14 |

| Figure 3.7: Cell shape based upon traffic requirements                      | 3-16 |

viii

## Chapter 4

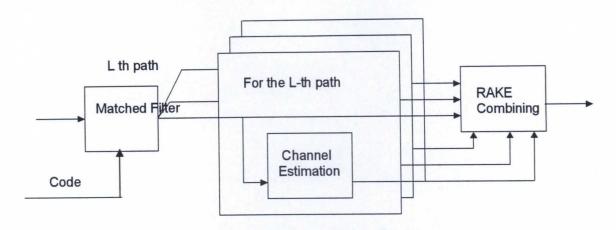

| Figure 4.1: Functional block diagram of adaptive antenna array receiver | 4-4  |

|-------------------------------------------------------------------------|------|

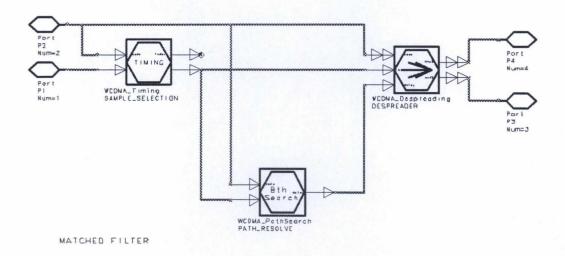

| Figure 4.2: Functional block diagram of a matched filter                | 4-9  |

| Figure 4.3: Simulated system model For AAA vs. RAKE comparison          | 4-12 |

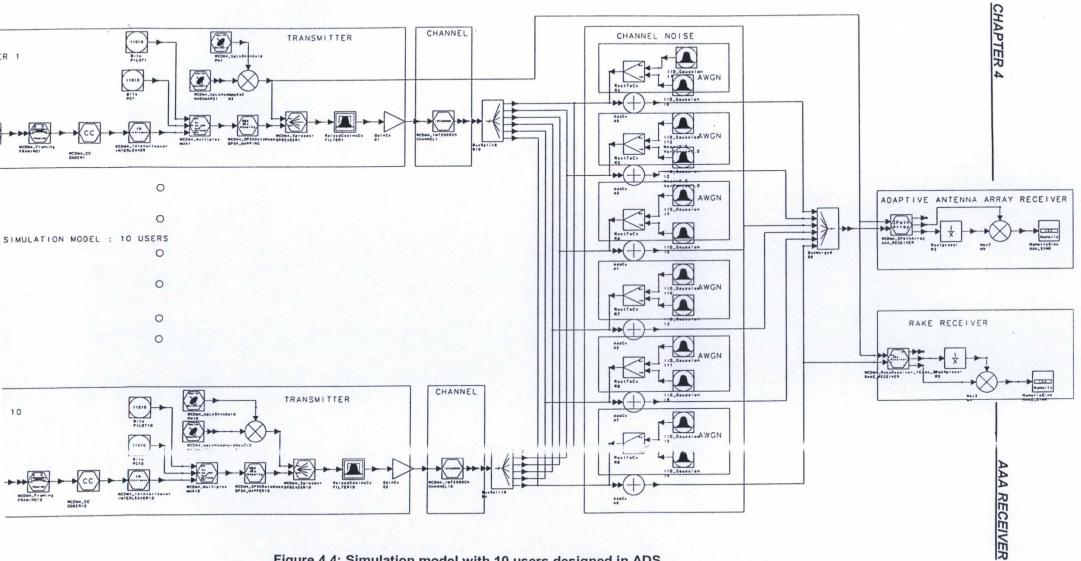

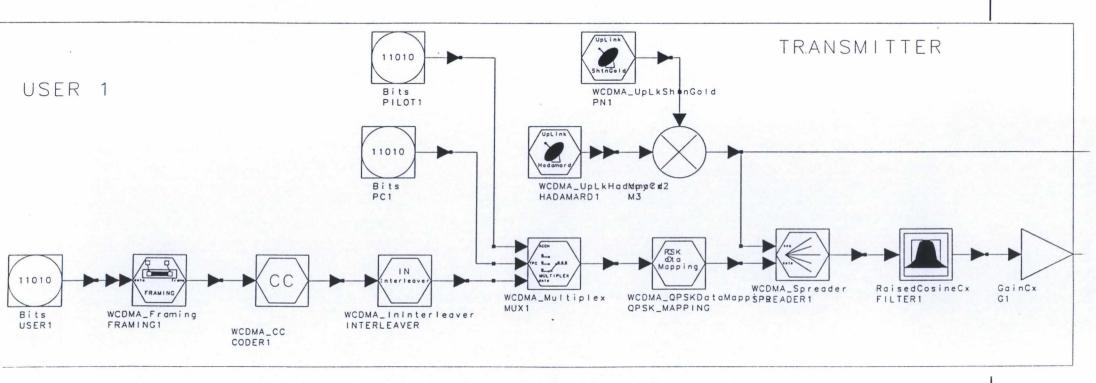

| Figure 4.4: Simulation model with 10 users designed in ADS              | 4-13 |

| Table 4.1: Transport channel formats for different class of service     | 4-14 |

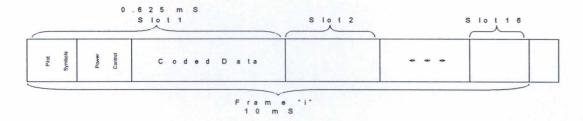

| Figure 4.5: Frame and slot structure                                    | 4-15 |

| Table 4.2: Link parameters used for simulation                          |      |

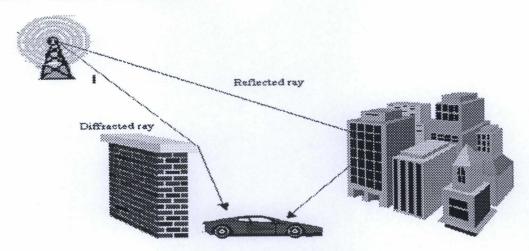

| Figure 4.6: Vehicular environment                                       | 4-17 |

|                                                                         | 4-19 |

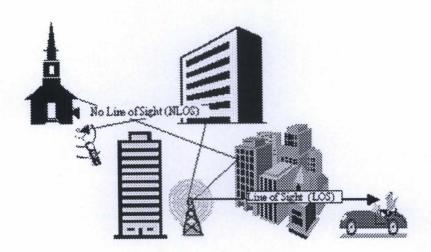

| Figure 4.7: Outdoor to indoor environment                               | 4-21 |

| Figure 4.8: Functional block diagram of RAKE receiver                   | 4-22 |

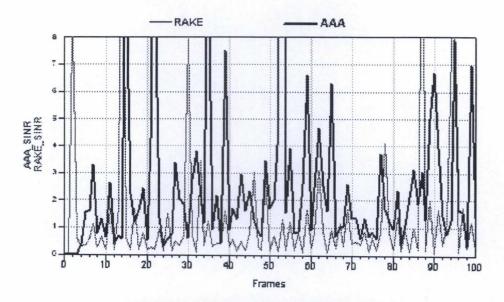

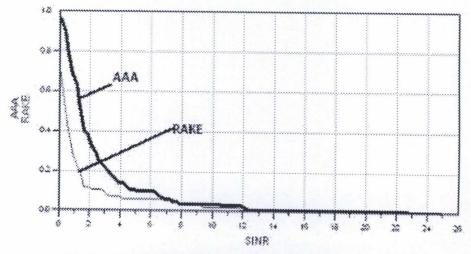

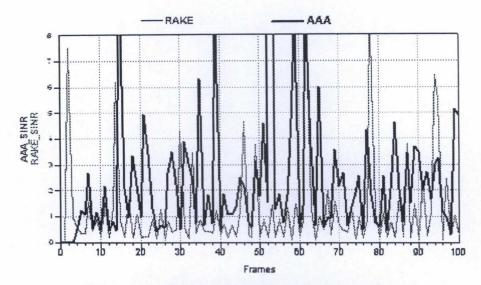

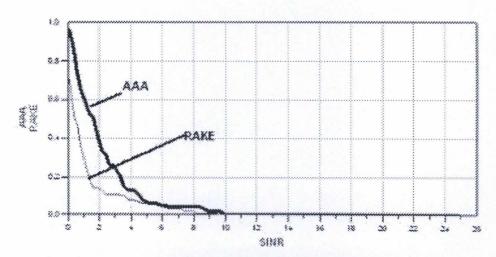

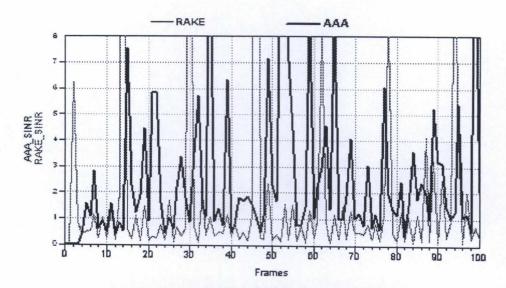

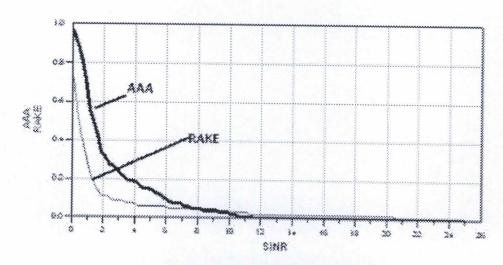

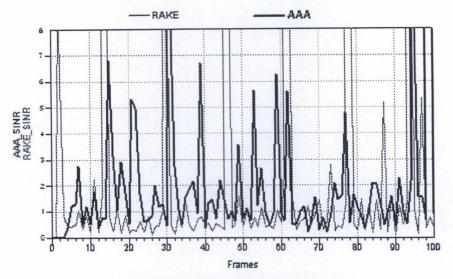

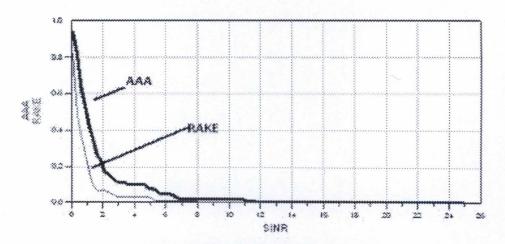

| Figure 4.9: SINR in vehicular environment                               | 4-23 |

| Figure 4.10: CCDF of vehicular environment                              | 4-23 |

| Figure 4.11: SINR in pedestrian environment                             | 4-24 |

| Figure 4.12: CCDF of pedestrian environment                             | 4-24 |

| Figure 4.13: SINR in indoor environment                                 | 4-25 |

| Figure 4.14: CCDF of indoor environment                                 | 4-25 |

| Figure 4.15: SINR in mixed environment                                  | 4-26 |

| Figure 4.16: CCDF of mixed environment                                  | 4-26 |

| Table 4.3: CCDF ratio AAA/Rake at various SINRs                         | 4-27 |

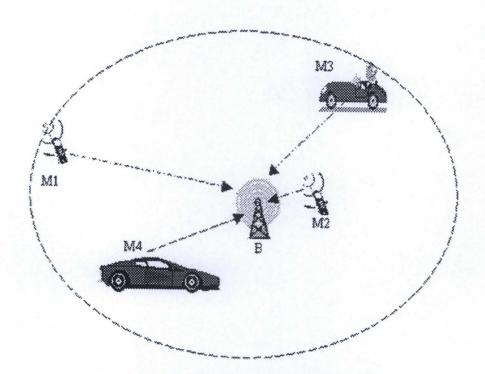

| Figure 4.17: Base station with four users                               | 4-28 |

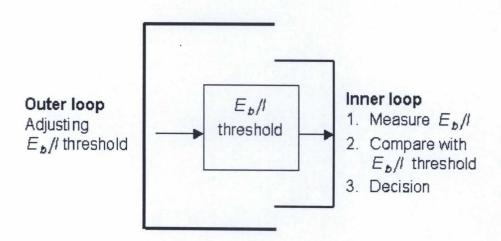

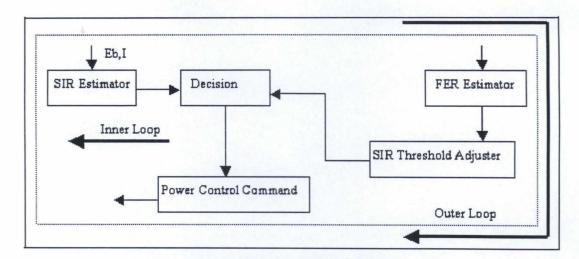

| Figure 4.18: Inner and outer loops of the closed loop power control     | 4-31 |

| Figure 4.19: Block diagram of power control structure                   | 4-31 |

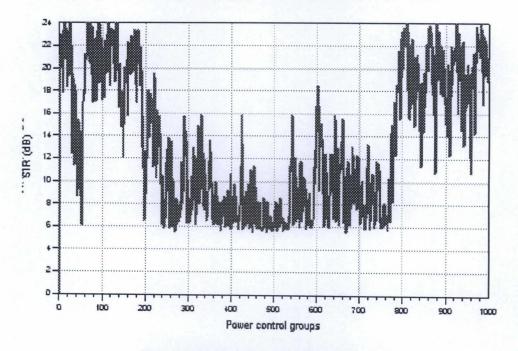

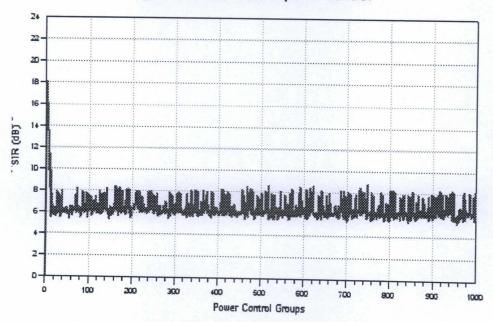

| Figure 4.20: SIR without power control                                  | 4-33 |

| Figure 4.21: SIR with power control                                     | 4-33 |

|                                                                         | 4-33 |

| Chapter 5                                                               |      |

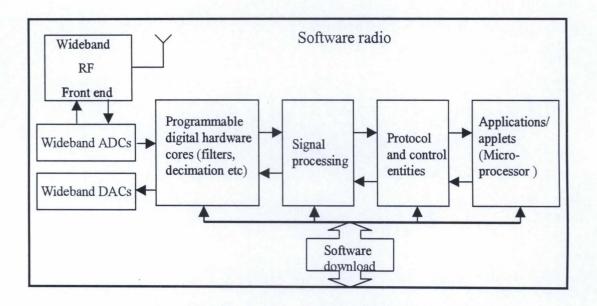

| Figure 5.1: High-level view of a generic software radio                 | 5-2  |

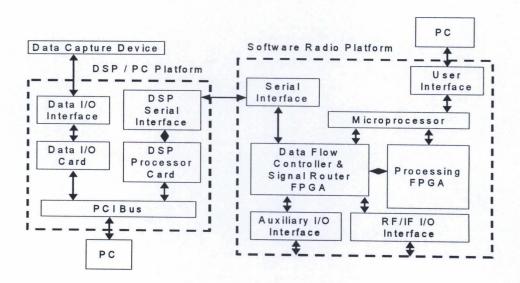

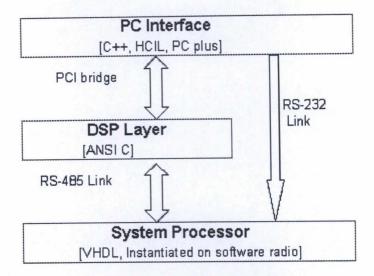

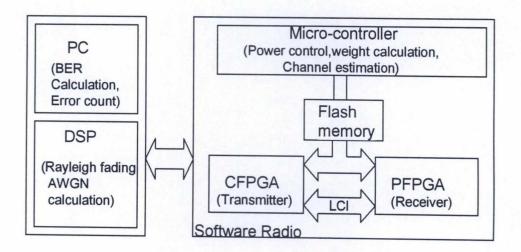

| Figure 5.2: SWR test bed block diagram                                  | 5-4  |

|                                                                         | -    |

|                                                                   | LIST OF FIGURES |

|-------------------------------------------------------------------|-----------------|

| Figure 5.3: Three-layered system                                  | 5-5             |

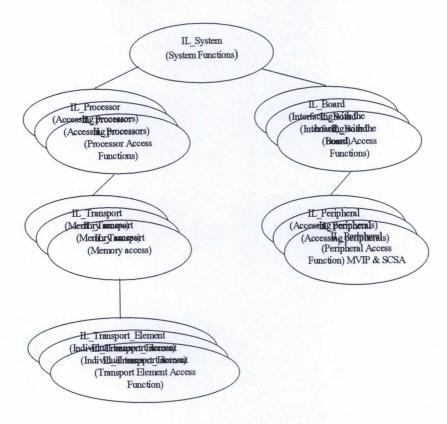

| Figure 5.4: Overview of HCIL                                      | 5-7             |

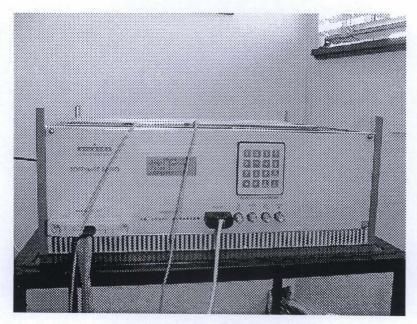

| Figure 5.5: AATs software radio                                   | 5-9             |

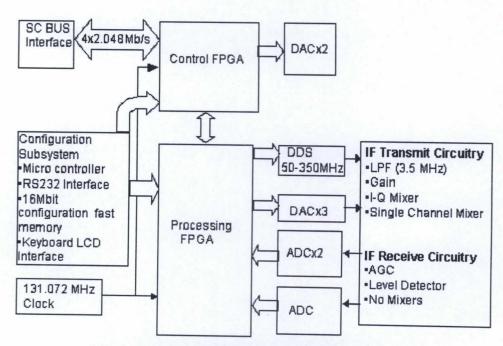

| Figure 5.6: The software radio block diagram                      | 5-9             |

|                                                                   | 5-12            |

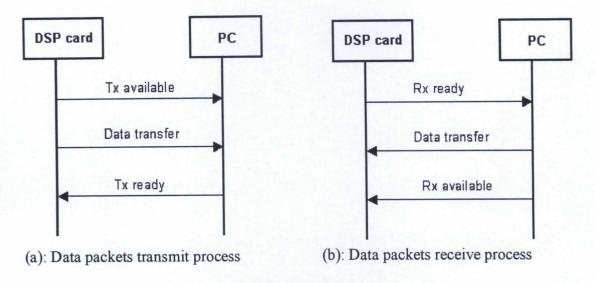

| Figure 5.7: PCI/DSP data transfer process                         | 5-13            |

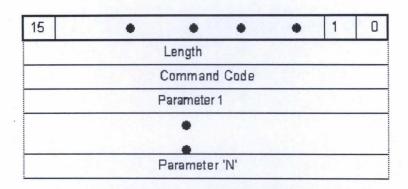

| Figure 5.8: PC/DSP command packet format                          | 5-13            |

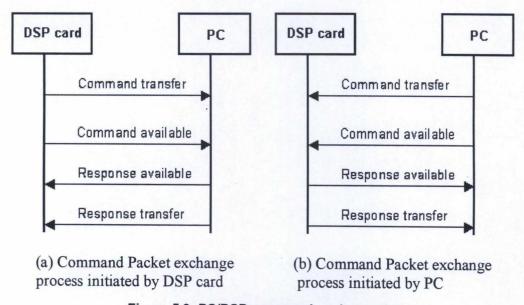

| Figure 5.9: PC/DSP command packet exchange                        |                 |

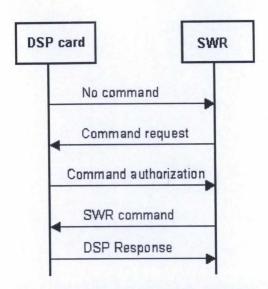

| Figure 5.10: Single command transfer sequence by SWR              | 5-15            |

| Figure 5.11: SDI Frame Format                                     | 5-16            |

| Figure 5.12: SDI Protocol Fields                                  | 5-16            |

| Chapter 6                                                         |                 |

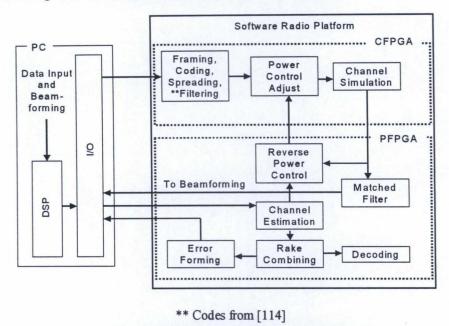

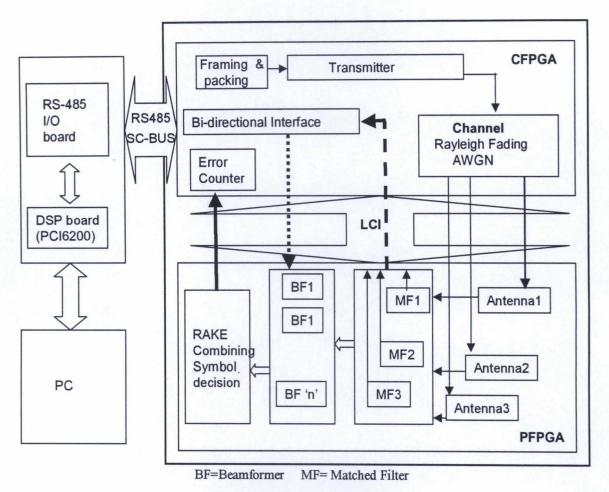

| Figure 6.1: Proposed implementation overview                      | 6-2             |

| Figure 6.2: System overview                                       | 6-3             |

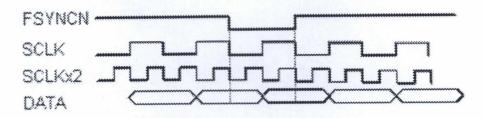

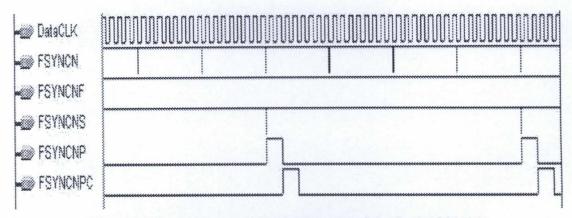

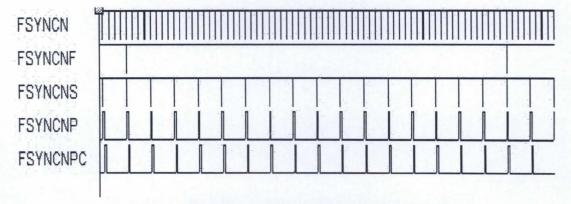

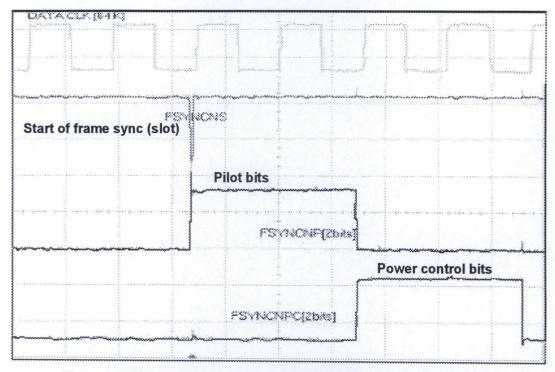

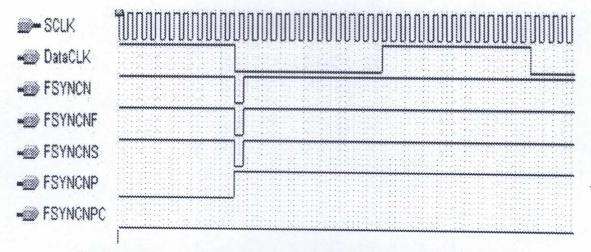

| Figure 6.3: SC bus timing diagram                                 | 6-5             |

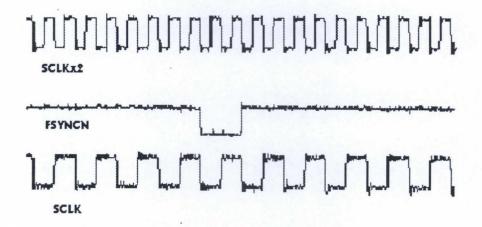

| Figure 6.4: SC bus signals measured/generated in FPGA             | 6-6             |

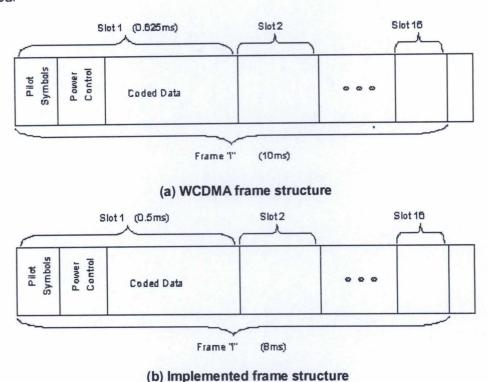

| Figure 6.5 Frame structure comparison                             | 6-7             |

| Table 6.1 Frame sync signal standards                             | 6-7             |

| Figure 6.6 Frame sync corresponding with data clock 64 KHz        | 6-8             |

| Figure 6.7 Comparison of various frame sync signals               | 6-8             |

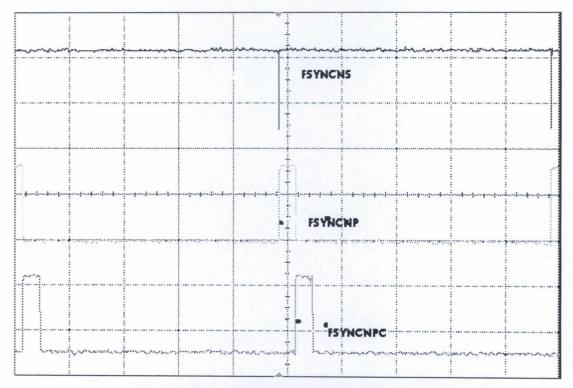

| Figure 6.8: Measured frame sync signals with data clock from CFPC | GA 6-9          |

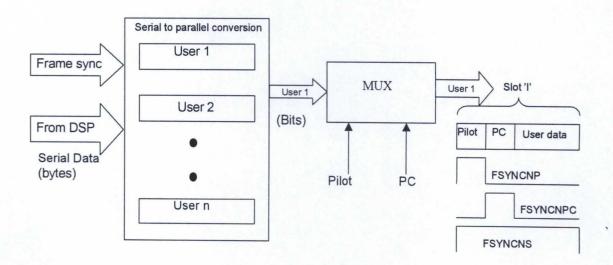

| Figure 6.9: Framing and packing process                           | 6-10            |

| Figure 6. 10: System block diagram                                | 6-11            |

| Figure 6.11: Autocorrelation of maximal length order of 8         | 6-12            |

| Figure 6.12: Entity diagram for the spreader                      | 6-12            |

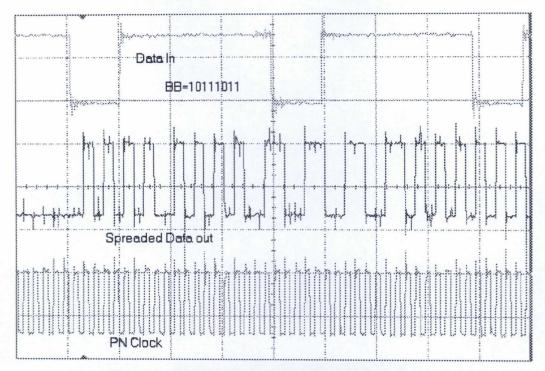

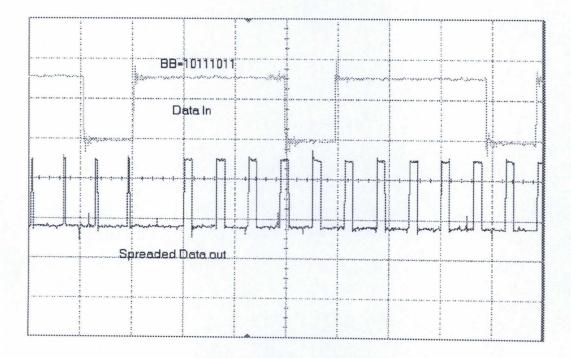

| Figure 6.13: PN clock and spreaded signal using code 1            | 6-14            |

| Figure 6.14: Spreaded signal using code 2                         | 6-14            |

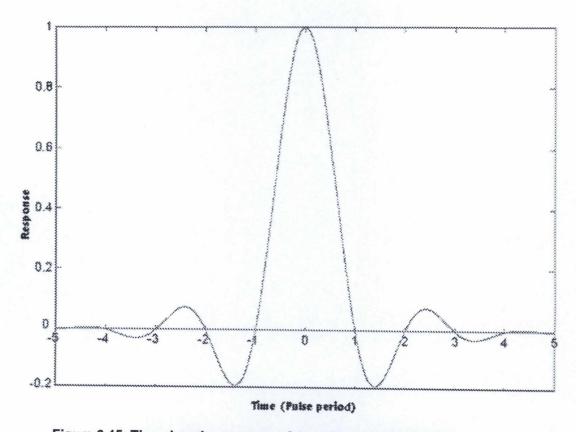

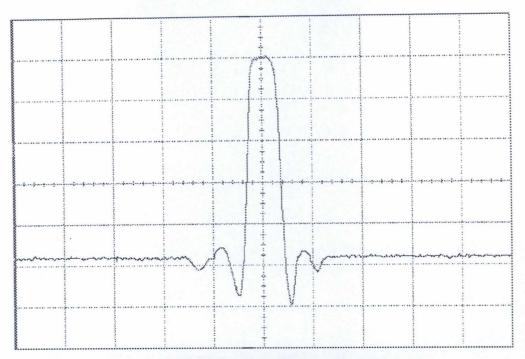

| Figure 6.15: Time domain response of the raised cosine filter     | 6-16            |

| Figure 6.16: Measured time domain response graph                  | 6-17            |

| Figure 6.17: The matched filter communication path                | 6-18            |

#### **LIST OF FIGURES**

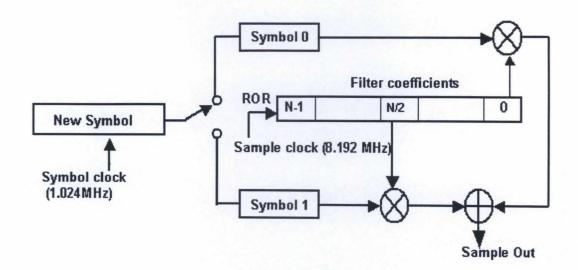

| Figure 6.18: Interpolation optimized transmitter filter structure           | 6-19 |

|-----------------------------------------------------------------------------|------|

| Figure 6.19: Measured filter response (Transmitter)                         | 6-19 |

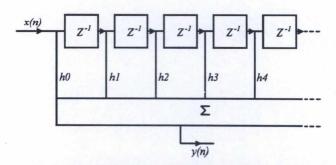

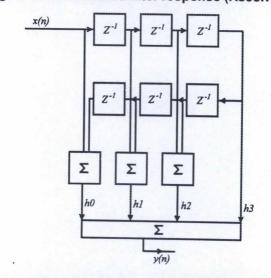

| Figure 6.20: Transversal filter implementation                              | 6-20 |

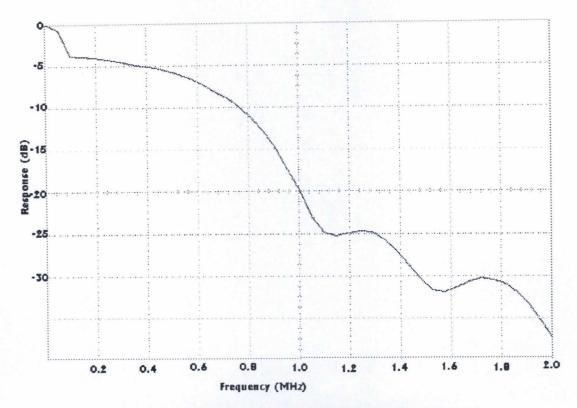

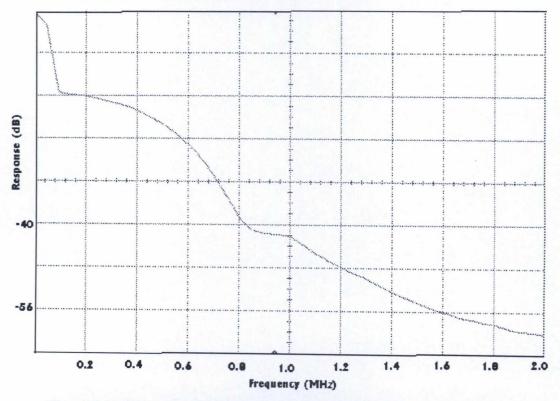

| Figure 6.21: Measured filter response (Receiver)                            | 6-21 |

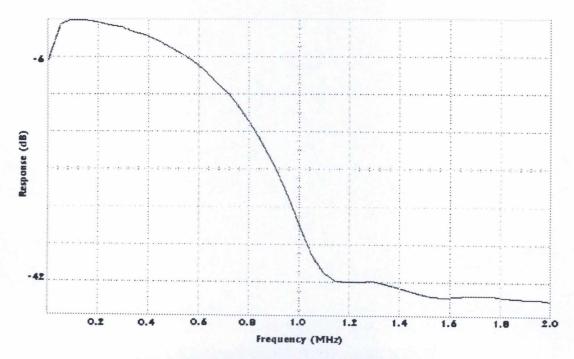

| Figure 6.22: Linear phase structure for filter                              | 6-21 |

| Figure 6.23: Measured filter response for linear phase structure (receiver) | 6-22 |

| Figure 6.24: Channel block overview                                         | 6-23 |

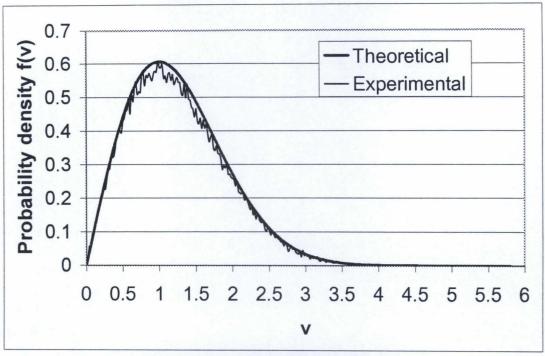

| Figure 6.25: Rayleigh fading distribution                                   | 6-25 |

| Figure 6.26: Measured Rayleigh samples received from DSP                    | 6-26 |

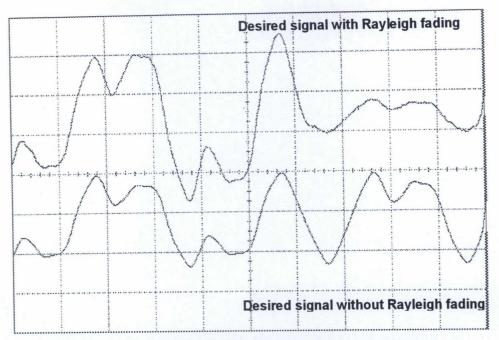

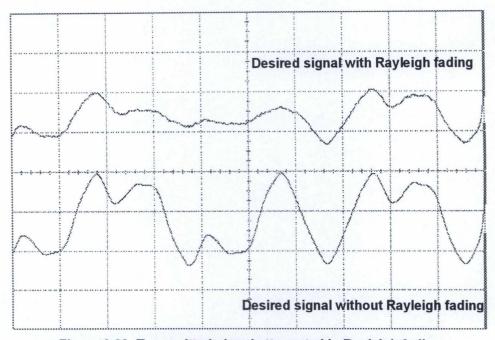

| Figure 6.27: Transmitted signal amplified in Rayleigh fading                | 6-27 |

| Figure 6.28: Transmitted signal attenuated in Rayleigh fading               | 6-27 |

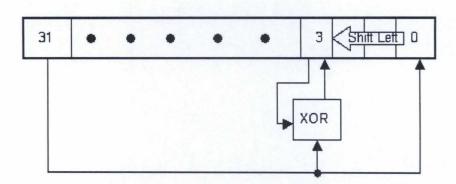

| Figure 6.29: Feedback method for uniform random generator                   | 6-30 |

| Figure 6.30: Measured AWGN channel                                          | 6-31 |

| Figure 6.31: Functional blocks of the receiver                              | 6-32 |

| Figure 6.32: Optimized structure of antenna in PFPGA                        | 6-33 |

| Figure 6.33: Multipath propagation model                                    | 6-33 |

| Figure 6.34: Angle of arrival of reflected path                             | 6-34 |

| Figure 6.35: Patch antenna array pattern                                    | 6-35 |

| Figure 6.36: Array and total array pattern at - 600 phase shift             | 6-36 |

| Figure 6.37: Patch antenna pattern at -1750 phase shift                     | 6-36 |

| Figure 6.38: Patch antenna pattern at 650 phase shift                       | 6-37 |

| Figure 6.39: Measured signal at the output of the filter                    | 6-38 |

| Figure 6.40: Structure of the error count frame                             | 6-39 |

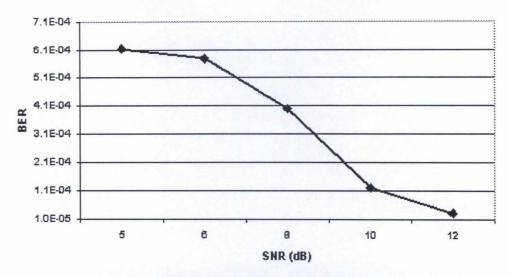

| Figure 6.41: BER with AWGN and fast Rayleigh fading                         | 6-40 |

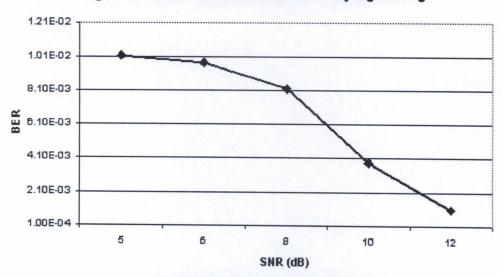

| Figure 6.42: BER with AWGN and slow Rayleigh fading                         | 6-41 |

| Figure 6.43: BER with arbitrary weights and delays                          | 6-41 |

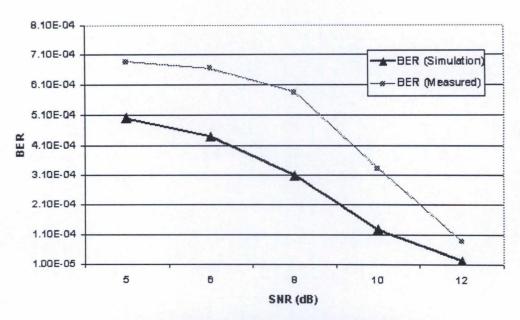

| Figure 6.44: BER (Simulation) with Rayleigh fading                          | 6-42 |

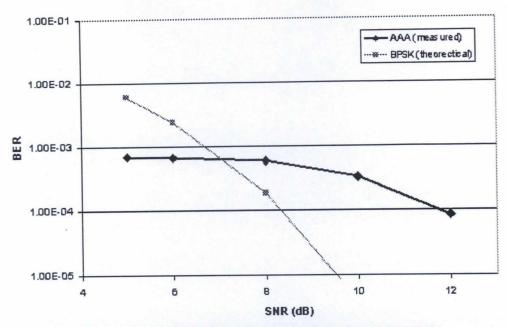

| Figure 6.45: Comparison of measured and theoretical BER                     | 6-43 |

## Chapter 7

| Figure 7.1: Functional split for the future development of the system | 7-4  |

|-----------------------------------------------------------------------|------|

| Appendices                                                            |      |

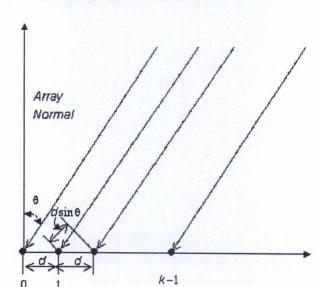

| Figure A.1 Uniformly spaced linear array                              | 9-2  |

| Figure A.2: Block diagram of Transmitter designed in ADS              | 9-6  |

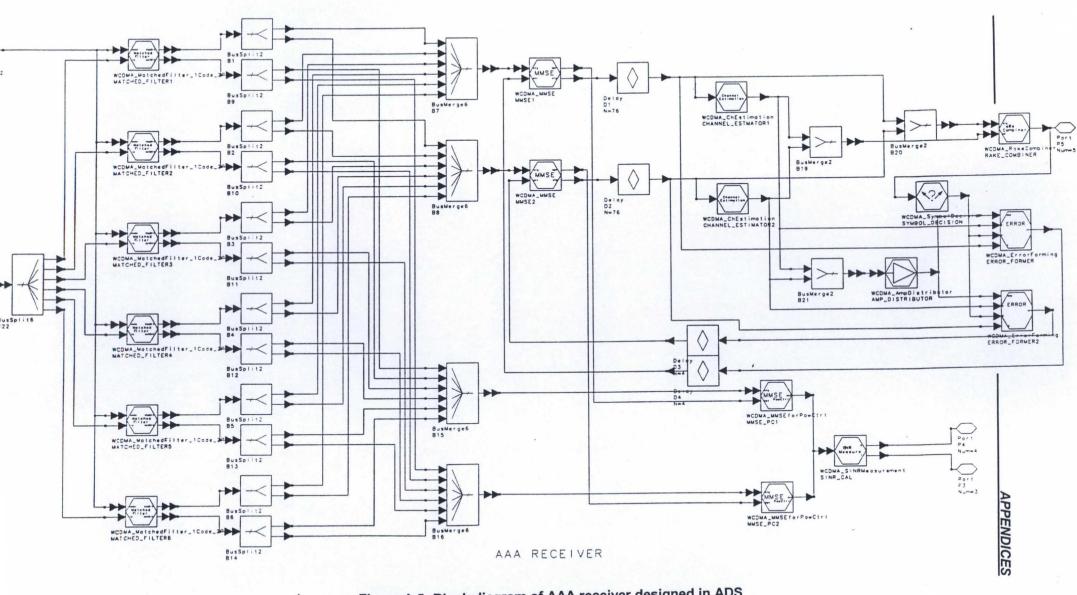

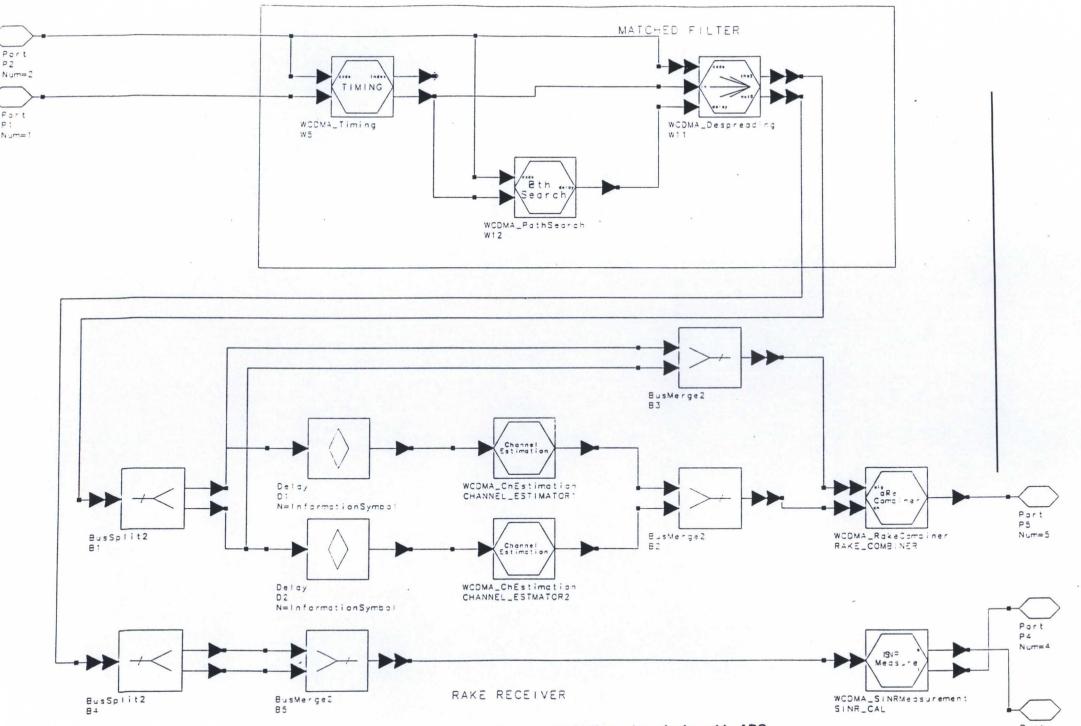

| Figure A.3: Block diagram of matched filter designed in ADS           | 9-7  |

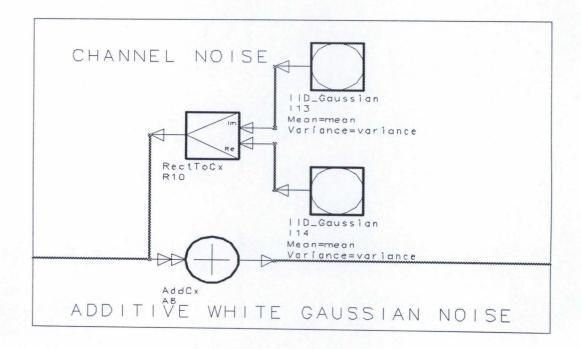

| Figure A.4: Block diagram of AWGN channel designed in ADS             | 9-7  |

| Figure A.5: Block diagram of AAA receiver designed in ADS             | 9-8  |

| Figure A.6: Block diagram of RAKE receiver designed in ADS            | 9-9  |

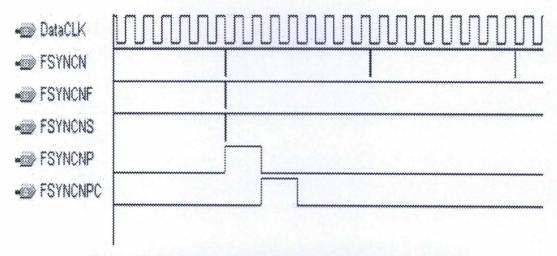

| Figure A.7 Frame sync corresponding with data clock 64 KHz            | 9-10 |

| Figure A.8 Frame sync corresponding with data clock 64 KHz & SCLK     | 9-10 |

| Figure A.9 Measured frame sync signals from CFPGA                     | 9-11 |

| Figure A.10 Multipath 1                                               | 9-17 |

| Figure A.11 Multipath 2                                               | 9-18 |

## **Abstract**

WCDMA promises to achieve high-speed internet, high quality image transmission and high-speed data services with larger system capacity. However, Multiple Access Interference is one of the major causes of transmission impairment, which reduces the link capacity in WCDMA systems. The Adaptive Antenna Array (AAA) technique reduces multiple access interference by directing antenna beam nulls towards the interfering signals by weighting the received signals from all antennas before combining the signals.

With the very rapid advancement of wireless personal communications services, a new challenge to the cellular industry is the integration of multiple systems and applications on a single device. A software radio technique offers a possible solution to achieve this goal including international roaming and multiple standard operations within the same geographical area. The main attraction of a software radio is it's flexibility, in that it can be programmed for emerging cellular standards allowing it to be updated with new software without any changes in the hardware infrastructure. A software radio incorporating adaptive array beamforming at the receiver can increase the total carried traffic in a system and transmit power while the probability of call blocking and forced termination can also be decreased.

This dissertation examines WCDMA, AAA, power control and software radio techniques in the world of wireless communication systems. Once the theoretical background of CDMA and AAA has been substantiated, the thesis establishes the need for power control in mobile systems by examining simulation results.

An AAA receiver with six antenna elements is proposed and evaluated in different environments as a precursor to implementation. It can be inferred that when the link is interference limited, the link capacity can be increased and it has been shown that the AAA receiver with six antenna elements increases the link capacity to about 2.9 times that of the single antenna RAKE receiver.

This thesis also examines the basic concepts of VHDL and considers this as the principle means to program reconfigurable core FPGA's in the software radio. A three-layered (PC/DSP/FPGA) software radio test bed is used to implement an AAA receiver. The architecture of the test bed is designed in such a way that it can be used to evaluate the performance of various FPGA based transceivers and coding schemes etc. Many of the desirable features and flexibilities inherent in the software radio concept are available on this test bed and the system has proved to be capable of high speed digital processing and is ideally suited to the development of time critical system components. The bit error rate achieved using the implemented receiver is assessed and compared to simulation results in an environment incorporating Rayleigh fading and AWGN.

## Chapter 1

## Introduction

C ommunications has become the key to momentous changes in the organization of businesses and industries worldwide as they adjust to the shift towards an information economy. Historically, communication has been restricted primarily to voice traffic between two fixed locations rather than between two people. With the advent of wireless technology, a transition from point-to-point communication has begun. Testimony to this is the rapidly increasing penetration of cordless and cellular phones into the wireless communication market all over the world.

#### 1.1 Motivation

Over the last decade the deployment of wireless communication systems has been significant. In the 1980s, the first commercial mobile telephony was introduced. The first generation of mobile systems were analog and based on Frequency Division Multiplex (FDM) technology. Due to limited technology, the size of phones was large. Advances in semiconductor technologies provided a vital boost to the cellular mobile industry. With the use of Application-Specific Integrated Circuits (ASICs), the size of the handsets reduced considerably. Second generation (2G) wireless systems employed digital modulation and advanced call processing capabilities, which fueled the growth of the cellular industry. Examples of 2G wireless systems include the Global System for Mobile communications (GSM, previously known as Groupe Speciale Mobile), Time Division Multiple Access (TDMA), examples of which are IS-54/IS134, and Code Division Multiple Access (CDMA). Specific CDMA examples are IS-95 in the

United States, Personal Digital Cellular (PDC) in Japan, Digital Enhanced Cordless Telecommunications (DECT), Personal Handyphone System (PHS) and Personal Access Communication Systems (PACS) [22-23]. Digital technology offered greater capacity, speech privacy and greater radio link robustness than analog systems which further enhanced its appeal to users and services providers alike.

Many technical features of CDMA enable the network to offer high quality on demand voice services to customers and it's ability to provide high capacity allows the service provider to better utilize its invested network assets. CDMA gained significant support among services providers because of the numerous advantages over other multiple access schemes like Frequency Division Multiple Access (FDMA) and TDMA. In a traditional FDMA scheme, increasing the required bandwidth per user decreases the total number of users a fixed spectrum can support. In TDMA systems data from each user are carried in time intervals called time slots; so additional users cannot be added once all time slots are assigned. Thus it is not possible for these schemes to increase the number of users beyond certain limits without causing an intolerable amount of interference to reception of a mobile station at the cell-site receiver.

CDMA uses a radically different approach. It assigns a unique code to each user to accommodate multiple users on the same wideband channel at the same time. The number of CDMA channels in the network depends on the level of total interference that can be tolerated in the system. Thus the CDMA system is limited by interference, and the quality of the system design plays an important role in it's overall capacity. Various promising techniques have been proposed to minimize the interference in a CDMA system. In [11], it is shown that multistage and successive interference cancellation techniques reduce interference by cancellation of one detected signal from another, the author also describe how adaptive detection algorithms can be applied to achieve this goal. In this thesis an Adaptive Antenna Array (AAA) technique is considered for suppressing the interference in the channel. The benefits and the capacity improvements achieved using the AAA technique is demonstrated in various investigations [34-36]. Various applications of AAAs in mobile communication

systems are discussed in [45-46] and [49]. CDMA systems also achieve capacity increase through the use of cell sectorization. Soft handoff, exploitation of multipath fading through RAKE combining etc are further advantages over FDMA and TDMA.

Power control techniques minimize the power in the channel, thereby reducing interference, which results in system capacity increase. Performance improvements using power control techniques is discussed in [84-86]. The performance of closed loop power control in a CDMA environment is demonstrated in [83] and [96]. This thesis investigates the performance of a closed loop power control technique. A joint power control and beamforming scheme is proposed and demonstrates the increase in system capacity via the combination of these two methods [87], [73].

The IS-95 CDMA standard was adopted by the Telecommunication Industry Association (TIA) and became a digital cellular standard in 1992. As the penetration of cellular services increased, so to did the demand for greater call capacity and higher data rates.

Third generation (3G) wireless systems evolved from the mature 2G networks, with the aim of providing universal access and global roaming. These systems are expected to support multidimensional high-speed wireless communication. The International Telecommunication Union (ITU) 3G mobile communication systems, called the International Mobile Telecommunications-2000 (IMT2000, or Universal Mobile Telecommunication Systems (UMTS) in Europe) are designed to support wideband services at data rates as high as 2 Mb/s, with the same quality as fixed networks. To realize true IMT-2000 systems, a new wideband wireless access technology incorporating as many technology developments as possible is necessary. WCDMA technology is considered to be the most promising technology to realize the IMT 2000 vision. WCDMA uses coherent demodulation in the uplink, a feature that has not previously been implemented in cellular CDMA systems. In the case of coverage, WCDMA demonstrated that it is possible to reuse GSM 1800 cell sites when migrating from GSM to WCDMA supporting high rate UMTS services [2]. The coverage of

WCDMA is determined by the link performance through link budget as shown in [25]. The results show that WCDMA speech service will tolerate a few dB higher path loss than a GSM speech service. It can be inferred from this that WCDMA gives better speech coverage than GSM, reusing the same cell sites when being deployed in the same or nearby frequency bands. Another important characteristic of WCDMA is the fact that power is the common shared resource for users. WCDMA became more attractive than other 3G systems which led to its commercial implementation. Recently, a commercial WCDMA network has been implemented by NTT, Japan.

The current challenge in radio networks is to provide integrated broadband services to every user. Third generation communication systems are intended to bring multimedia to mobile terminals. It is clear that if video applications become widely used in 3G networks existing capacity will be insufficient. This creates the need for a new system or standard which can provide higher traffic densities. As new radio standards are deployed without substantially supplanting existing ones, the need for multimode multiband handsets and infrastructure increases. In order to provide global roaming the need for a system that is reconfigurable without any change in the hardware infrastructure arises. With Software radio techniques, only one hardware infrastructure system is needed. The difference in frequency band and technology can be overcome through reconfiguring the system by downloading the software manually or through on over the air command interface [119-121].

A number of enabling technologies have allowed the development of commercially viable platforms providing an efficient bridge to 3G wireless systems. Software radio offers a means to address the issue of infrastructure evolution from GSM to UMTS from the base station perspective. From the handset perspective it offers manufacturers the potential of a UMTS handset product capable of handing off to GSM in those areas that UMTS rollout has not yet reached. It also potentially allows manufacturers to address geographical markets at different stages of migration to UMTS with a single "future-proof" product. The basic concept behind software radios has been in existence for well over ten years. There is currently a resurgence of interest in the software radio.

This is partly driven by the idea that a truly global commercial communications terminal may be realized as a software radio [127]. Early software radio research focused on the military's goal of total flexibility across dozens of radio frequency bands and air interface modes. Current research focuses more on the economic viability of introducing 3G handsets and infrastructure. The recent renaming of the Modular Multifunction Information Transfer Systems (MMITS) forum to the Software Defined Radio (SDR) forum signals the shift from military to commercial emphasis in open architecture standards for software radio [122]. The commercial sector defines a software radio as one that implements a specific range of capabilities through elements that are software reconfigurable. The software radio includes a limited set of predefined hardware functions such as air-interface Application Specific Integrated Circuits (ASIC), among which one may be selected by software.

An ideal software radio is a multimode radio with dynamic capability defined through software in all layers of the protocol stack, including the physical layer. In base stations, a wideband ADC may digitize an entire service band at IF, with programmable digital filters for channel isolation and DSP's or Field Programmable Gate Arrays (FPGAs) for demodulation. Coupled with a corresponding wideband DAC and software re-programmable functions from IF to base band, such a radio supports arbitrary air interfaces within engineering limits. FPGA-based DSP platforms allow the designer to realize the data path that exactly matches the required processing, while at the same time maintaining the flexibility of a software approach. With the advance in FPGA technology a new dimension for signal processing engineers to maintain the flexibility of software radio with performance close to ASICs has been provided.

This thesis will examine a particular type of software radio with two high speed FPGAs as the reconfigurable core. Design and implementation issues of a WCDMA AAA system that exploits the benefits of these key technologies are also discussed. The implementation of a specific WCDMA AAA transceiver on the software radio will allow the reader to explore, how the radio flexibility can work towards easier development and overcome new system deployment problems.

#### 1.2 Focus of the thesis

In order to amalgamate the techniques of spread spectrum, AAA, power control, and software radio into a working system a thorough investigation is required. From an implementation point of view, this thesis focuses mainly on three issues: the physical layer of a CDMA system, practical channel behavior model and the hardware level of the software radio.

Chapter 2 examines the theoretical concepts of spread spectrum techniques, where CDMA is considered as the basic structure to explain the concepts of a WCDMA wireless system. Pseudorandom Noise (PN) sequences are used to spread the incoming signal in the WCDMA system. Simulated results are presented to demonstrate the behavior of PN sequences. The physical layer of CDMA, presented in Section 2.4 familiarizes the reader with the component level of the system, simultaneously discussing the differences between the CDMA and WCDMA physical layers. An overview of the WCDMA standard is discussed in order to implement the proposed system using WCDMA standards. The benefits of WCDMA over CDMA are also discussed.

An Adaptive Antenna Array technique minimizes the multiple access interference in WCDMA systems, thereby increasing the system capacity. This thesis considers AAA techniques as a means of minimizing MAI in the system. Chapter 3 examines the theoretical concepts of antenna arrays, beamforming and the application of adaptive antenna arrays to mobile communication systems. The spatial filtering properties of the antenna array which reduces the cochannel interference and the capability of forming beams in certain directions and nulls in others, which provides the ability to cancel some of delayed signals, are the principle benefits of antenna arrays. Formation of multiple beams also reduces the handoff process in the network. The Least Mean Square algorithm is also discussed to demonstrate the weight adaptation method that could be employed in the implemented system.

In Chapter 4, a WCDMA receiver using a six element AAA to suppress the MAI is proposed for implementation. Mathematical representation of the proposed AAA receiver model is discussed. In order to justify the proposal for implementation, a system model is designed to carry out a performance evaluation. An AAA receiver with six antenna elements and a single antenna element RAKE receiver with ten users are considered for evaluation. The 3G mobile communication systems are expected to operate in various environments. It is infeasible to consider all environments but considering the essence of possible environments, four different environments are considered namely; vehicular, indoor, and outdoor to indoor pedestrian and finally a mixed environment (which is a practical channel with AWGN). The significant performance improvement of the proposed receiver in all environments justifies it's implementation. The penultimate section of Chapter 4 establishes the need for power control in mobile CDMA environments using simulation results. Also described is a closed loop power control algorithm, which can be incorporated in the implementation in future developments. The simulations discussed in chapter 4 were completed as a precursor to the implementation of the proposed receiver in the software radio.

Chapter 5 explores the basic concepts of the software radio. Although the 3G wireless concepts address the goal of global standardization, an approach which is more realistic in the intermediate term and more flexible in the longer term, is to develop transceivers that will operate with several standards and in several frequency bands on a common hardware platform. Such a platform would allow flexible and programmable operations. This chapter introduces the concept of flexibility in a software radio and discusses the specific radio tasks via partitioning of radio architectures into the two core programmable technologies of DSPs and FPGAs. A PC/DSP/FPGA based software radio test bed is utilized and is presented in Section 5.4. This test bed can be used to evaluate various FPGA based transceivers and provides a good alternative to system simulation on a purely PC platform. The system is presented as a three layered architecture and the various interfaces and protocol specifications are also discussed. Alcatel Altech Telecoms (AAT) flexible software radio platform is discussed, giving

the reader a firm understanding of the environment in which the proposed system model was implemented. The benefits of the core programmable device (FPGA) in the software radio are also reviewed. The data sources for the FPGA include ADCs and serial data streams. VHDL is considered as the means of programming the FPGAs in the software radio. Section 5.7 introduces the features of VHDL, explains VHDL terms using a simple VHDL program and discusses the synthesis process.

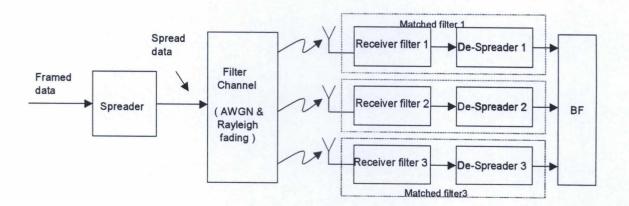

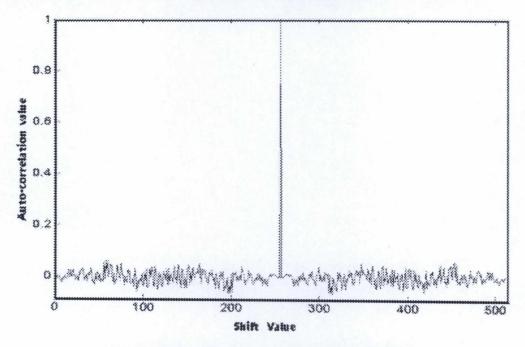

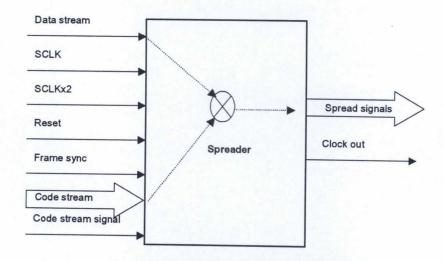

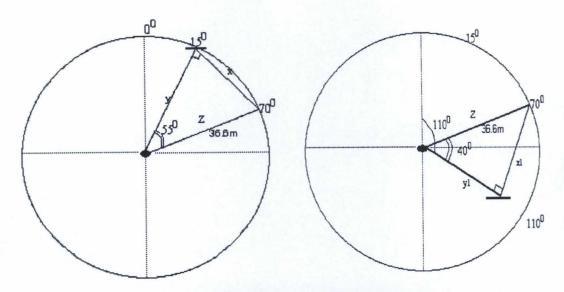

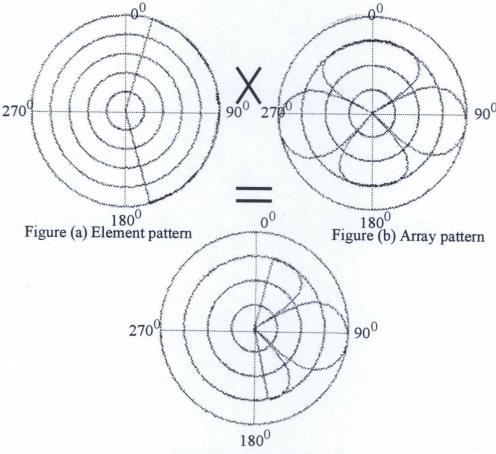

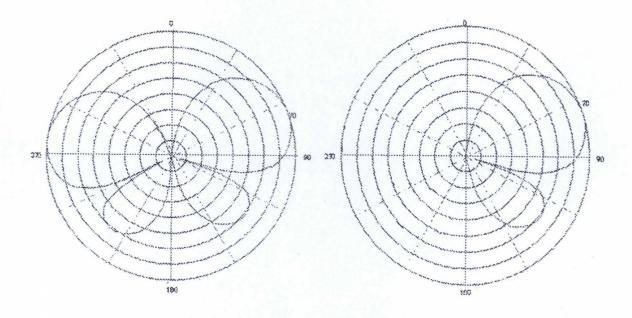

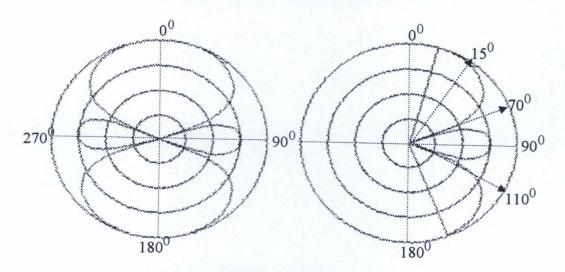

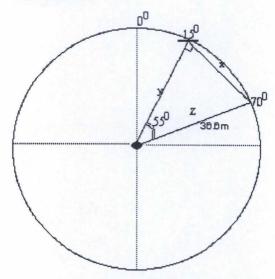

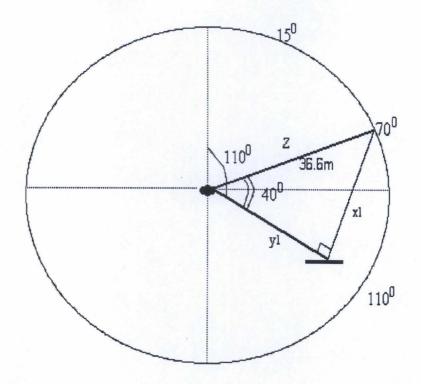

Chapter 6 moves the reader into the implementation arena where the proposed implementation plan and actual system to be implemented are discussed. Measured results of each block are presented and discussed to justify the implementation. Section 6.3 tackles the system time critical components and the generation of various synchronization frame signals used in the design. A different approach is considered to explain the implementation issues. This approach uses simple block diagram rather than VHDL code explanation. Section 6.5 explores one of the core elements of the transmission aspects of the system; that of spreading and despreading of the base band data. A simulation is used to demonstrate the autocorrelation function of a PN sequence. The signals measured at the output of transmitter and receiver filters describe the basic filter concepts. The chapter familiarizes the reader with the theoretical aspect of Rayleigh fading and AWGN and the practical implementation of these channel distortions. A subsection is used to explain the realization of antenna arrays in the software radio. Due to the limited capacity in the FPGA, mobility of the desired user is avoided. The weights were calculated manually and stored in the DSP memory and fed to the multipliers used in the beamformers. A theoretical radiation pattern of a patch antenna is used to calculate the total array pattern in order to determine the appropriate weights for each of the desired users. The chapter concludes with the results obtained for system performance in both AWGN and uncorrelated Rayleigh fading channels and also exposes the reader to the high-speed capabilities of the software radio.

Chapter 7 concludes this thesis with suggestions for future development and improvement of the implemented system. The system developed on the software radio

test bed can be used as a basic structure to implement a complete WCDMA network as a part of Centre of Excellence Programme.

#### 1.3. Original contribution of the thesis

The original contributions of this thesis are listed below.

- 1. Optimization of an AAA receiver using ADS software.

- 2. A system model is designed to carryout the comparative performance evaluation of an AAA receiver (with six antenna elements) and a RAKE receiver.

- 3. A comparative performance evaluation results in four different environments for the different receivers are presented.

- 4. A simple closed loop power control structure is derived and simulated using the ADS environment.

- 5. Implemented a rudimentary AAA receiver on a DSP/FPGA based software radio platform.

- 6. Generated and optimized code for the following system components in the software radio.

- i. Frame synchronization signals

- ii. Framing

- iii. Spreading

- iv. Rayleigh fading

- v. AWGN

- vi. Antenna array structure

- vii. Despreader

- viii. Beamformer

- ix. RAKE combiner (equal gain)

- x. Error counter

Since this work builds on developments of all students involved in the Centre of Excellence, it should have noted that only the transmitter and receiver filter used in this design are from Ellis, [114]

#### 1.4 Published work

The following publications have resulted from this work, which have been presented by the student author at the following national and international conferences

- "A Comparative Performance Evaluation Of Coherent Adaptive Array Diversity DS-CDMA Receiver", Proc. of IEEE APBEM, SATCAM2000, Cape town, South Africa.

- "Performance Evaluation Of Reverse Link Power Control in a Mobile CDMA Environment", Proc. of SATNAC2000, Sept.11-13, Cape town, South Africa.

- "Towards the implementation of a WCDMA AAA receiver on an FPGA software radio platform". Proceedings of 53<sup>rd</sup> VTC2001, IEEE Spring Conference (May6-11, 2001), Rhodes Island, Greece.

- "Operational Overview of a DSP/FPGA Based Software Radio". Proc. of SATNAC2001, Wild Coast, South Africa.

## Chapter 2

# Code Division Multiple Access

#### 2.1 Introduction

The demand for mobile radio services has continued to increase dramatically for many years and this expected high demand has led many service providers to investigate digital technology to satisfy the increasing demand. Many of the users are becoming increasingly interested in minimizing the possibility of their communication signals being intercepted or received by an unintended party. Spread spectrum modulation is a promising technique for communication signal protection against unauthorized interception as well as protection against intentional and accidental interference [18]. Spread Spectrum techniques provide the wireless communication developer with a host of exciting and powerful possibilities. For instance, it offers the prospect of its coexistence, in a near-transparent fashion, with narrow-band signals. From this, it is clear that spread spectrum signals are fairly immune to jamming signals. In this light, it may be asked why the technology has not been more widely used. The truth is that it has been used for decades in a military context, and the answer to it's slow infiltration of civilian use lies in the fairly complex nature of its implementation. However, as the mobility of the world's telecommunications infrastructure has dramatically increased. so the demand for new signal transmission techniques such as spread spectrum has also This, coupled with formidable technological advances, has led to the feasibility of using spread spectrum within a civilian context. Spread spectrum has been used for a long time in military communications to resist intentional jamming and to achieve low-probability of detection. However, in recent years spread spectrum techniques have moved from military to commercial communications, culminating in the introduction of Code Division Multiple Access (CDMA) technology as an alternative standard for commercial digital cellular systems.

#### 2.2. Spread Spectrum

The definition of spread spectrum techniques [6] is as follows:

"Spread spectrum is a means of transmission in which the signal occupies a bandwidth in excess of the minimum necessary to send the information; the band spread is accomplished by means of a code which is independent of the data, and a synchronized reception with the code at the receiver is used for despreading and subsequent data recovery".

The use of spread spectrum means that each transmission utilizes a large amount of spectrum, this may be compensated for by the interference reduction capability inherent in the use of spread spectrum techniques, so that a considerable number of users might share the same spectral band. The basic signal characteristics of the spread spectrum systems are [18]:

- The carrier is an unpredictable wide band signal

- The bandwidth of the carrier is much larger than the bandwidth of the data modulation

- Reception is accomplished by cross correlation of the received wideband signal with a synchronously generated replica of the wideband carrier.

Spread spectrum systems, because of the nature of their signal characteristics have at least five important attributes:

#### 2.2.1 Multipath protection

In the receiver the arrived signal is not just a single path signal from the transmitter. Due to transmission through objects and reflections, the signal arrives at the receiver from different paths. These are the same as the transmitted signal but with phase differences, different amplitudes, delays and arrival angles. Combining these signals at the receiver will be constructive at some of the frequencies and can reject others. In the

time domain, this results in a dispersed signal. Spread spectrum modulation can combat this multipath interference and depends very much on the type of modulation used.

#### 2.2.2 Increased privacy and security

The data signal is spread with coded sequences and can only be despread and recovered if the receiver knows the replica of the coded sequences. This increases privacy and security. Cryptographic capabilities result when the data modulation cannot be distinguished from the carrier modulation and the carrier modulation is effectively random to an unintended receiver. A system using indistinguishable data and spread spectrum carrier modulation is a form of privacy.

#### 2.2.3 Multiple access

Transceivers using independent random carriers can operate in the same bandwidth with minimal cochannel interference. These systems are called spread spectrum Code Division Multiple Access (CDMA) systems [18]. In CDMA all the users have the same bandwidth at the same time, but separated with different Pseudorandom Noise (PN) codes which must be orthogonal to each other. If PN codes are orthogonal then their cross correlation over the one code length time of the PN codes is zero. In the receiver, correlating the received signal with the particular code signal from a certain user will then only despread the signal of the user, while the other spread signals will remain spread over a large bandwidth. Thus, within the information bandwidth, the power of the desired user will be larger than the interfering power provided there are not too many interferers, and the desired signal can be extracted.

#### 2.2.4 Antijamming capability

The antijamming capability, especially narrow band signal jamming, has been exploited in military systems for a long time. This is more or less the same as interference rejection except the interference is unlawfully inflicted on the system.

#### 2.2.5 Low probability of intercept (LPI)

LPI can be achieved with high processing gain and unpredictable carrier signals when power is thinly and uniformly spread in the frequency domain. The low density of spread spectrum signals is an inherent spread spectrum property, which exists because of the bandwidth expansion.

There are three general approaches to implementing spread spectrum systems

- a) Frequency Hopping Spread Spectrum: In frequency hopping spread spectrum, the carrier frequency is shifted in discrete increments in a pattern generated by a code sequence. It creates uncertainty at the hostile receiver by randomly shifting the base bandwidth between a number of possible frequency intervals or cells. Assuming the frequencies used are packed as tightly as orthogonality permits. Typically the new carrier phase cannot be predicted when a frequency hop occurs. Frequency hopping spread spectrum systems are of two types; fast and slow hop systems. In a slow hop system, the hop rate is less than the message bit rate and in fast hop system the hop rate is greater than the message bit rate.

- b) Time hopping spread spectrum: In time hopping spread spectrum systems the transmission time is divided into intervals called frames. Each frame is divided into time slots and during each frame only one time slot is modulated with a message. Uncertainty is created at a hostile receiver by varying the intervals of time. Time hopping is useful as a form of random time multiplexing allowing both transmitter and receiver use of the same antenna [18]. The pulse rate in time hopping is same as the bit rate of the message it transmits.

- c) Direct Sequence Spread Spectrum: In direct sequence spread spectrum the message carrier is modulated by a digital code in which the code bit rate is much larger than the information signal bit rate. Unlike time hopping, direct sequence typically transmits continuously during the bit interval, not just over a subinterval. Thus it transmits all the time and continually uses all of the spread spectrum bandwidth.

CHAPTER 2 CDMA

The excellent performance of spread spectrum techniques against interference signals has motivated cellular providers to implement this system for commercial use. In early 1990 QUALCOMM Inc. pioneered innovative implementation approaches using CDMA spread spectrum digital cellular systems. This CDMA system was standardized and is known as the IS-95 standard of the Telecommunications Industry Association and the Electronic Industries Association (TIA/EIA/IS-95).

In this thesis, the implemented system employs direct sequence spread spectrum techniques. A system in which the spreading signal has a bandwidth greater than the minimum bandwidth required to transmit the desired information satisfies the requirements of direct sequence spread spectrum techniques. At the receiver, despreading is achieved by the cross-correlation of the received spread signal with a synchronized replica of the same signal used to spread the data. In CDMA Pseudorandom Noise (PN) code signals are used to spread the information signal.

#### 2.3 Pseudorandom Noise Sequences

A Pseudorandom Noise (PN) sequence is a sequence of binary 1's and 0's with autocorrelation properties similar to white noise. In CDMA systems, pseudorandom noise sequences are used to perform the following tasks:

- Larger bandwidth for transmission via modulation of the data signal

- Providing a unique identity for each user by using the same transmission bandwidth in the multiple access scheme

The PN sequences are not random but are deterministic, periodic sequences. The following are the important properties of PN sequences from [10]:

- The relative frequencies of zero and one are each ½

- For zeroes or ones, half of all run lengths are of length 1; one quarter are of length 2; one eighth are of length 3; and so on

- If a PN sequence is shifted by any nonzero number of elements, the resulting sequence will have an equal number of agreements and disagreements with respect to the original sequence

CHAPTER 2 CDMA

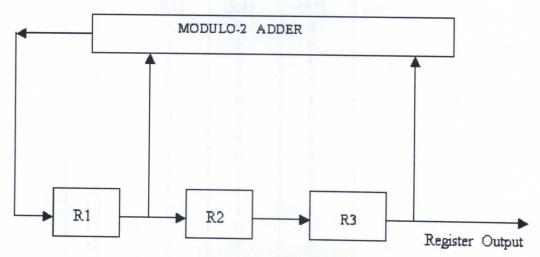

A deterministically generated sequence that nearly satisfies the above three tasks within extremely small discrepancies is referred to as a pseudorandom sequence. PN sequences can be generated by using n-stage linear feed back shift registers. A feed back shift register consists of two memory storage stages. Binary bits are shifted through the different stages of the register in response to clock pulses connected to it. The output of the stages are combined to produce the input of the first stage. The contents of the initial stage and the feed back logic will determine the contents of the next stage. A feed back shift register and its outputs are called linear when the feed back logic consists of modulo-2 adders.

To explain the properties of PN sequences, consider a three-stage linear feedback shift register as shown in Figure 2.1. The output of the last stage (stage 3) is connected to the modulo-2 adder and a feedback path is connected to the first stage. The operation of the shift register is controlled by a sequence of clock pulses. In the case of CDMA the clock period can set to the chip time. At each clock pulse, the contents of the shift register at each stage will shift by one stage to the right. Also at each clock pulse the contents of the stages R1 and R3 are modulo-2 added, and the result is fed back to stage R1. The shift register sequence is defined to be the output of stage R3

Figure. 2.1: Stage linear feedback shift register

If one assumes that the first stage of the shift register R1 is initially filled with a 1 and the other stages are filled with 0, the initial stage of the shift register is 1 0 0. After

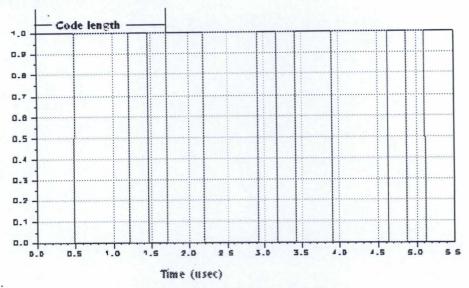

Figure 2.2 shows the PN sequence generated in ADS simulation environment using a 3-stage linear feedback shift register.

Figure 2.2: PN sequences

Autocorrelation is the degree of correspondence between a sequence and a phase shifted replica of the same sequence. When the autocorrelation reaches a maximum, then the two codes are in-phase and have a time shift of zero. In a CDMA system, this function is done by a mobile station to acquire the unmodulated pilot channel. The reverse channel in CDMA is the link from mobile station to the base station while the forward channel is from base station to mobile station. The reverse link uses a long PN code for channelization. The long code has a length of  $2^{42} - 1$  chips and is generated using a 42-stage register. The forward link uses Walsh or Hadamard codes for channelizing individual users of a particular base station. However, the forward link also uses the PN code. Each base is assigned a unique PN code that is superimposed on top of the Walsh code. This is done to provide isolation among the different base stations because each base station uses the same 64 Walsh code set. The short PN codes that are used in the forward link have a length of  $2^{15} - 1$  chips and are generated using a 15-stage register.

CHAPTER 2 CDMA

#### 2.4 Physical layer overview of CDMA

As in depth presentation of a CDMA physical layer is provided, as it is necessary to understand the implementation issues that is addressed in Chapter 6.

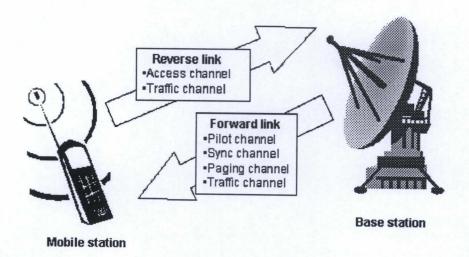

As previously stated a CDMA channel consists of forward CDMA and reverse CDMA channels between the base station and mobile station. In the forward channel Walsh codes are used to distinguish different channels, while in the reverse channel PN sequences are used to distinguish the channels.

#### 2.4.1 Forward link

The forward channel consists of four types of logical channels: pilot, sync, paging and traffic channels [20,95]. Figures 2.3 and 2.4 show the CDMA channel overview and block diagram of a CDMA (IS-95) forward link pilot channel respectively.

Figure 2.3: CDMA (IS-95) channel overview

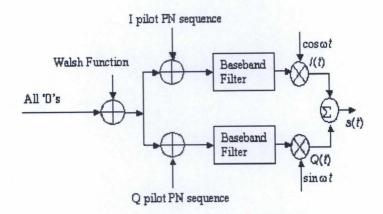

Figure 2.4: Forward link pilot channel [20,95]

2.4.1.1: Pilot channel: The pilot channel is an unmodulated spread spectrum signal, which is continuously transmitted by the base station on each active forward CDMA channel. The mobile station monitors the pilot channel at all times except when not receiving in the slotted mode [20]. The pilot channel provides the mobile with timing and phase reference. The SINR measurement of pilot channel in a mobile station provides information as to which is the strongest serving sector for that mobile.

2.4.1.2 Sync channel: Figure 2.5 shows a block diagram of forward link sync channel. The sync channel transports synchronization messages to the mobile station. The sync channel is convolutionally encoded and interleaved before transmission. Each sync channel frame begins with the start-of-message bit. '1' indicates the start of the sync channel message and '0' indicates that the current sync channel frame has the contents of a running sync channel message that started in the previous frame. The sync channel message contains information relating to the offset of the pilot PN sequence used by the transmitter sector and the information to enable the mobile to synchronize with the long PN code.

Figure 2.5: Forward link sync channel [20,95].

2.4.1.3 Paging channel: Figure 2.6 shows a CDMA paging channel structure. The paging channel carries the system overhead information and mobile station specific messages. A CDMA system uses data rate of either 4.6 or 9.6 kbps for the paging channel while WCDMA uses 16 kbps. The data is convolutionally encoded and processed by a symbol repetition and block interleaver stage. The interleaved data is passed through a data scrambler to prevent long sequences of '0's and '1's from appearing in the data stream.

Figure 2.6: Forward link paging channel [20,95]

Data scrambling is accomplished by performing the modulo-2 sum of the interleaver output with every 64<sup>th</sup> bit from a long code generator. The use of 1 out of 64 bits is called decimation. WCDMA does not use a scrambler [9]. Finally, the resultant signal is spread by a specific Walsh function assigned to that paging channel and further spread by a short PN sequence assigned to the serving sector.

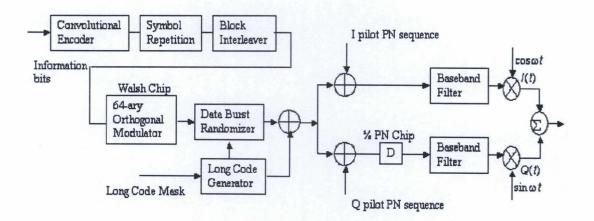

Figure 2.7: Forward link traffic channel [20,95]

2.4.1.4 Traffic channel: The traffic channel is used for the transmission of user and signaling information to a specific mobile station. The structure of the forward traffic channel is shown in Figure 2.7. The structure of the traffic channel is similar to that of the paging channel, the only difference is that traffic channel contains multiplexed power control bits. In CDMA the data and signaling bits are multiplexed together in the channel. WCDMA multiplexes the channel after the symbol repetition and always processes a separate signaling channel. A CDMA system scrambles the data using a decimated long code and multiplexes the power control bits. The multiplexed signal is then further scrambled by the decimated long code and modulo-2 added to Walsh or Hadamard codes for the channel being used.

#### 2.4.2 Reverse link

The reverse link consists of only two channels: access channel and traffic channel. Due to the noncoherent nature of the reverse link, Walsh codes are not used for channelization but PN codes are used to distinguish the signals from different mobile stations. In a WCDMA system a pilot signal, which can be recovered on either side, is sent, so Walsh or Hadamard codes are used in both directions. Figure 2.8 shows the access channel structure.

Figure 2.8: Reverse link access channel [20,95]

2.4.2.1 Access channel: The access channel is used by the mobile station to initiate communication with the base station and to respond to the paging channel messages. The channel operates at 4.8 kbps in CDMA and 16 kbps for WCDMA. The information bits are convolutionaly encoded and processed by symbol repetition and interleaving functions. In this channel the repetition and interleaving stages are different for CDMA and WCDMA [9]. In CDMA each code symbol processes through an orthogonal 64-ary modulator to generate a Walsh symbol for each input symbol, but in WCDMA, the output of the repetition stage is modulo-2 added to a Walsh code for the access channel. M-ary modulation techniques in DSCDMA is discussed in [33] and [96]. The M-ary modulator converts the incoming data symbols into complex valued symbols, the M-ary data modulator can convert m incoming data symbols into one of M  $(M=2^m)$ possible data symbols represented by K channel symbols. These can then be transmitted using binary, balanced quaternary, or complex spreading schemes. The M-ary modulator spreads the transmitted signal in the frequency domain. The orthogonally modulated data are then spread by PN sequences. Long PN codes are used to distinguish the access channel from other channels. The data is further scrambled in the I and Q paths by short PN sequences. The data in the Q path is delayed by one-half a PN chip because the reverse link uses OQPSK modulation. The ease of bit synchronization at the receiver and the fact that the difference in the time alignment in the bit stream has no impact on the output power spectral density of OQPSK are the main advantages of OQPSK over QPSK [21]. A response message or a request message are the two types of message sent over the access channel.

Figure 2.9: Reverse link traffic channel [20,95]

2.4.2.2 Traffic channel: Figure 2.9 shows the reverse link traffic channel structure. The reverse link traffic channel is used for the transmission of user and signaling information to the base station. The structure is similar to the access channel; the only difference is the data burst randomizer. The orthogonally modulated data is fed into the data burst randomizer in order to take advantage of voice activity factor on the reverse link. The data burst randomizer generates a masking pattern of '0's and '1's that randomly masks out redundant data. The output of the randomizer is then spread by the long code. The WCDMA systems do not use a randomizer.

#### 2.5 Benefits of CDMA

CDMA has gained international acceptance by wireless system providers as an upgrade from conventional wireless systems. Some of the features of the CDMA are discussed below.

- Increased capacity

- Enhanced privacy and security

- No hard handoff

- Simplified system planning reducing deployment and operating costs

- Reduced average transmitted power, thus increasing talk time for portable devices

- Improved voice quality, eliminating the audible effects of multipath fading.

- Improved coverage characteristics which reduce number of cell sites.

- Coexistence with analog systems

Because of these attractive benefits, CDMA has gained considerable attention amongst cellular providers. Due to the rapid rise in the number of cellular users in wireless communication there is a need for a system that can support a range of services such as high speed data with larger system capacity and multimedia. The most promising candidate, Wideband Code Division Multiple Access (WCDMA), is being developed throughout the world [3-4].

## 2.6 Wideband Code Division Multiple Access (WCDMA)

The continuous growth in traffic volume and emergence of new services has begun to change the structure of wireless networks. WCDMA is based on the wide band DS-CDMA technology. WCDMA systems are similar to the CDMA systems, but there are some differences in the physical layer, protocol and air interface standards. From an implementation point of view, this thesis focuses mainly on the physical layer and the interface standards. One of the main differences of WCDMA is that the Walsh or Hadamard sequences can be used in both forward and reverse directions. Fast Transmit Power Control (TPC) is another added advantage of WCDMA. However the most recent research results on wireless transmission technology have been incorporated into present WCDMA to improve performance and flexibility.

WCDMA has been chosen as the fundamental radio access technology for UMTS/IMTS-2000 in both Europe and Japan. Compared to the second generation narrow band CDMA, the WCDMA radio interface offers significant improvements, in addition to the support of higher data rate. Some important concepts of WCDMA are

the introduction of intercell asynchronous operation and pilot channels associated with individual data channels. The main technical features of WCDMA are [2,4,17]:

- 1. Fast cell search under intercell asynchronous operation: Intercell asynchronous systems can more easily realize continuous system deployment from outdoor to indoors than intercell synchronous system. This is because the previous stage does not require any external timing source such as Global Positioning System (GPS) used in IS95.

- The fast cell search under intercell asynchronous operation can be explained as follows. The control channels in the forward link of all cell sites reuse the same short spreading code and the scramble code sequence is periodically masked over one symbol duration so that the particular code appears periodically during the scramble code [17,4]. The group identification code indicating the code group, to which the scramble code of each cell site belongs, is transmitted in parallel during the masking period. The cell search algorithm detects and identifies the scramble code group and finally identifies the group identity code by cross correlating the received signal with all scramble code candidates.

- 2. Fast Transmit Power Control (TPC) on both reverse and forward links: The time-multiplexed pilot radio frame structure used in WCDMA supports Signal to Interference Ratio (SIR) measurement. The SIR is measured and compared with the target SIR to generate a TPC command which is transmitted every 0.625ms to the mobile station to raise or lower the transmit power by 1dB. Target SIR values are controlled by an outer power control loop. This outer loop measures the link quality, typically a combination of frame and its bit error rates depending on the service, and adjusts the SIR targets accordingly. This ensures that the lowest possible SIR target is used at all times resulting in maximum capacity. The outer loop is used to independently control the relative power of the different physical channels belonging to the same connection. The pilot and the data symbols are used to measure instantaneous received signal power but only pilot symbols are used to measure the interference plus background noise. Fast TPC is applied to both the reverse and forward links. The instantaneous

- SIR on each forward link varies in a random manner; this leads to the use of fast TPC that can increase the link capacity in both directions.

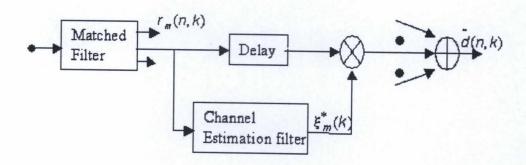

- 3. Coherent Rake Combining: Coherent detection will improve the performance of the uplink up to 3 dB compared to noncoherent reception used by the second generation CDMA system. Figure 2.10 shows a Coherent RAKE receiver structure. The matched filter resolves the frequency-selective multipath channel into M frequency non-selective propagation paths with different time delays. The output of the coherent RAKE combiner is represented at the n<sup>th</sup> symbol position of the k<sup>th</sup> slot associated with the m<sup>th</sup> propagation path, m=0,1, ---, M-1, as [17]:

$$\tilde{d}(n,k) = \sum_{m=0}^{M-1} r_m(n,k) \tilde{\xi}_m(k) \qquad -----(2.2)$$

where  $\xi_m(k)$  is the channel estimate and  $r_m(n,k)$  is the matched filter output.

Figure 2.10 Coherent RAKE receiver structure [17]

4. Coherent tracking of spreading code: A non-coherent delay-locked tracking loop suffers from tracking jitter due to the noise enhancement arising from the square-law detector. This can be overcome by using coherent delay-locked tracking loop which leads to the improvement of transmission performance [17].

CHAPTER 2 CDMA

#### 2.6.1 MAC and Radio link control

The Medium Access Protocol (MAC) and Radio Link Control (RLC) are responsible for transferring real time and non-real time services [2,4]. The transfer of non-real time data transfer includes the possibility of low-level automatic repeat requests offering higher protocol layers reliable data transfer. The MAC layer controls the multiplexing of data streams originating from different services. All the RLC protocol data units in WCDMA have the same size regardless of the transmission rate. In the case of networks, CDMA cell coverage is dependent on the cell load. WCDMA employs admission control and congestion, so the cell load and thus coverage can be controlled.

#### 2.7 Summary

In order to provide global roaming the standardization of third generation mobile communications systems is now rapidly progressing all over the world. These systems, called International Mobile Telecommunications-2000 (IMT2000) in the International Telecommunication Union (ITU), will extend the services provided by second generation systems. Standardization of service capabilities includes standardization of bearers, quality of service parameters and additional mechanisms needed to realize the required services. These additional mechanisms include the service creation functionality of various network elements and the communication between element and the storage of associated data. Such standardized service capabilities should provide a defined platform which will enable support of speech, video, multimedia, access to Internet, messaging, data etc. A set of service capabilities should enable users, service providers and network operators to define services themselves according to their needs. WCDMA promises flexibility, provision for multirate services, packet data, and seamless interfrequency handover. The proposed air interface standard and the technical parameters of WCDMA are summarized in Table 2.2 [2-5,8]. Since there are so many possible combinations of settings, Table 2.3 show the parameters used in this thesis.

| Channel Bandwidth         |                      | 5,10,20 MHz                                       |  |  |

|---------------------------|----------------------|---------------------------------------------------|--|--|

| Chip rate                 |                      | 4.096/8.192/16.384 Mcps                           |  |  |

| Multiple Access           |                      | DS-CDMA                                           |  |  |

| Roll-off factor           |                      | 0.22                                              |  |  |

| 293                       | Variable-rate speech | 10 or 20 ms                                       |  |  |

| Frame length              | Packet data          | 10-80 ms                                          |  |  |

| Modulation                | Spreading            | Balanced QPSK (downlink)                          |  |  |

|                           |                      | Dual channel QPSK (Uplink)                        |  |  |

|                           |                      | Complex spreading circuit                         |  |  |

|                           |                      | QPSK (downlink)                                   |  |  |

|                           | Data                 | BPSK (uplink)                                     |  |  |

| Coherent detection        |                      | Pilot symbol assisted                             |  |  |

| Channel coding            |                      | Convolutional and Turbo coding                    |  |  |

| Scrambling code           |                      | 10 ms                                             |  |  |

| Interleaving              |                      | 10/20/40/80 ms                                    |  |  |

| Multirate                 |                      | Variable spreading and multicode                  |  |  |

| Spreading factor          | r                    | 4-256 (4.096Mchips/s)                             |  |  |

|                           |                      | Variable length orthogonal sequences for          |  |  |

| Spreading                 | Downlink             | channel separation                                |  |  |

|                           |                      | Gold sequence for user and cell separation        |  |  |

|                           | Uplink               | Variable length orthogonal sequences for          |  |  |

|                           |                      | channel separation                                |  |  |

|                           |                      | Gold sequence 2 <sup>41</sup> for user separation |  |  |

| Handover                  |                      | Soft handover                                     |  |  |

|                           |                      | Interfrequency handover                           |  |  |

| Power control             |                      | Open and fast closed loop (1600 Hz)               |  |  |

| Power control s           | tep size             | 0.25-1.5 dB                                       |  |  |

| Inter base station timing |                      | Asynchronous                                      |  |  |

Table 2.2: Parameters of WCDMA

| Processing Gain    |           | 32x0.5x3                                 |                           |            |  |

|--------------------|-----------|------------------------------------------|---------------------------|------------|--|

| Modulation         | Data      | QPSK                                     |                           |            |  |

|                    | Spreading | QPSK                                     |                           |            |  |

| Channel Coding     |           | Convolutional Coding, R=1/3, K=9         |                           |            |  |

| Frame Structure    |           | _                                        | Pilot                     | 4 symbols  |  |

|                    |           |                                          | Data                      | 76 symbols |  |

|                    |           | Frame                                    | Frame 0.625 ms X 16 Slots |            |  |

| Chip Rate          |           | 4.096 Mcps                               |                           |            |  |

| Interleaving       |           | 10ms                                     |                           |            |  |

| Spreading Code     |           | Gold Code                                |                           |            |  |

| Channel Estimation |           | Linear Interpolation                     |                           |            |  |

| Demodulation       |           | Pilot symbol assisted coherent detection |                           |            |  |

| Channel decoding   |           | Soft-decision Viterbi decoding           |                           |            |  |

Table 2.3: Link parameters used for simulation

#### 2.8 Conclusion

This chapter covered the fundamental principles of spread spectrum systems and for the implementation aspect, focused on the physical layer of IS-95 CDMA and underlying differences in the physical layer between CDMA and WCDMA. A summary of WCDMA parameters and an overview of air interface standards were also discussed. WCDMA technology provides improved capacity and coverage due to the wider bandwidth and coherent uplink. The possibility of asynchronous operation and refined radio-network algorithms will further reduce the deployment cost of WCDMA. WCDMA systems support full utilization of adaptive antennas through the use of dedicated pilot symbols on both uplink and downlink thus leads to further improvement in the network and its traffic capacity. To conclude, WCDMA is a promising technology, ready to provide the basis for a true third generation mobile communications system with full multimedia capabilities.

# Chapter 3

# Antenna Arrays

#### 3.1 Introduction

An antenna is usually defined as the structure associated with the region of transition between the guided wave and free space or vice versa. The antenna plays a vital role in modern mobile communication systems, especially in the case of increased antenna gain, which increases received signal strength.

A single antenna element has low values of directivity (gain). A practical objective of directive communication is an improvement in the received signal as measured relative to the prevailing noise. At the receive end of the communication link, the increase in directivity means that the antenna receives less interference from its signal environment. The directivity improves the Signal-to-Noise Ratio (SNR). One useful method of achieving directive antenna characteristics is an arrangement of several individual antennas of the same kind so spaced and phased that their individual contributions add in one preferred direction while they cancel in others. This type of arrangement is known as an antenna array. The individual antenna in an array is called an element. An array can be arranged in various configurations such as straight line, circle, square, arc, etc.

An array that consists of a number of equally spaced individual antennas set up along a straight line is called a linear array, while two-dimensional planar arrays consist of elements oriented on a geometric grid in a plane. Rectangular arrays may be thought as

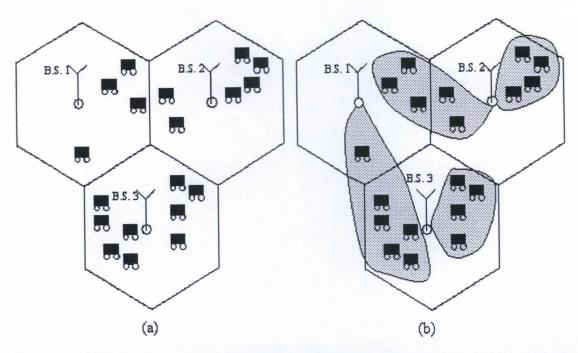

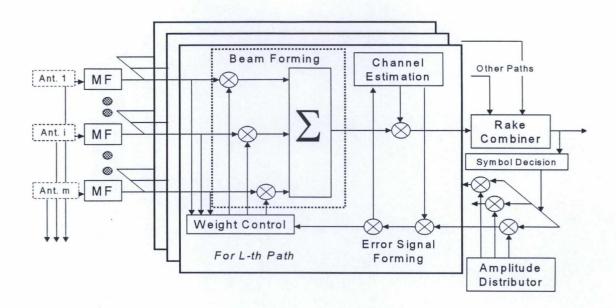

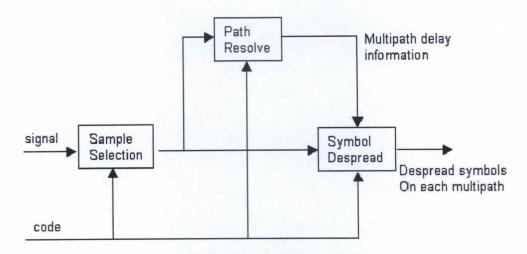

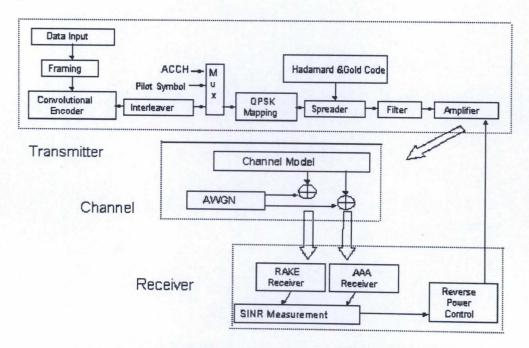

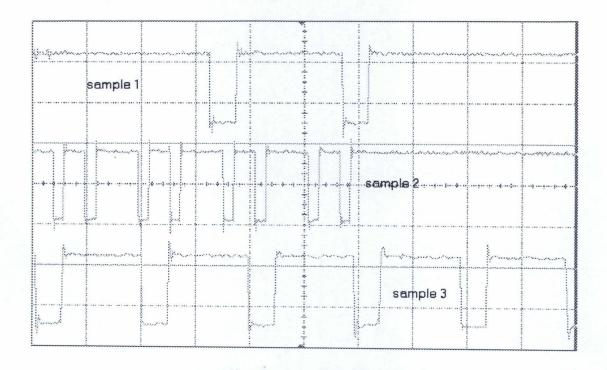

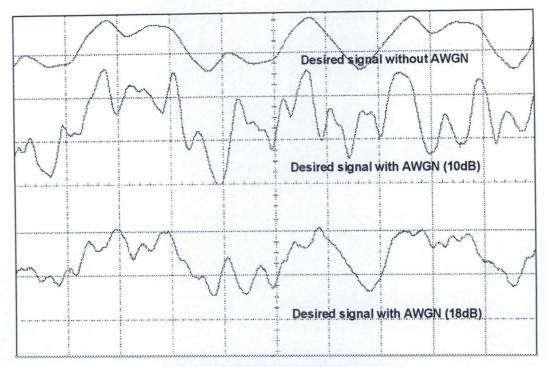

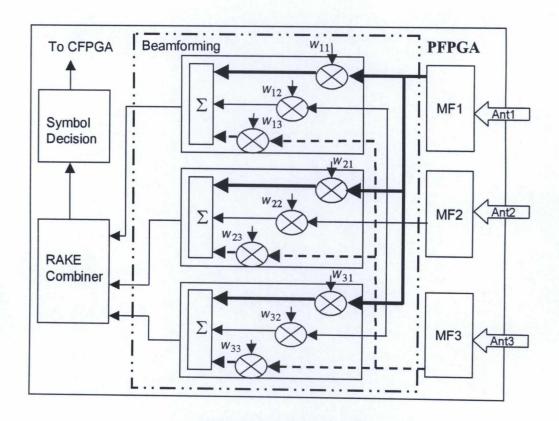

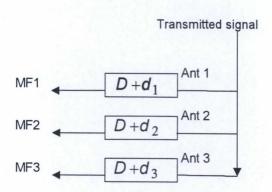

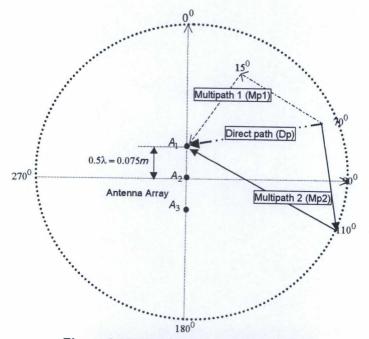

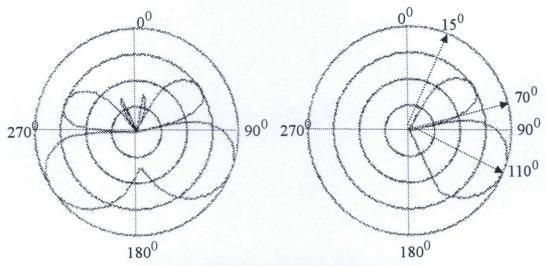

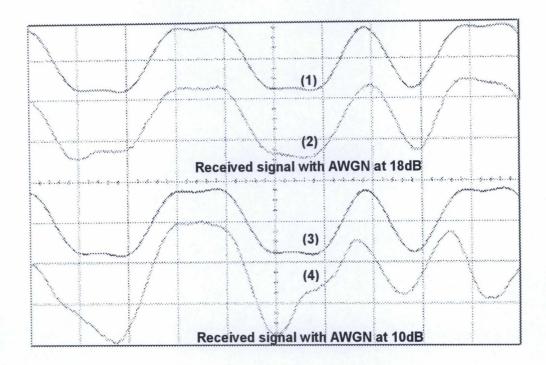

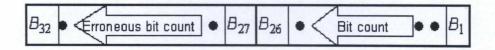

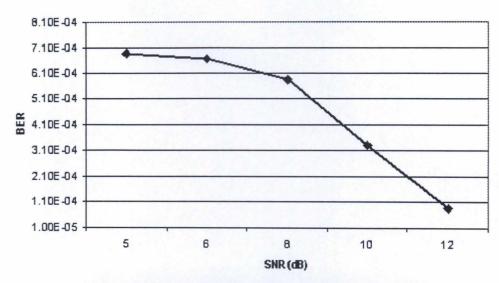

a set of linear arrays placed next to each other, equally spaced, forming a twodimensional array. In this thesis, the proposed receiver makes use of a linear array with six antenna elements.