# MODELLING AND ANALYSIS OF INVERTER-BASED FACTS DEVICES FOR POWER SYSTEM DYNAMIC STUDIES

by

FENG-WEI (FRED) HUANG (BScEng)

Submitted in fulfillment of the academic requirements for the degree of Doctor of Philosophy, in the School of Electrical, Electronic and Computer Engineering, University of KwaZulu-Natal, Durban, South Africa.

December 2006

I hereby declare that all the material incorporated into this thesis is my own original and unaided work except where specific reference is made by name or in the form of a numbered reference. The work contained herein has not been submitted for a degree at any other university.

Signed:

F-W Huang

for my family

## **ABSTRACT**

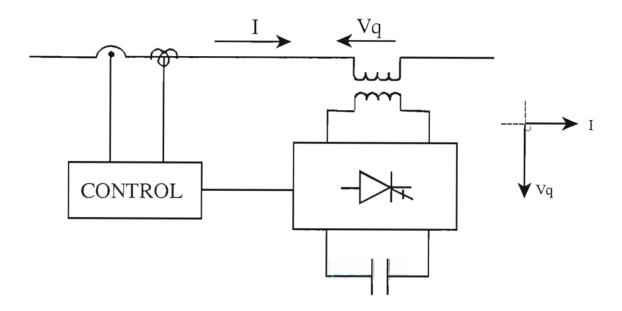

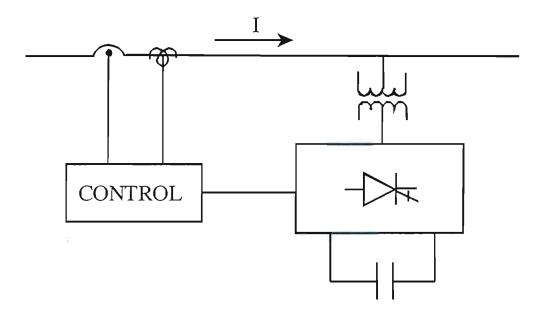

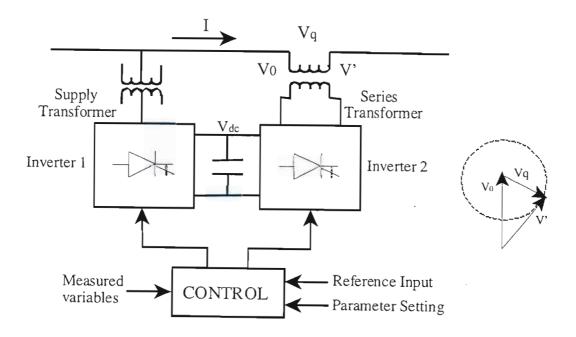

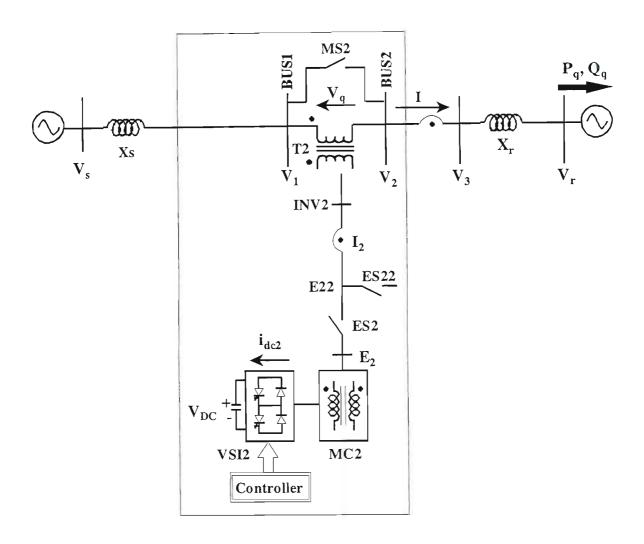

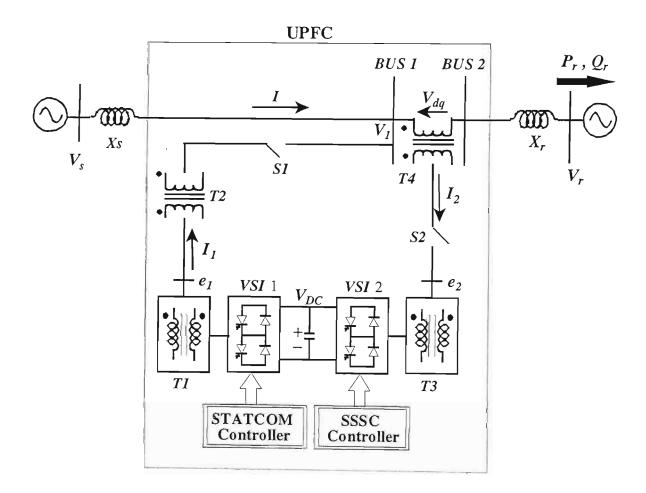

Flexible AC Transmission Systems (FACTS) involves the incorporation of power-electronic controlled devices into ac power transmission systems in order to extend the power-transfer capability of these systems beyond their traditionally accepted boundaries. One particular category of FACTS devices makes use of high-powered voltage source inverters to insert near-sinusoidal ac compensating voltages into the transmission system. This thesis considers this particular category of inverter-based FACTS devices, namely the static synchronous compensator (STATCOM), static synchronous series compensator (SSSC) and unified power flow controller (UPFC).

Although the potential for FACTS devices to enhance the operation of power systems is well known, a device such as a UPFC is itself a complicated subsystem of the overall power system. There is therefore also the possibility that the introduction of such devices could cause adverse interactions with other power system equipment or with existing network resonances. This thesis examines the interactions between inverter-based compensators and a particular form of system resonance, that of subsynchronous resonance between a generator turbine shaft and the electrical transmission network.

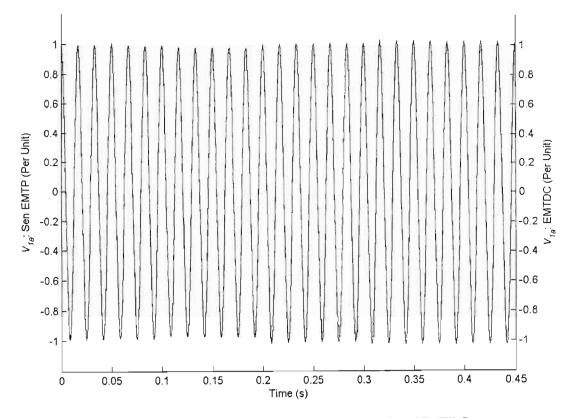

The thesis presents a review of the theory of operation of high-power, multi-pulse inverter topologies actually used in transmission-level FACTS devices. Detailed simulation models are developed of both two-level and three-level multi-pulse inverters. With appropriate controls, simulation models of both the SSSC and STATCOM, and a full UPFC are then developed using these detailed inverter models and the results from these simulation models compared against other results from the literature. These comparisons show favourable agreement between the detailed FACTS models developed in the thesis and those used by other researchers. However, the models presented in this thesis include a more detailed representation of the actual power-electronic circuitry and firing controls of inverter-based FACTS devices than is the case with other models used in the literature.

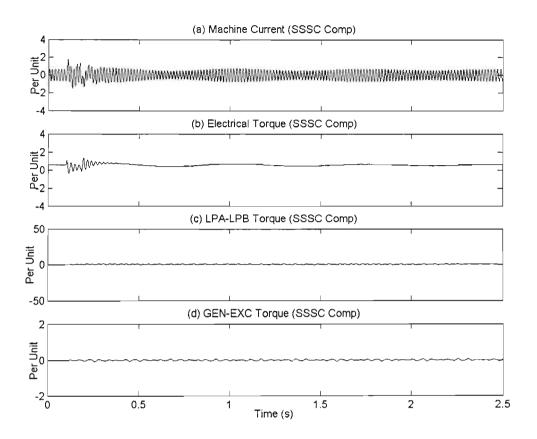

The thesis then examines the issue of whether the introduction of an SSSC to a transmission system could cause subsynchronous resonance (SSR). SSR is a form of dynamic instability that arises when electrical resonances in a series capacitively compensated transmission line interact with the mechanical resonances of a turbo-generator shaft system. The detailed SSSC simulation model developed in the thesis is used to determine the impedance versus frequency

characteristics of a transmission line compensated by an SSSC. The results confirm earlier work by others, this time using more detailed and realistic models, in that the introduction of an SSSC is shown to cause subsynchronous resonance.

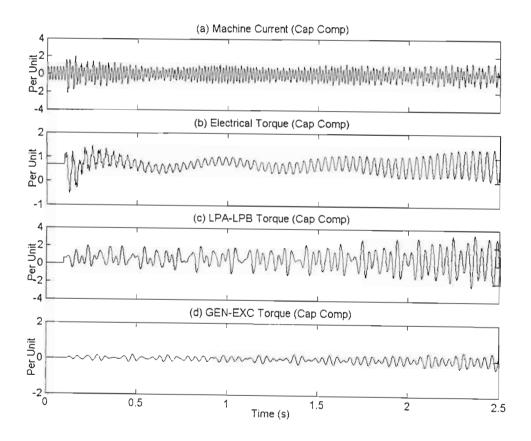

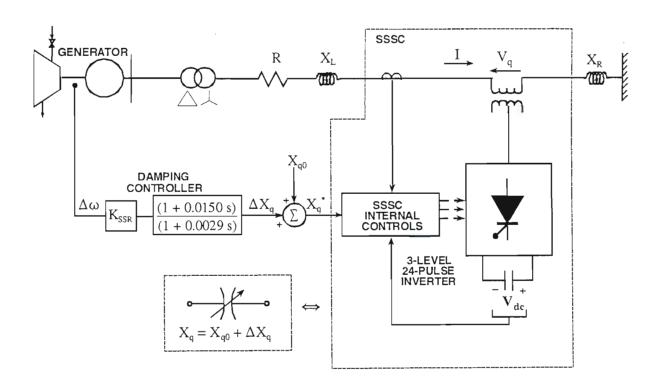

The thesis then considers the addition of supplementary damping controllers to the SSSC to reduce subsynchronous oscillations caused both by the SSSC itself as well as by a combination of conventional series capacitors and an SSSC in a representative benchmark study system. The results show that subsynchronous oscillations in the transmission system compensated solely by an SSSC can successfully be damped out using a single-mode supplementary damping controller for a range of values of SSSC series compensation. However, in the case of the transmission system compensated by both conventional series capacitors and an SSSC, the nature of the subsynchronous oscillations is shown to be complex and strongly multi-modal in character. The thesis then proposes an extension to the single-mode supplementary damping controller structure that is better suited to damping the multi-modal resonances caused when an SSSC and conventional series capacitors are used together to compensate a transmission line. The results obtained from this multi-modal controller indicate that it is able to stabilise SSR for a range of compensation values, but that the controller design needs to be adjusted to suit different values of compensation.

## **ACKNOWLEDGEMENTS**

The work presented in this thesis was carried out under the supervision of Professor Bruce S Rigby and Professor Ronald G Harley, both of the Department of Electrical Engineering, University of KwaZulu-Natal, Durban. I wish to thank Professor Rigby for his constant support, patient guidance, and co-operation throughout the course of this thesis, and for his commendable efforts during the correction of this document. I also wish to thank Professor Harley for believing in me and for arranging much needed financial support.

In addition I should like to thank:

my family for their patience, support and love;

my friends for their encouragement, understanding and simply being there for me;

my postgraduate friends for their assistance and co-operation, and who have together contributed towards a friendly and stimulating work environment over the years.

the National Research Foundation in South Africa, the University of KwaZulu-Natal, and ESKOM TESP for providing financial support.

| 2.3 | The 6-Pulse Three-Level Inverter                                       | 30. |

|-----|------------------------------------------------------------------------|-----|

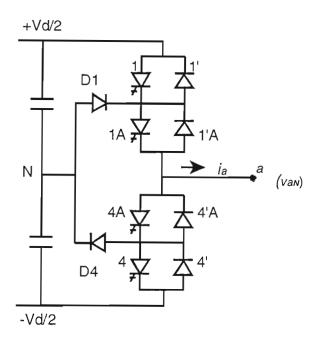

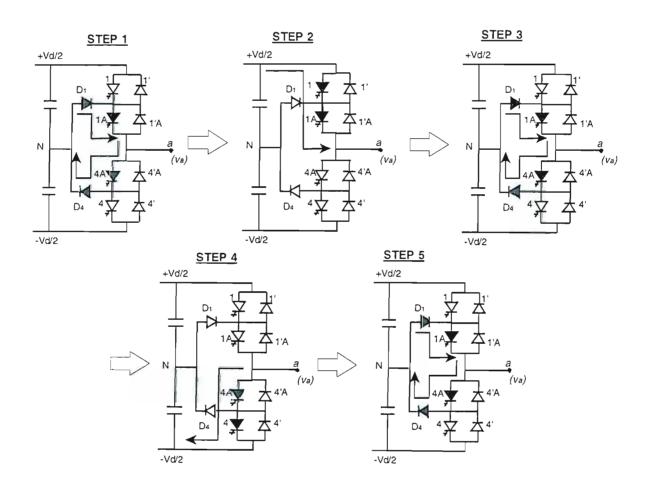

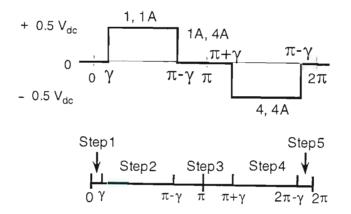

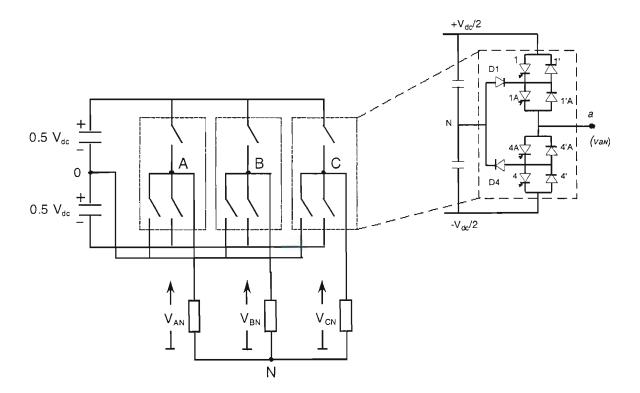

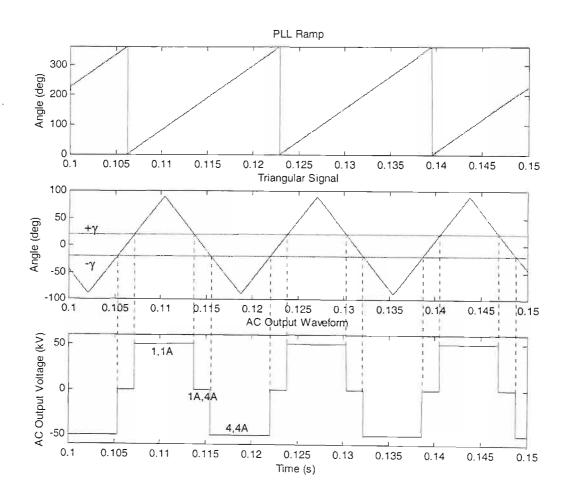

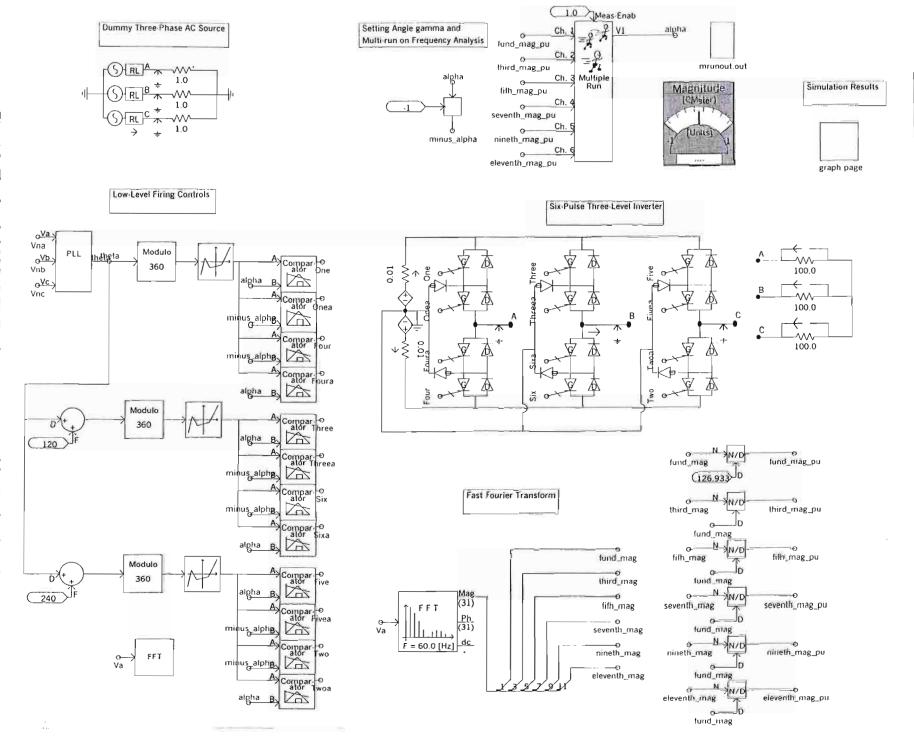

|     | 2.3.1 The Topology And Operation Of The 6-Pulse Three-Level Inverter   | 30  |

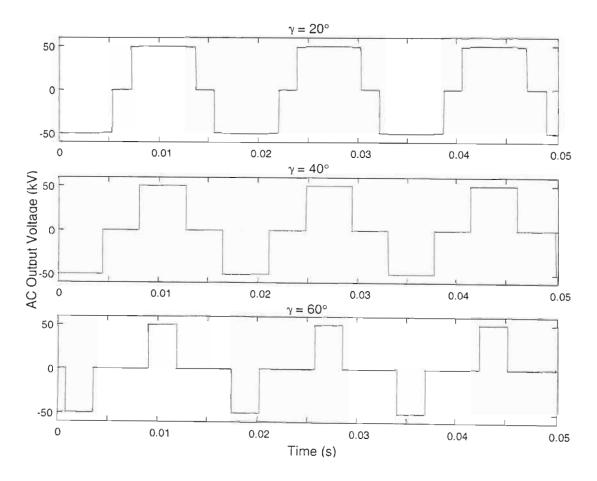

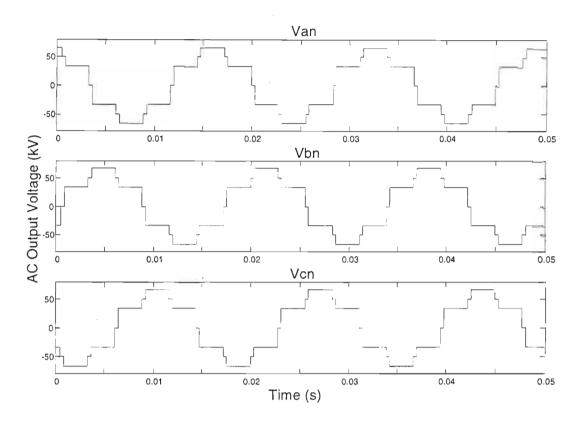

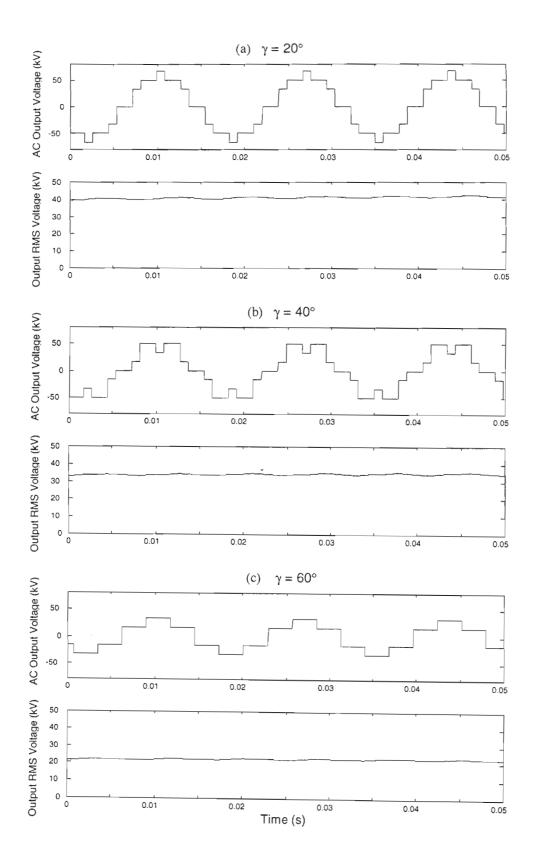

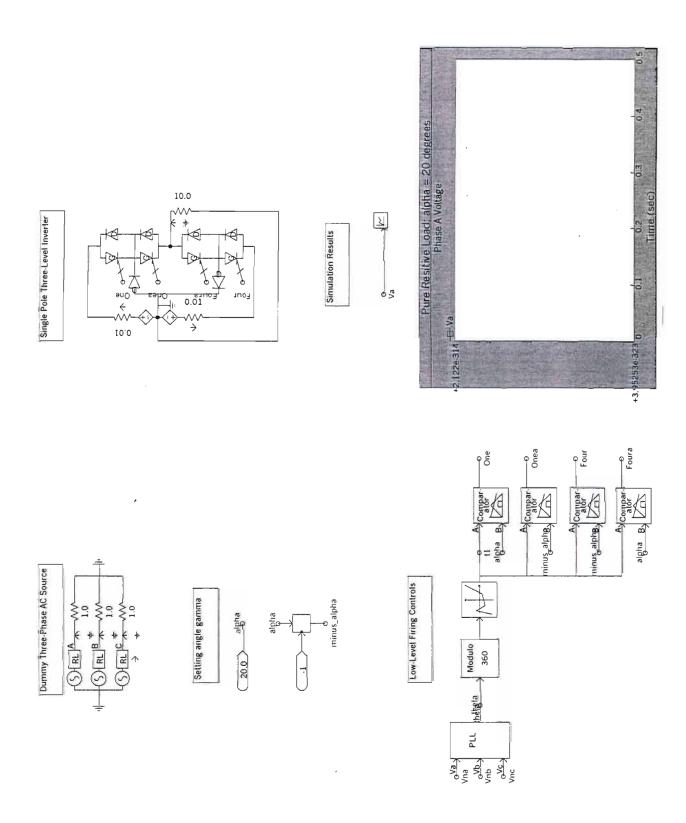

|     | 2.3.2 Time-Domain Simulation Results From PSCAD/EMTDC 31               |     |

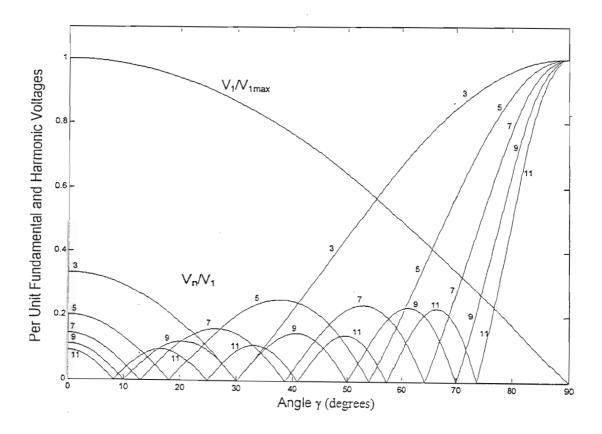

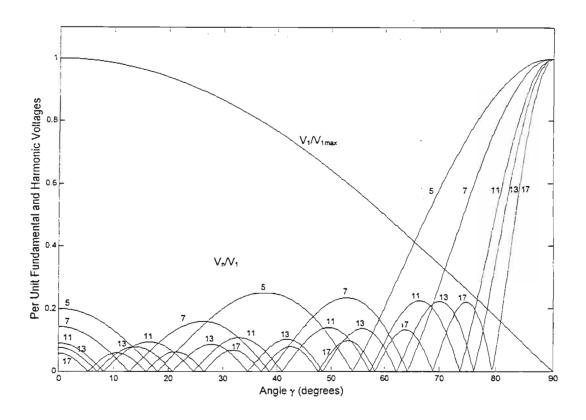

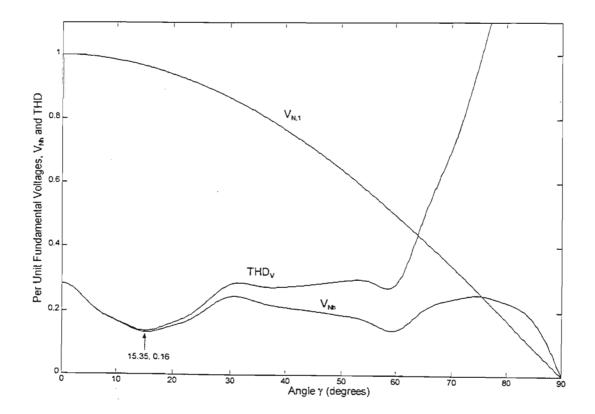

|     | 2.3.3 The Frequency-Domain Characteristics Of The 6-Pulse Three-Level  |     |

|     | Inverter 34                                                            |     |

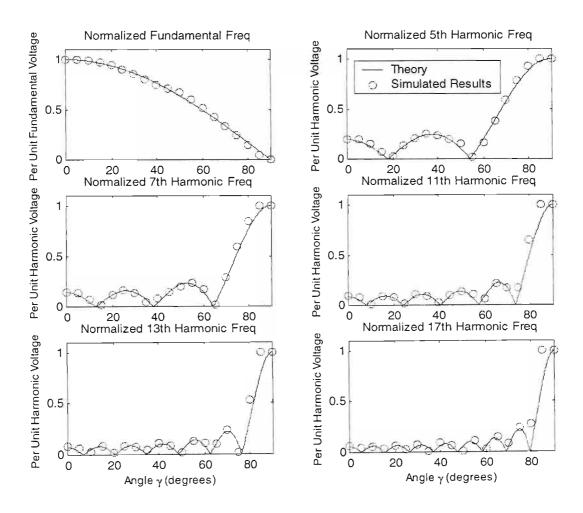

|     | 2.3.4 Frequency-Domain Characteristics From PSCAD/EMTDC Simulation     | l   |

|     | Model 38                                                               |     |

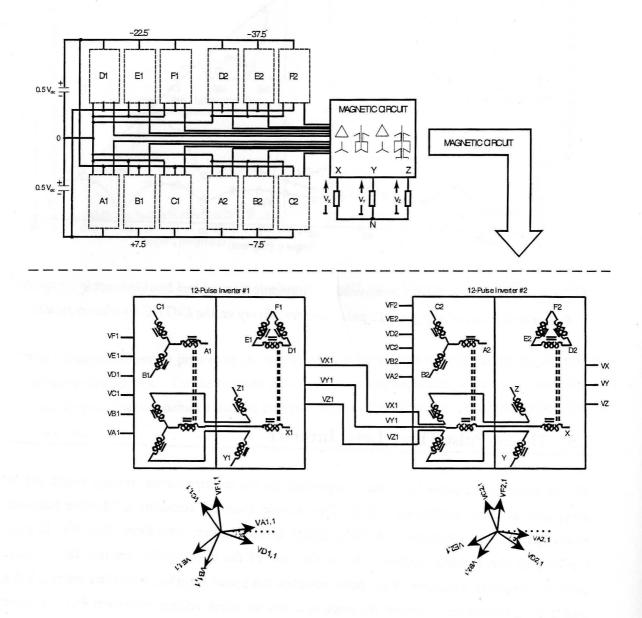

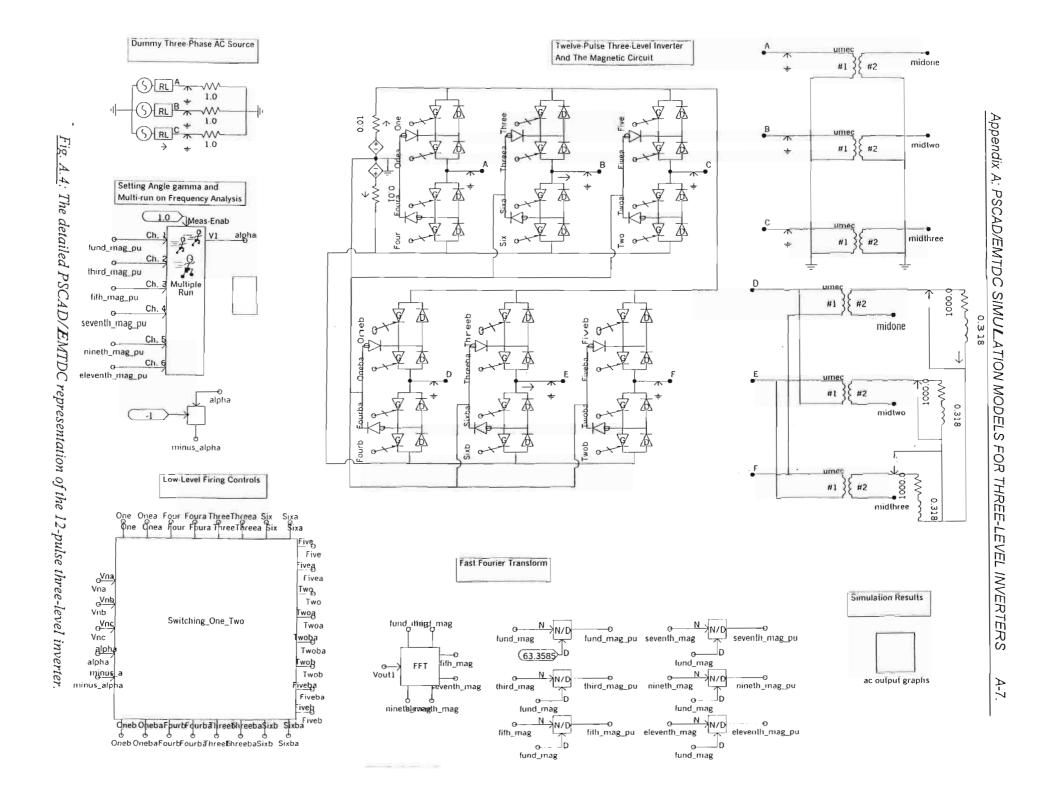

| 2.4 | The 12-Pulse Three-Level Inverter                                      | 40. |

|     | 2.4.1 The Topology And Operation Of The 12-Pulse Three-Level Inverter  | 40  |

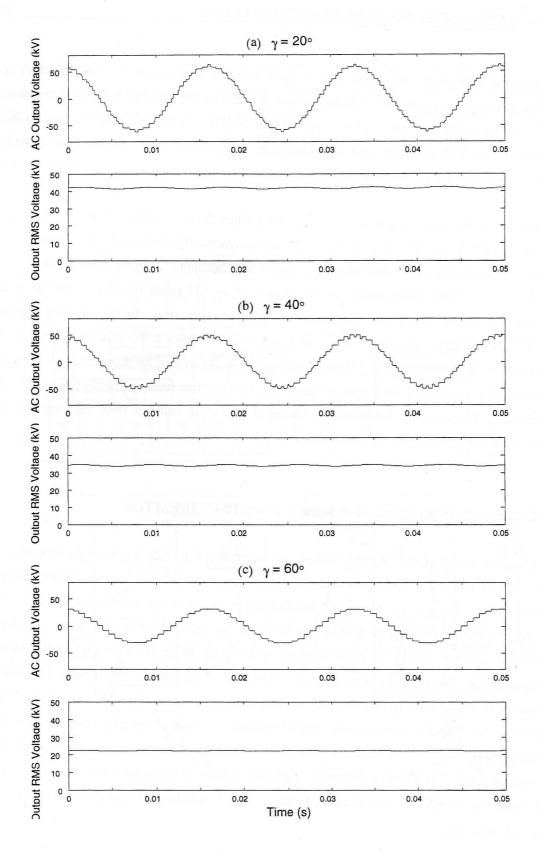

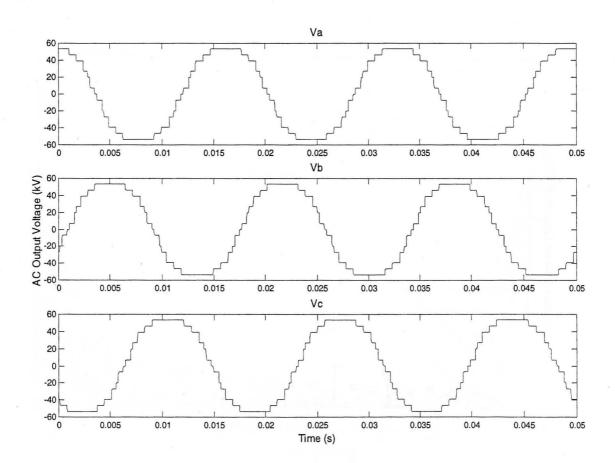

|     | 2.4.2 Time-Domain Simulation Results From PSCAD/EMTDC 42               |     |

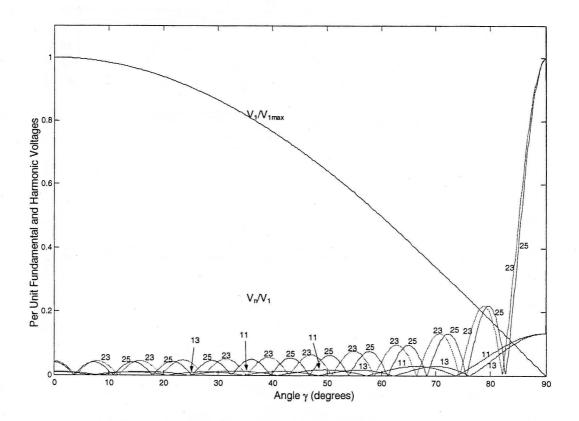

|     | 2.4.3 The Frequency-Domain Characteristics Of The 12-Pulse Three-Level |     |

|     | Inverter 45                                                            |     |

|     | 2.4.4 Frequency-Domain Characteristics From PSCAD/EMTDC Simulation     |     |

|     | Model 47                                                               |     |

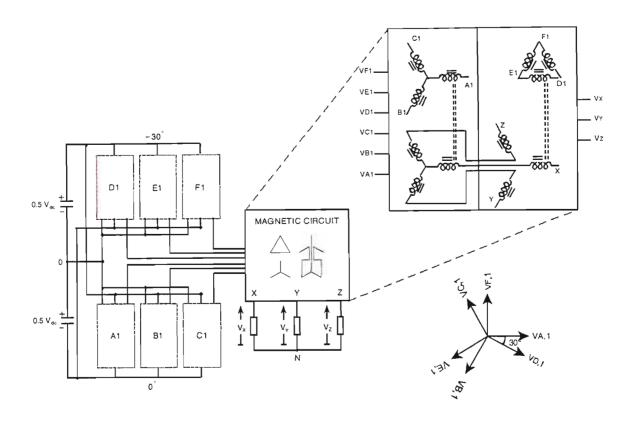

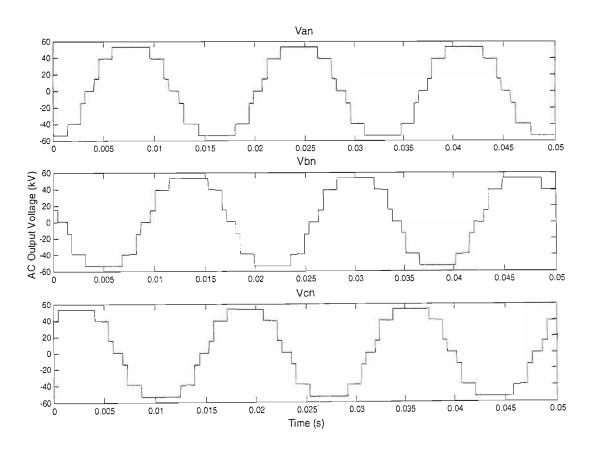

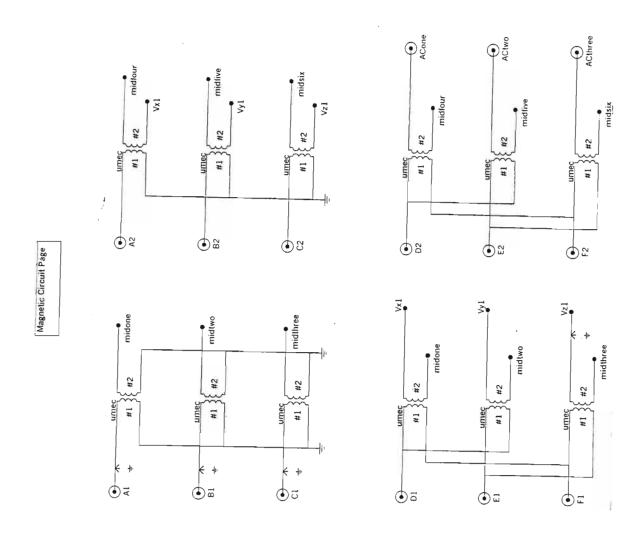

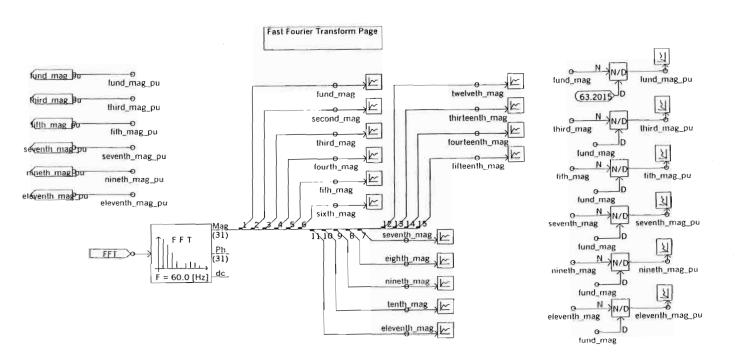

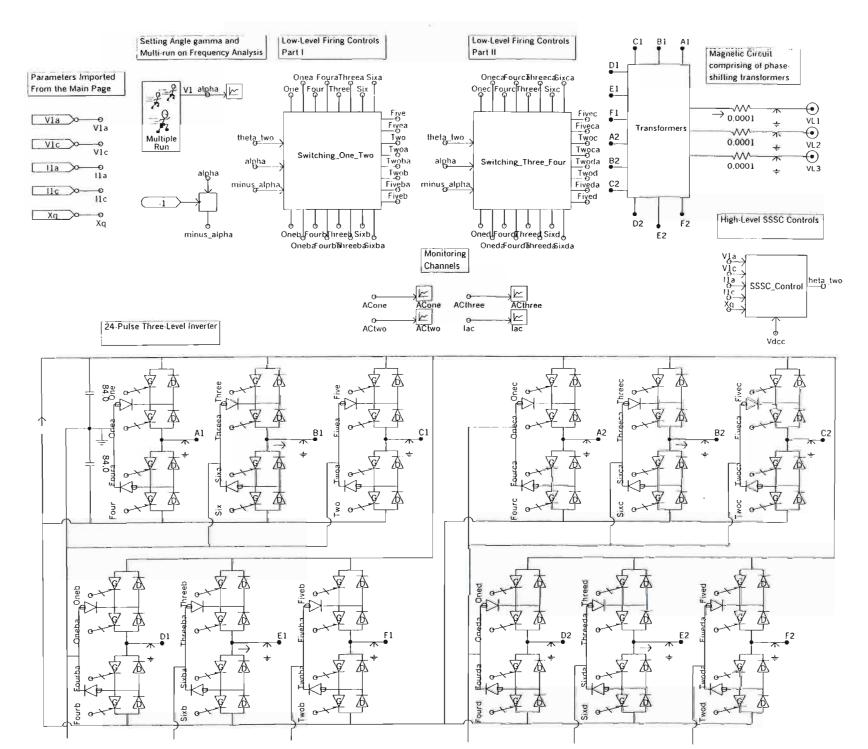

| 2.5 | The 24-Pulse Three-Level Inverter                                      | 49. |

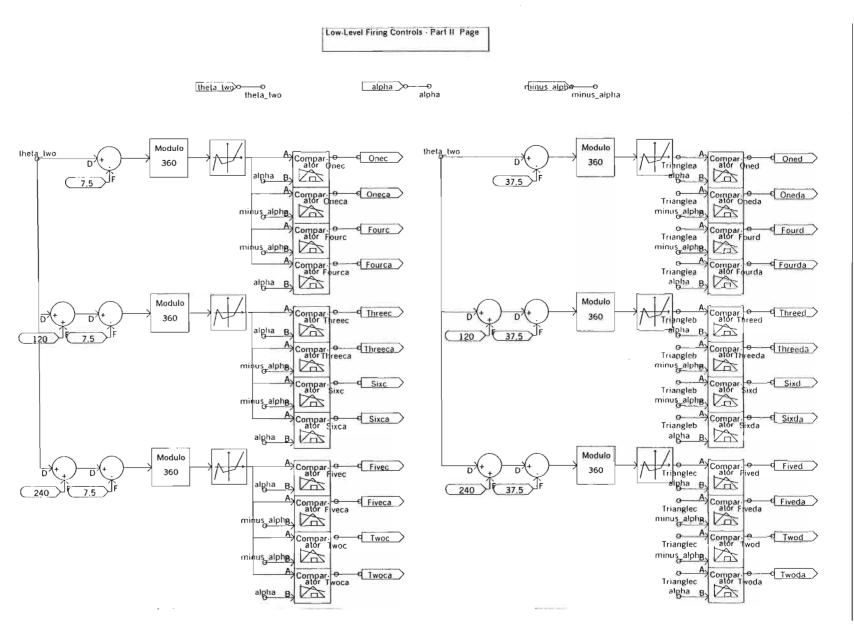

|     | 2.5.1 The Topology And Operation Of The 24-Pulse Three-Level Inverter  | 49  |

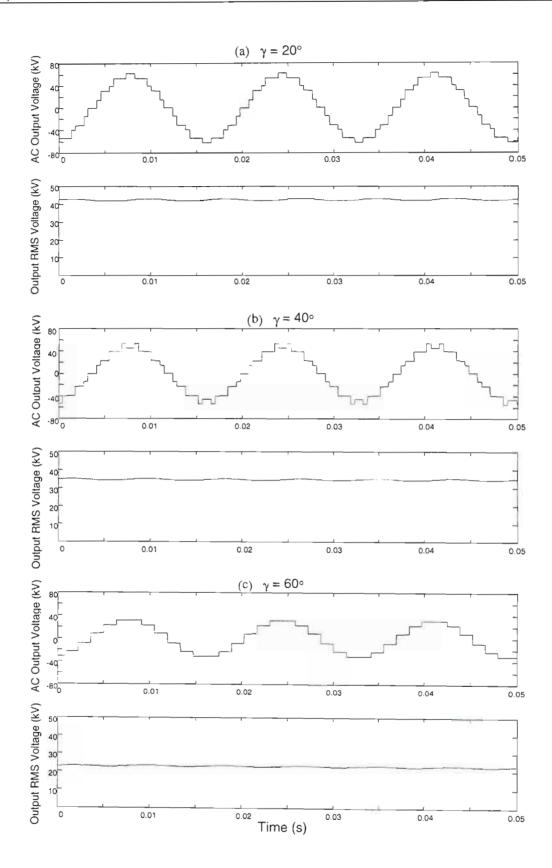

|     | 2.5.2 Time-Domain Simulation Results From PSCAD/EMTDC 51               |     |

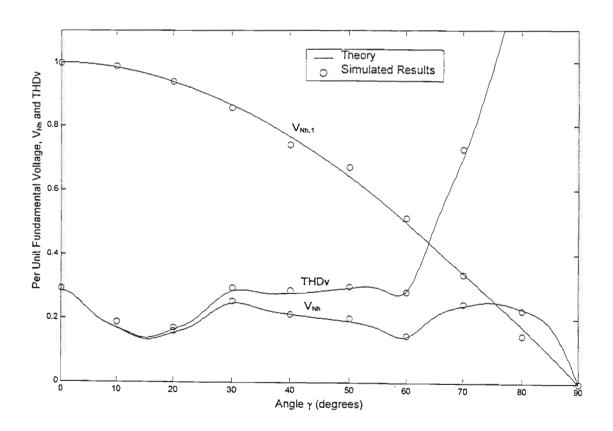

|     | 2.5.3 The Frequency-Domain Characteristics Of The 12-Pulse Three-Level |     |

|     | Inverter 54                                                            |     |

|     | 2.5.4 Frequency-Domain Characteristics From PSCAD/EMTDC Simulation     |     |

|     | Model 56                                                               |     |

| 2.6 | Conclusion                                                             | 58. |

|     |                                                                        |     |

|     |                                                                        |     |

| CH  | APTER THREE: THE 24-PULSE INVERTER BASED SSS                           | 2   |

|     |                                                                        |     |

| 3.1 | Introduction                                                           | 60. |

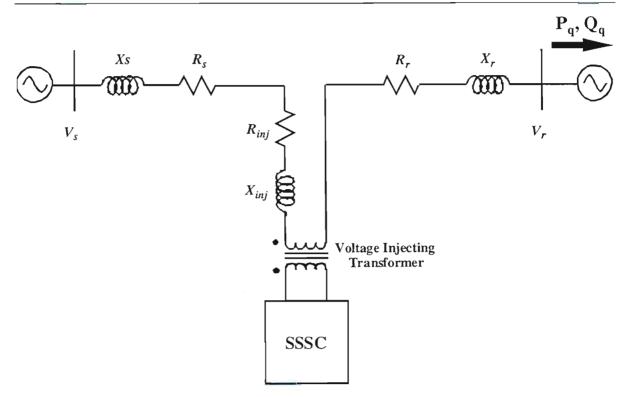

| 3.2 | The 24-Pulse Two-Level Inverter Based SSSC                             | 61. |

|     | 3.2.1 Introduction 61                                                  | 01. |

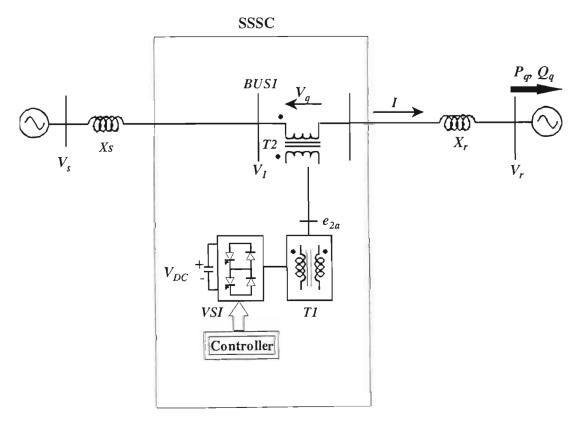

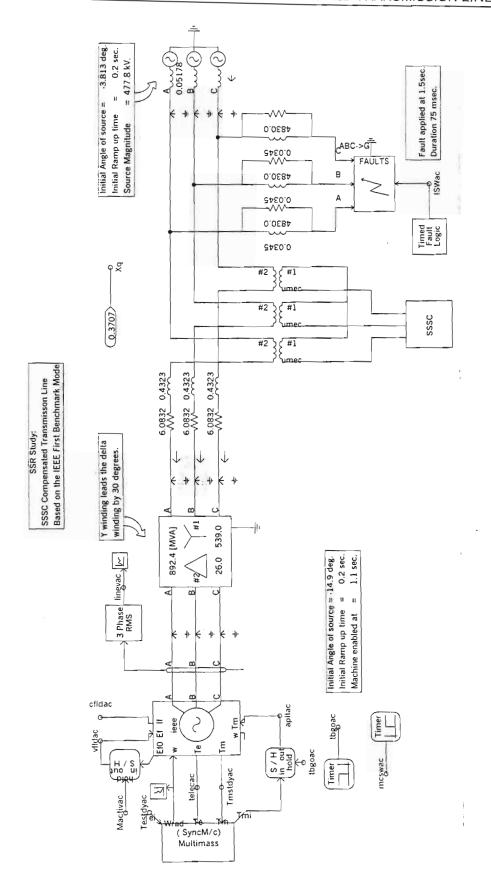

|     | 3.2.2 The SSSC And Transmission System Layout 62                       |     |

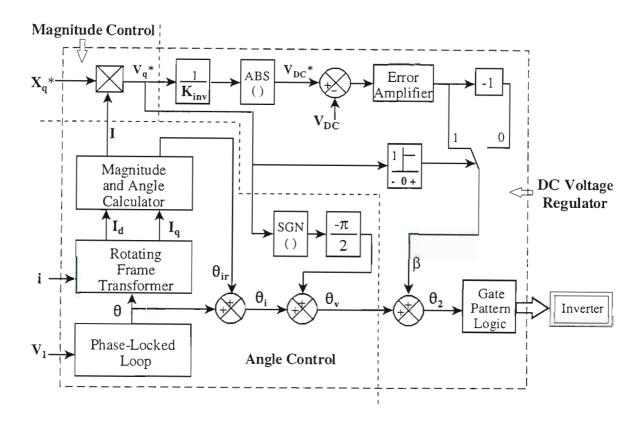

|     | 3.2.3 The SSSC Controller 63                                           |     |

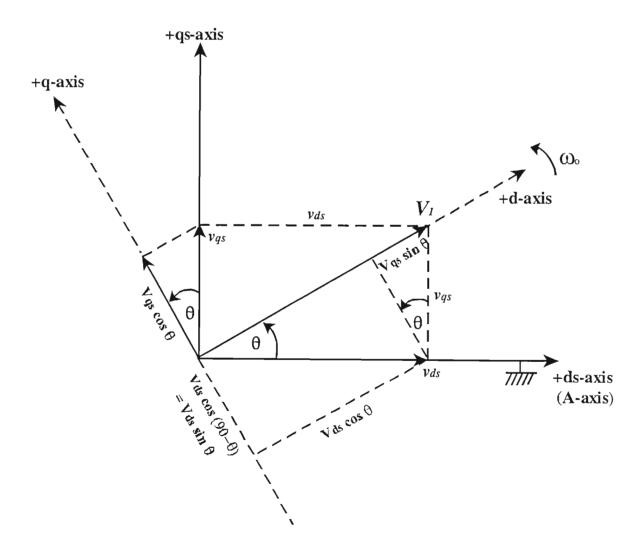

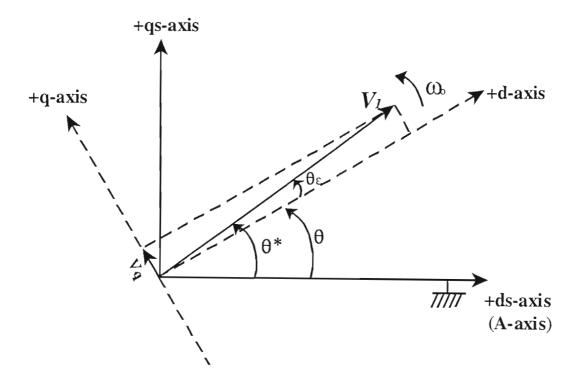

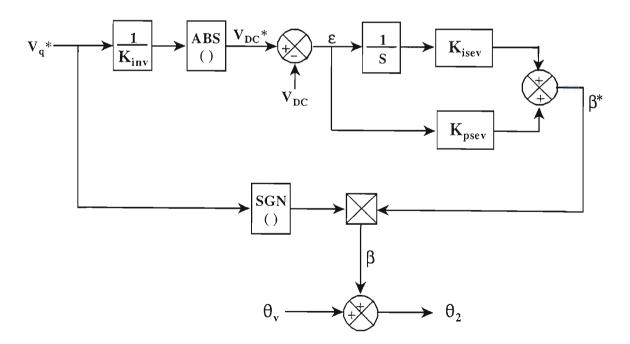

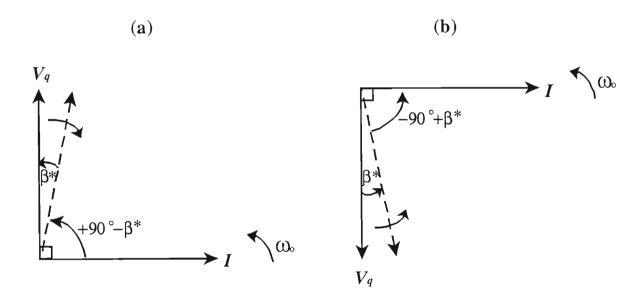

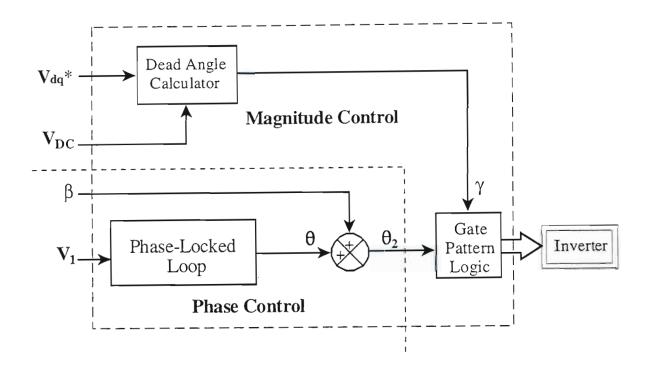

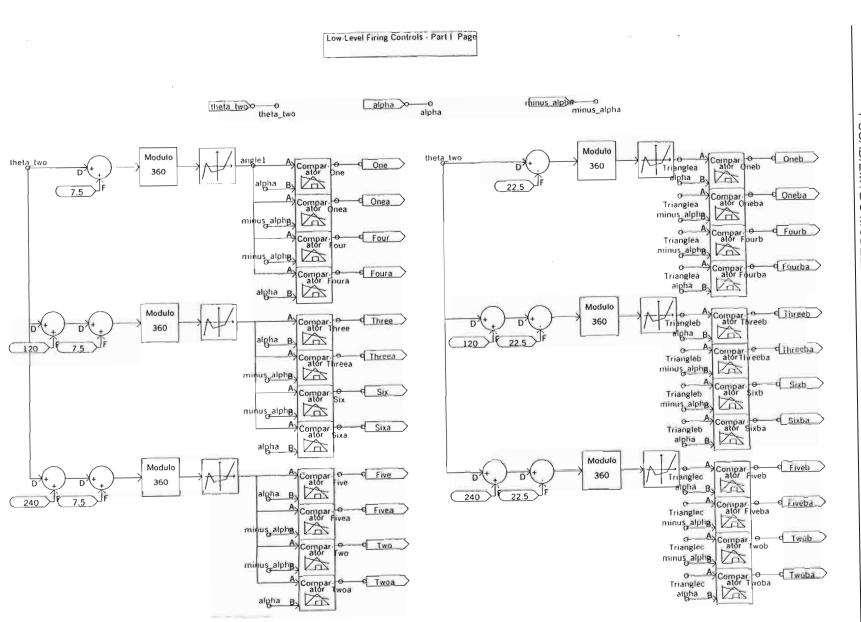

|     | 3.2.3.1 Angle Control Of Injected Voltage 64                           |     |

|     | - Phase Locking of the Injected Voltage Vector $V_q$ 64                |     |

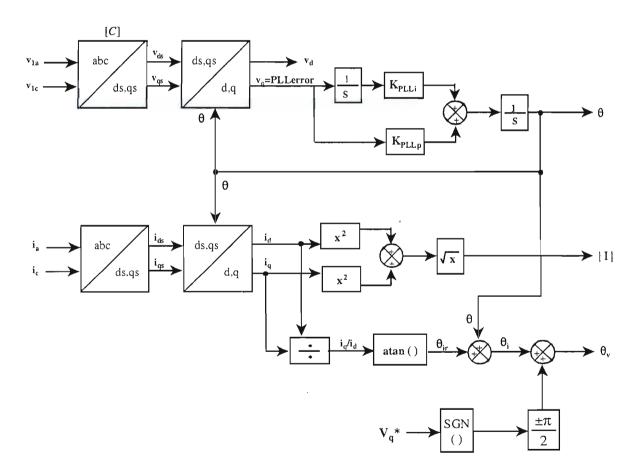

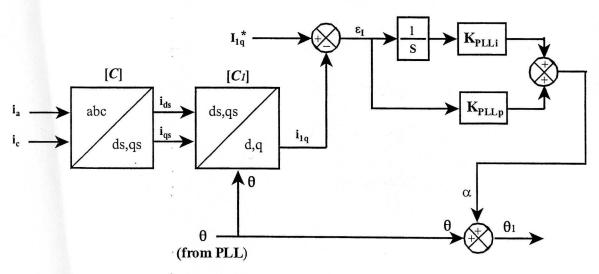

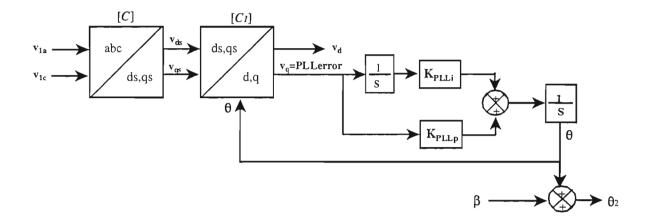

|     | <ul> <li>The Phase Locked Loop (PLL) 68</li> </ul>                     |     |

|     | <ul> <li>Line Current I in the d-q Frame 70</li> </ul>                 |     |

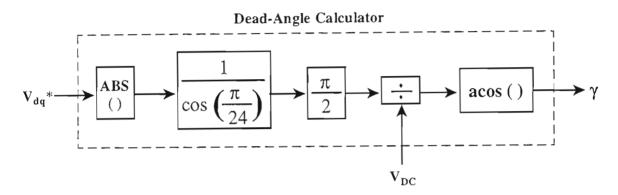

|     | 3.2.3.2 Amplitude Of The Compensating Voltage 72                       |     |

|     | 3.2.3.3 Inverter DC Voltage Regulator 72                               |     |

|     | The stange regulator /2                                                |     |

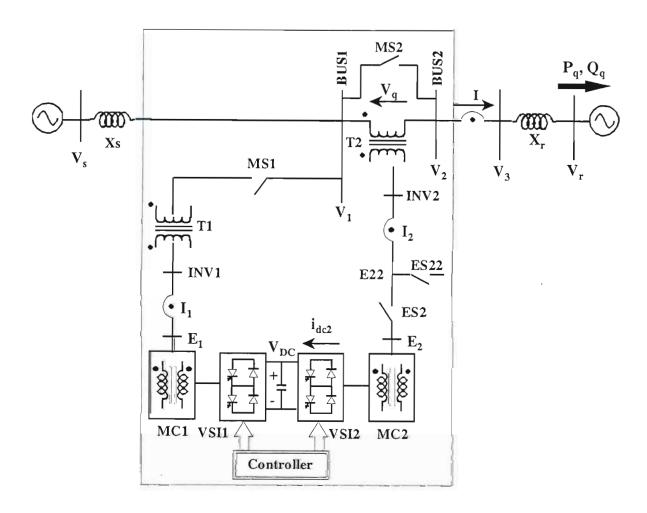

|         | 4.3.3 UPFC Simulation Model In PSCAD/EMTDC 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|         | 4.3.4 UPFC Benchmark Results 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 124.                                                      |

| 4.4     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 124.                                                      |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           |

| CH      | HAPTER FIVE: CONTINUOUS-TIME MODEL OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | c FOD                                                     |

|         | INVERTER-BASED FACTS DEVICE PSCAD/EMTDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S FOR                                                     |

| 5.1     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 126.                                                      |

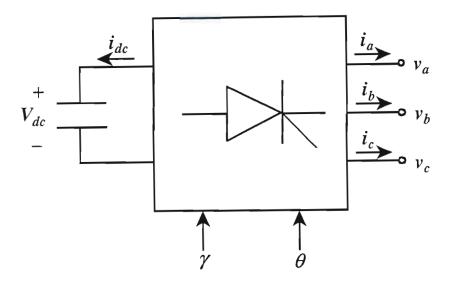

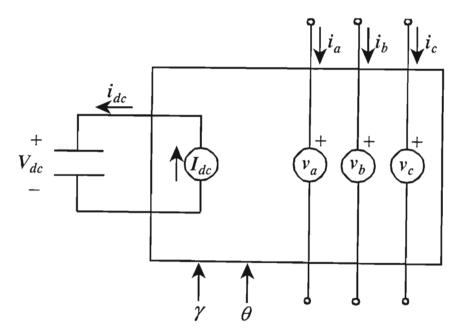

| 5.2     | Continuous-Time Model Of Voltage-Sourced Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 127.<br>129.                                              |

| 5.3     | TO THE PROPERTY OF THE PROPERT |                                                           |

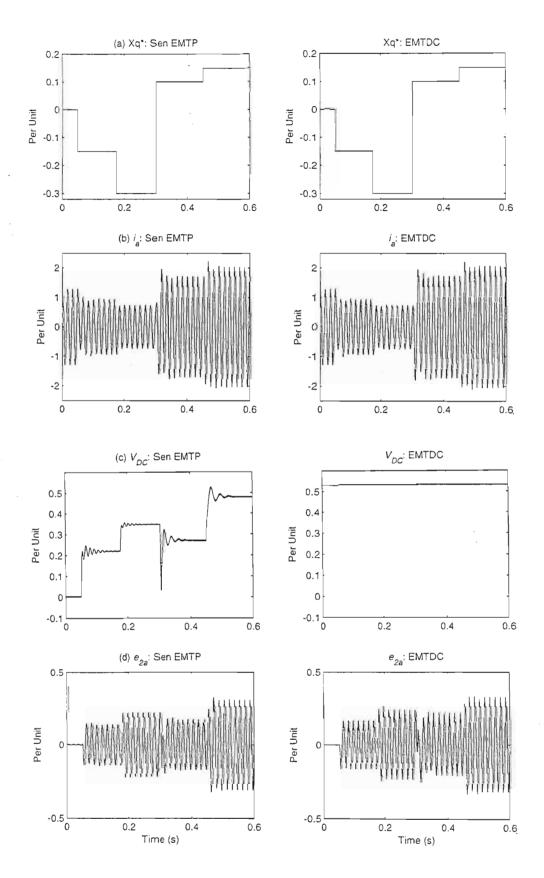

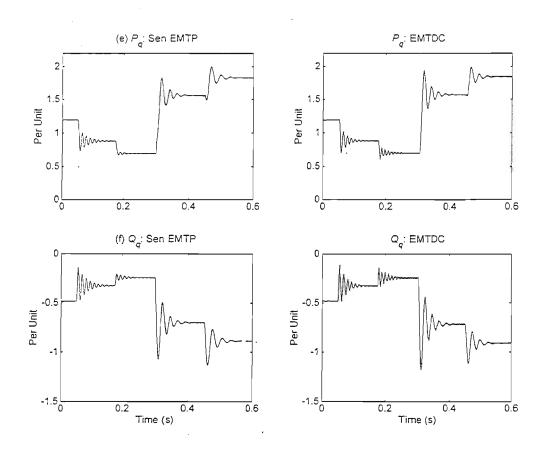

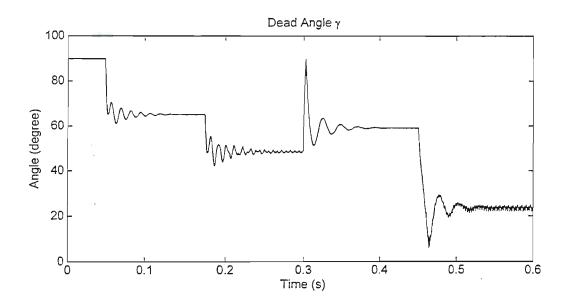

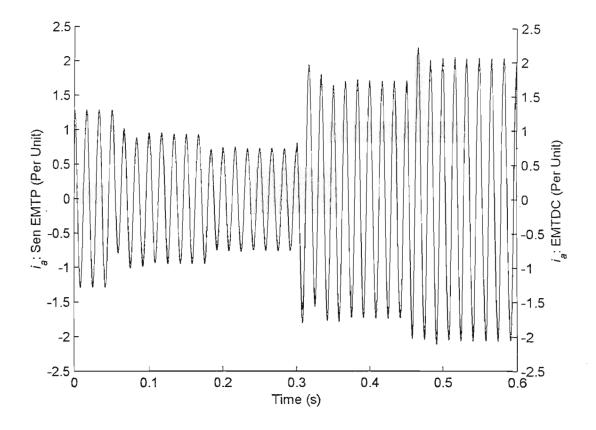

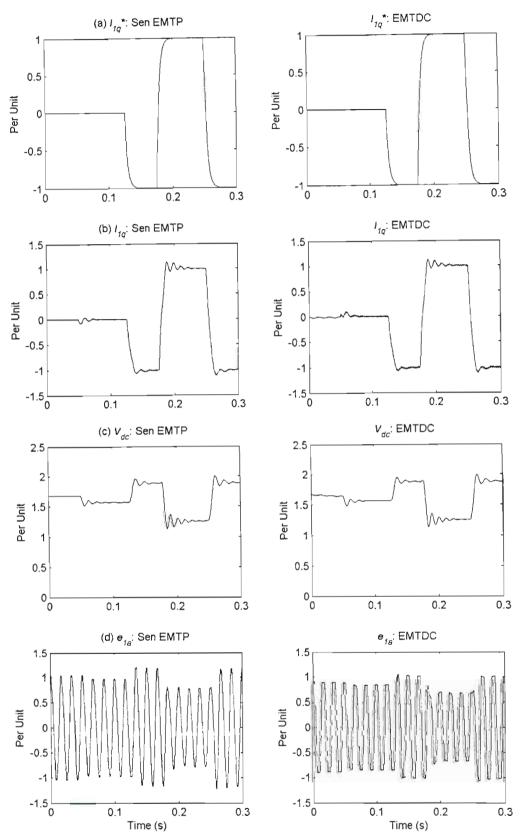

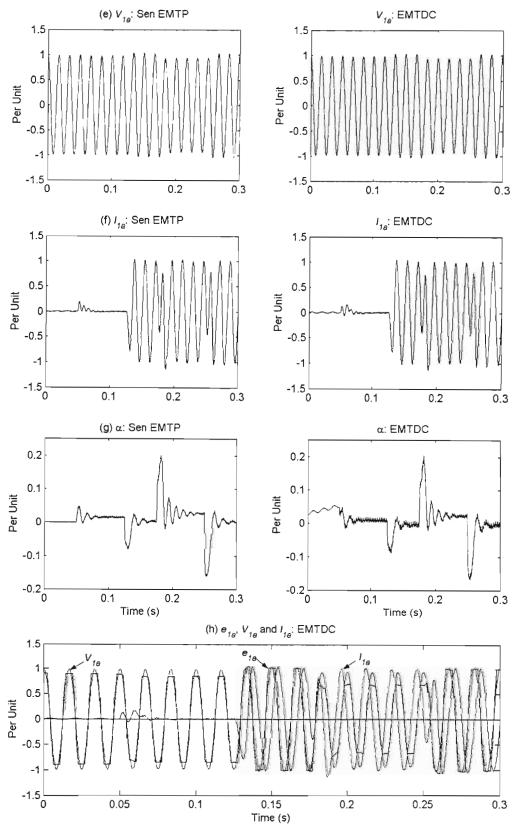

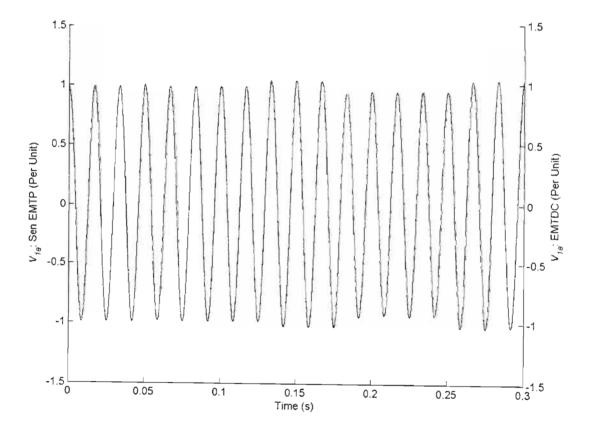

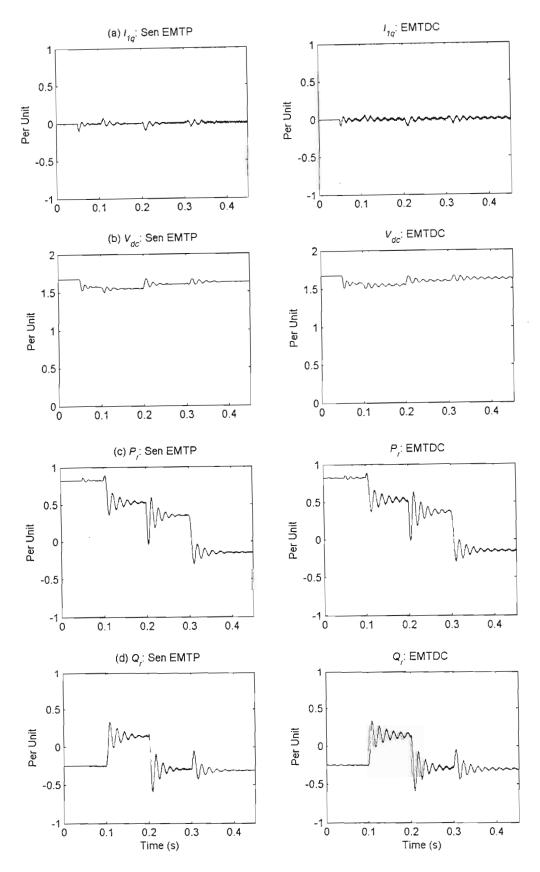

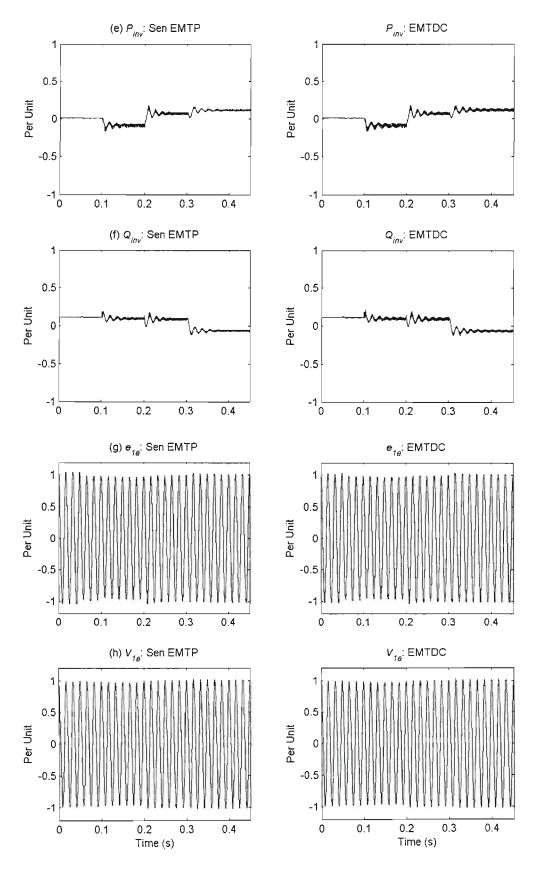

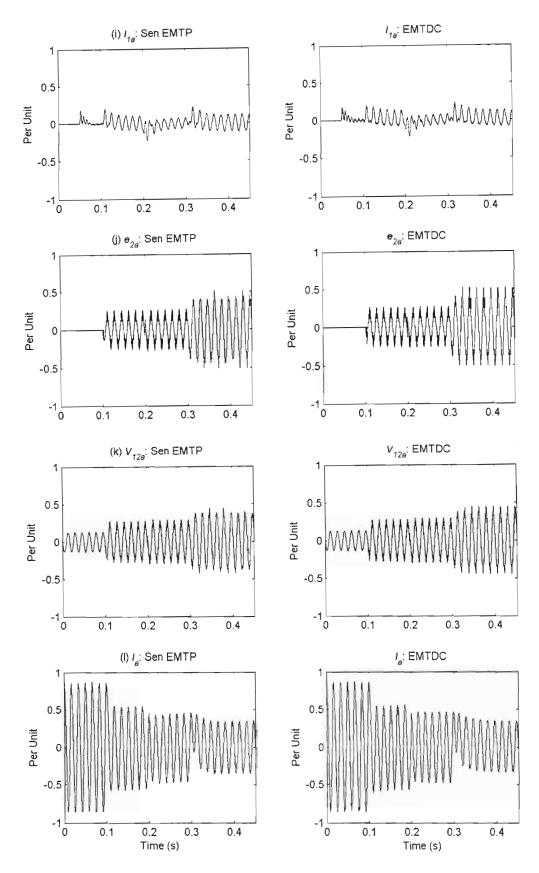

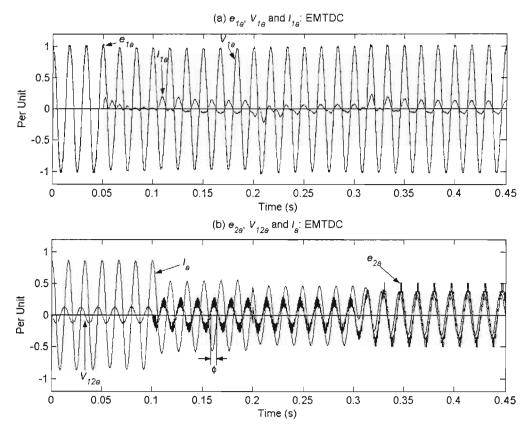

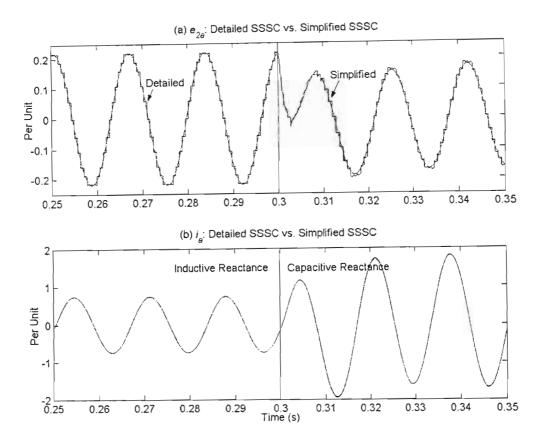

| 5.4     | Continuous-Time Invert-Based FACTS Devices: Benchmark Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 132.                                                      |

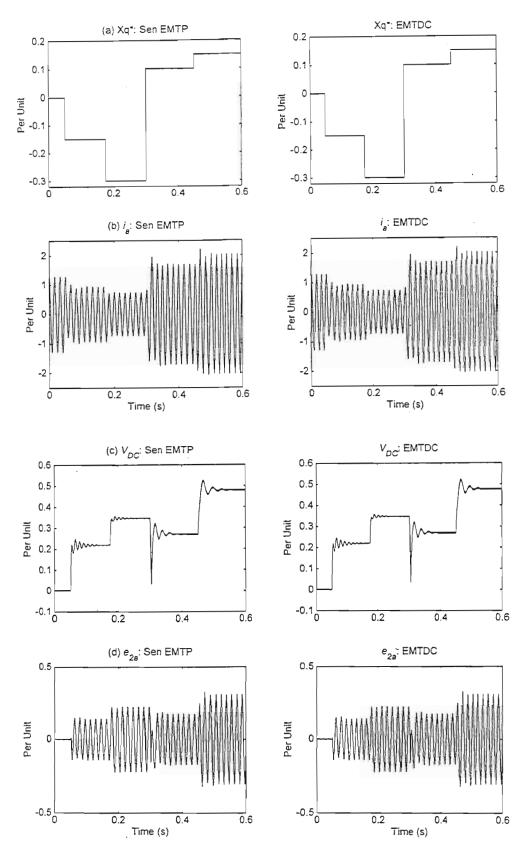

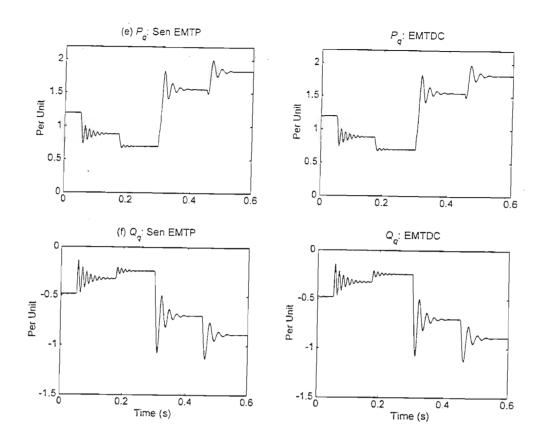

|         | 5.4.1 SSSC <i>132</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                           |

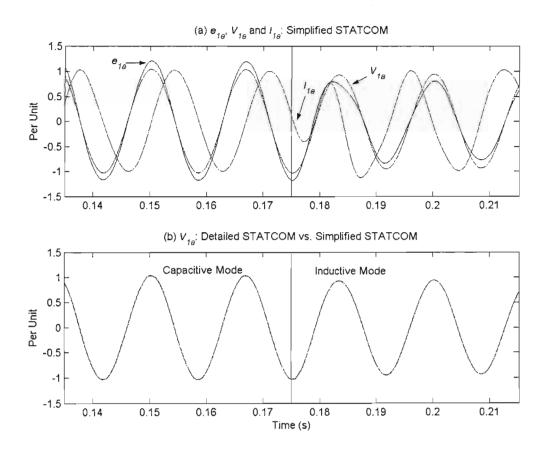

|         | 5.4.2 STATCOM <i>133</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           |

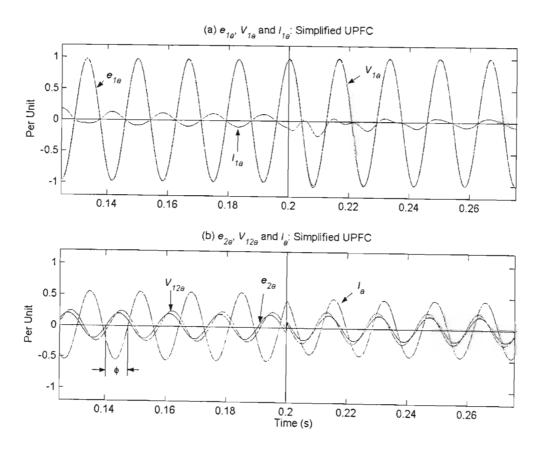

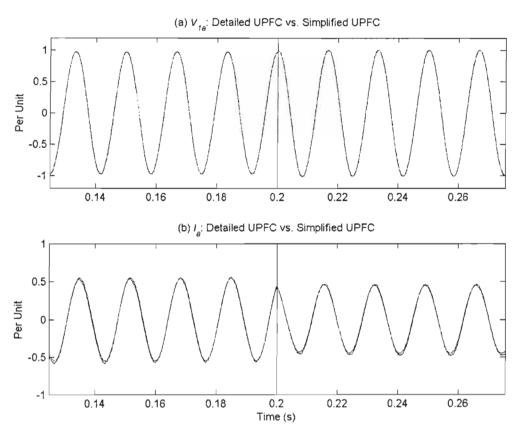

|         | 5.4.3 UPFC 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |

| 5.5     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 136.                                                      |

| CF      | HAPTER SIX: RESONANT CHARACTERISTICS OF ELECTRICAL COMPENSATION PROPERTY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                           |

|         | ELECTRICAL COMPENSATION PE<br>BY THE TWO-LEVEL SSSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ROVIDED                                                   |

| 6.1     | ELECTRICAL COMPENSATION PE<br>BY THE TWO-LEVEL SSSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ROVIDED                                                   |

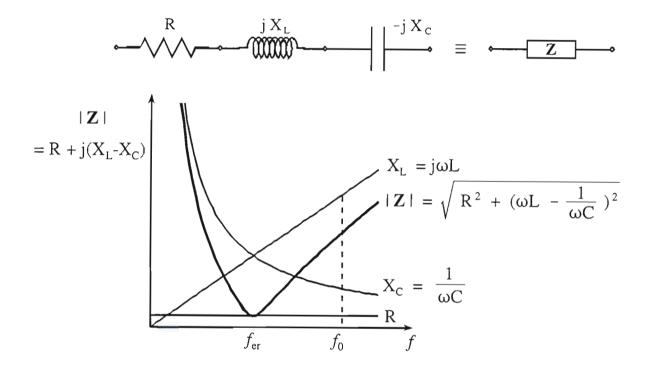

| 6.1     | ELECTRICAL COMPENSATION PE<br>BY THE TWO-LEVEL SSSC<br>Introduction<br>Subsynchronous Resonance (SSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ROVIDED                                                   |

| 6.1     | ELECTRICAL COMPENSATION PE<br>BY THE TWO-LEVEL SSSC  Introduction Subsynchronous Resonance (SSR) 6.2.1 SSSC 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ROVIDED                                                   |

| 6.1     | ELECTRICAL COMPENSATION PER BY THE TWO-LEVEL SSSC  Introduction  Subsynchronous Resonance (SSR)  6.2.1 SSSC 139  6.2.2 Mechanisms Of SSR 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ROVIDED                                                   |

| 6.1     | ELECTRICAL COMPENSATION PER BY THE TWO-LEVEL SSSC  Introduction Subsynchronous Resonance (SSR) 6.2.1 SSSC 139 6.2.2 Mechanisms Of SSR 139 6.2.3 Literature Review 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 138.<br>139.                                              |

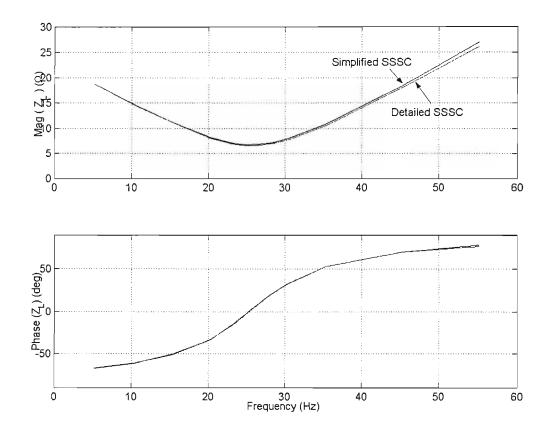

| 6.1     | ELECTRICAL COMPENSATION PER BY THE TWO-LEVEL SSSC  Introduction  Subsynchronous Resonance (SSR)  6.2.1 SSSC 139  6.2.2 Mechanisms Of SSR 139  6.2.3 Literature Review 141  The Impedance Versus Frequency Characteristics Of The SSSC In Technology (SSC) In Technology (S | 138.<br>139.<br>The                                       |

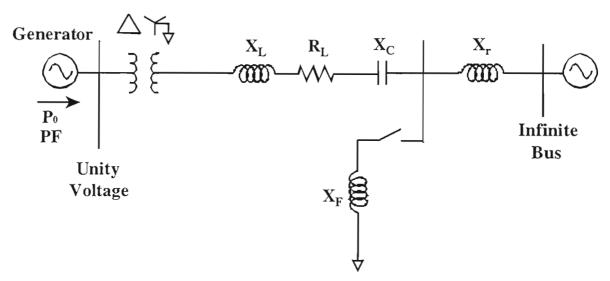

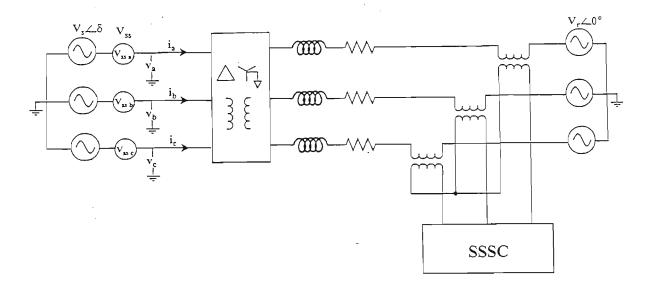

| 6.1     | ELECTRICAL COMPENSATION PER BY THE TWO-LEVEL SSSC  Introduction Subsynchronous Resonance (SSR) 6.2.1 SSSC 139 6.2.2 Mechanisms Of SSR 139 6.2.3 Literature Review 141 The Impedance Versus Frequency Characteristics Of The SSSC In Transmission Line Of The IEEE Benchmark Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 138.<br>139.                                              |

| 6.1     | ELECTRICAL COMPENSATION PER BY THE TWO-LEVEL SSSC  Introduction Subsynchronous Resonance (SSR) 6.2.1 SSSC 139 6.2.2 Mechanisms Of SSR 139 6.2.3 Literature Review 141  The Impedance Versus Frequency Characteristics Of The SSSC In Transmission Line Of The IEEE Benchmark Model 6.3.1 Introduction 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 138.<br>139.<br>The                                       |

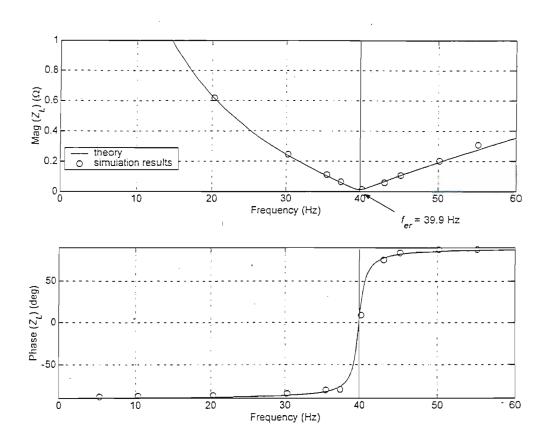

| 6.1     | ELECTRICAL COMPENSATION PERBY THE TWO-LEVEL SSSC  Introduction  Subsynchronous Resonance (SSR)  6.2.1 SSSC 139  6.2.2 Mechanisms Of SSR 139  6.2.3 Literature Review 141  The Impedance Versus Frequency Characteristics Of The SSSC In Transmission Line Of The IEEE Benchmark Model  6.3.1 Introduction 143  6.3.2 Simulated Frequency Response Test Methodology 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 138.<br>139.<br>The                                       |

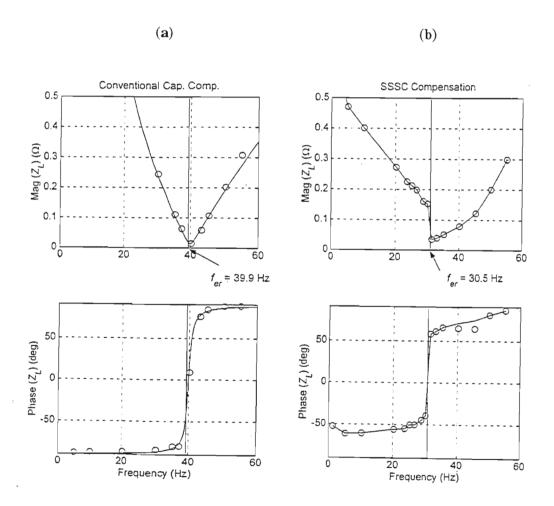

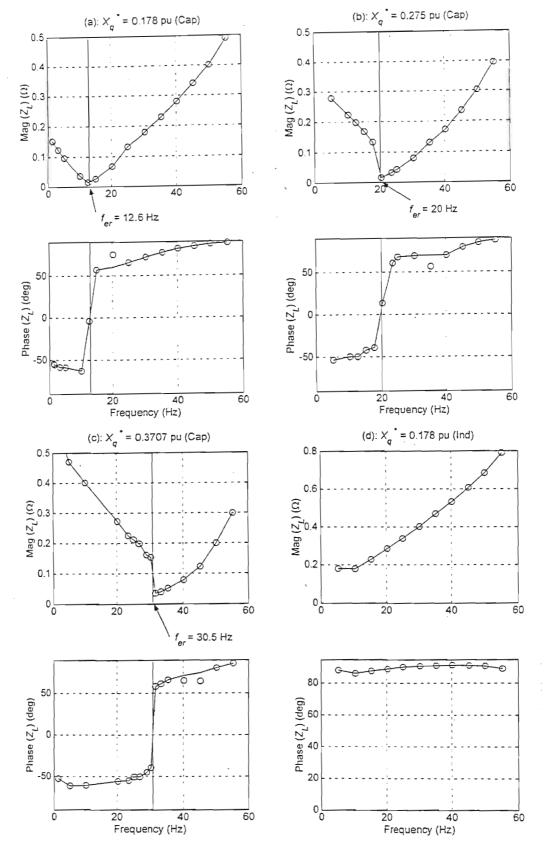

| 6.1     | ELECTRICAL COMPENSATION PERBY THE TWO-LEVEL SSSC  Introduction  Subsynchronous Resonance (SSR)  6.2.1 SSSC 139  6.2.2 Mechanisms Of SSR 139  6.2.3 Literature Review 141  The Impedance Versus Frequency Characteristics Of The SSSC In Transmission Line Of The IEEE Benchmark Model  6.3.1 Introduction 143  6.3.2 Simulated Frequency Response Test Methodology 144  6.3.3 Conventional Capacitor Compensation Versus SSSC Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 138. 139. The 143.                                        |

| 6.1     | ELECTRICAL COMPENSATION PERBY THE TWO-LEVEL SSSC  Introduction  Subsynchronous Resonance (SSR)  6.2.1 SSSC 139  6.2.2 Mechanisms Of SSR 139  6.2.3 Literature Review 141  The Impedance Versus Frequency Characteristics Of The SSSC In Transmission Line Of The IEEE Benchmark Model  6.3.1 Introduction 143  6.3.2 Simulated Frequency Response Test Methodology 144  6.3.3 Conventional Capacitor Compensation Versus SSSC Compensation SSSC Compensation For Different Values Of Compensating Response Test Methodology Response Test Methodology 144  6.3.4 SSSC Compensation For Different Values Of Compensating Response Test Methodology Response Test Methodology 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 138. 139. The 143.                                        |

| 6.1 6.2 | ELECTRICAL COMPENSATION PERBY THE TWO-LEVEL SSSC  Introduction  Subsynchronous Resonance (SSR)  6.2.1 SSSC 139  6.2.2 Mechanisms Of SSR 139  6.2.3 Literature Review 141  The Impedance Versus Frequency Characteristics Of The SSSC In Transmission Line Of The IEEE Benchmark Model  6.3.1 Introduction 143  6.3.2 Simulated Frequency Response Test Methodology 144  6.3.3 Conventional Capacitor Compensation Versus SSSC Compensation SSSC Compensation For Different Values Of Compensating Results  148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ROVIDED  138. 139.  The  143.  tion $145$ actance $X_q^*$ |

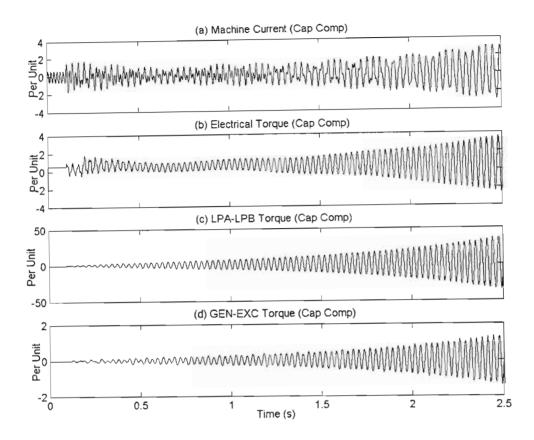

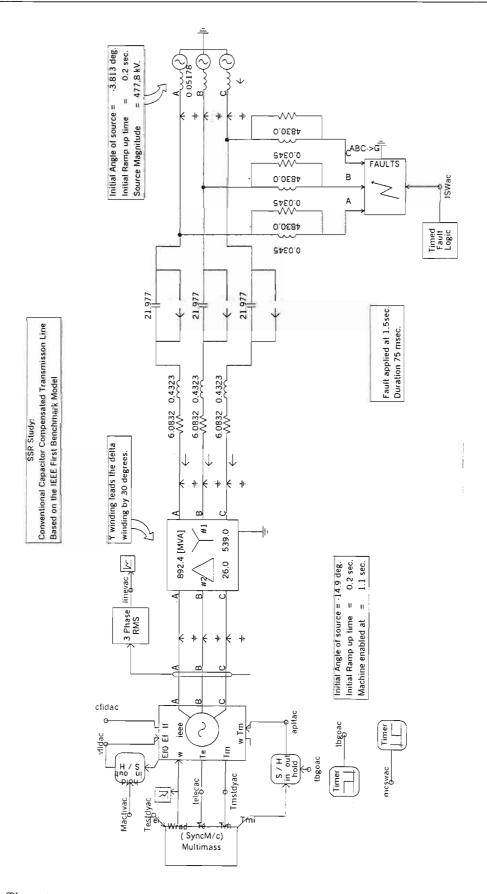

| 6.1 6.2 | ELECTRICAL COMPENSATION PERBY THE TWO-LEVEL SSSC  Introduction  Subsynchronous Resonance (SSR)  6.2.1 SSSC 139  6.2.2 Mechanisms Of SSR 139  6.2.3 Literature Review 141  The Impedance Versus Frequency Characteristics Of The SSSC In Transmission Line Of The IEEE Benchmark Model  6.3.1 Introduction 143  6.3.2 Simulated Frequency Response Test Methodology 144  6.3.3 Conventional Capacitor Compensation Versus SSSC Compensation Compensation For Different Values Of Compensating Results  148  The IEEE First Benchmark Model Compensated: Conventional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 138. 139.  The 143.  tion 145 actance $X_q^*$ al Capacito |

| 6.1 6.2 | ELECTRICAL COMPENSATION PERBY THE TWO-LEVEL SSSC  Introduction  Subsynchronous Resonance (SSR)  6.2.1 SSSC 139  6.2.2 Mechanisms Of SSR 139  6.2.3 Literature Review 141  The Impedance Versus Frequency Characteristics Of The SSSC In Transmission Line Of The IEEE Benchmark Model  6.3.1 Introduction 143  6.3.2 Simulated Frequency Response Test Methodology 144  6.3.3 Conventional Capacitor Compensation Versus SSSC Compensation SSSC Compensation For Different Values Of Compensating Results  148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ROVIDED  138. 139.  The  143.  tion $145$ actance $X_q^*$ |

|     | 8.4.2 Performance of Multi-Modal Damping Control 198                                                          |       |

|-----|---------------------------------------------------------------------------------------------------------------|-------|

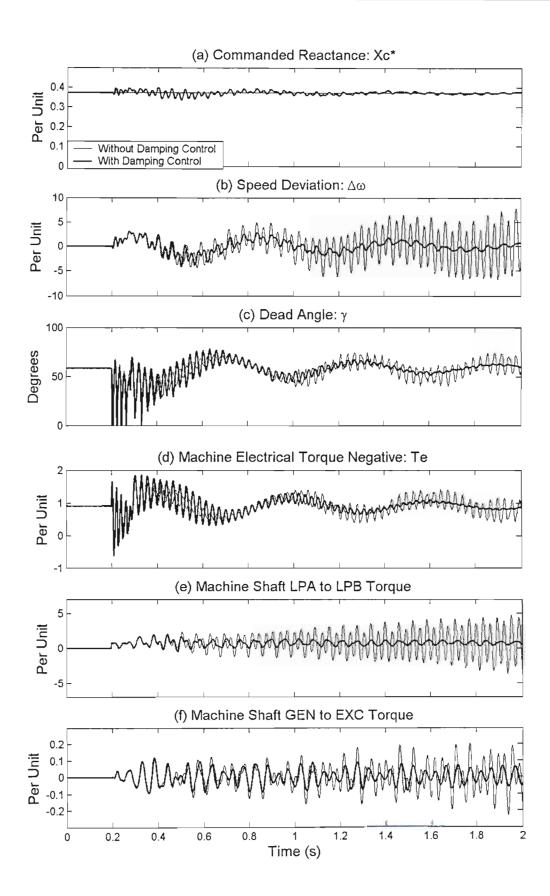

|     | Case 1 – Multi-Modal Damping Controller Applied To Case 1 199                                                 |       |

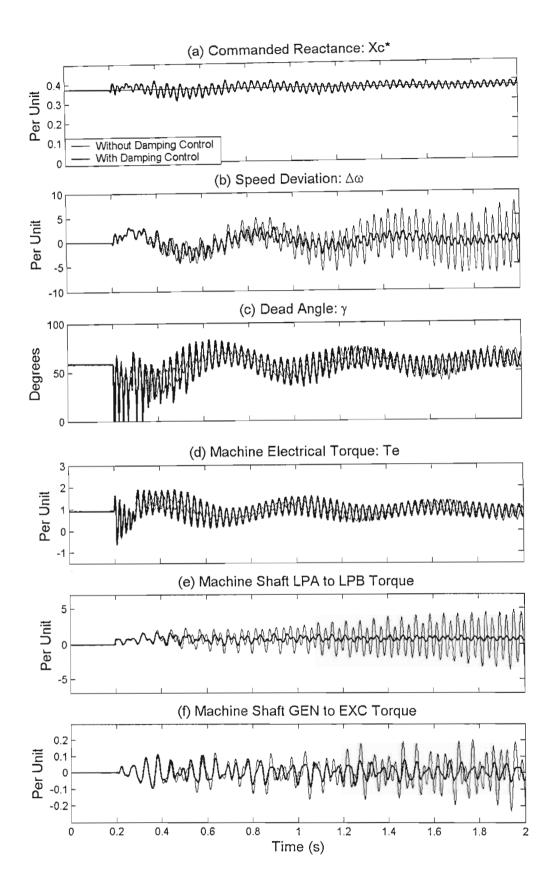

|     | Case 2 – Multi-Modal Damping Controller Applied To Case 2 202                                                 |       |

|     | Case 3 – Multi-Modal Damping Controller Applied To Case 3 204                                                 |       |

| 8.5 | Performance of Multi-Modal Damping Controller at Other Values of                                              |       |

|     | Compensation                                                                                                  | 207.  |

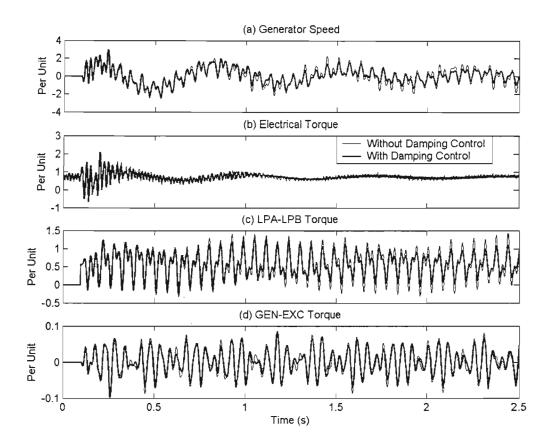

|     | 8.5.1 Cross-Case Damping Study Using the Multi-Modal Supplementary Control                                    | oller |

|     | Designed For Case 1 Dual-Compensated System 208                                                               |       |

|     | - Multi-Modal Damping Controller Applied To The Case 2 Dual-Compensated                                       |       |

|     | System 208                                                                                                    |       |

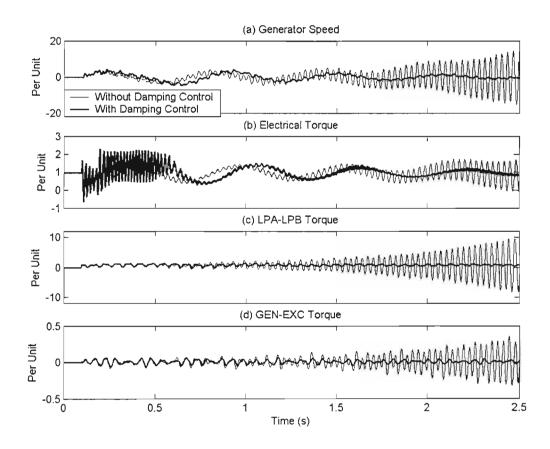

|     | <ul> <li>Multi-Modal Damping Controller Applied To The Case 3 Dual-Compensated</li> <li>System 210</li> </ul> |       |

|     | 8.5.2 Cross-Case Damping Study Using the Multi-Modal Supplementary Contr                                      | oller |

|     | Designed For Case 2 Dual-Compensated System 211                                                               |       |

|     | <ul> <li>Multi-Modal Damping Controller Applied To The Case 1 Dual-Compensated</li> <li>System 211</li> </ul> |       |

|     | <ul> <li>Multi-Modal Damping Controller Applied To The Case 3 Dual-Compensated</li> <li>System 212</li> </ul> |       |

|     | 8.5.3 Cross-Case Damping Study Using the Multi-Modal Supplementary Control                                    | oller |

|     | Designed For Case 3 Dual-Compensated System 214                                                               | 01101 |

|     | - Multi-Modal Damping Controller Applied To The Case 1 Dual-Compensated                                       |       |

|     | System 214                                                                                                    |       |

|     | - Multi-Modal Damping Controller Applied To The Case 2 Dual-Compensated                                       |       |

|     | System 215                                                                                                    |       |

| 8.6 | Practical Considerations                                                                                      | 217.  |

| 8.7 | Conclusion                                                                                                    | 217.  |

|     |                                                                                                               |       |

|     |                                                                                                               |       |

| CH  | IAPTER NINE: CONCLUSION                                                                                       |       |

|     |                                                                                                               |       |

| 9.1 | Introduction                                                                                                  | 219.  |

| 9.2 | Three-Level Multi-Pulse Inverter Model                                                                        | 219.  |

| 9.3 | Detailed Models of Inverter-Based FACTS Devices                                                               | 220.  |

| 9.4 | Continuous-Time SSSC, STATCOM and UPFC Models                                                                 | 223.  |

| 9.5 | Resonant Characteristics of the Two-Level SSSC                                                                | 223.  |

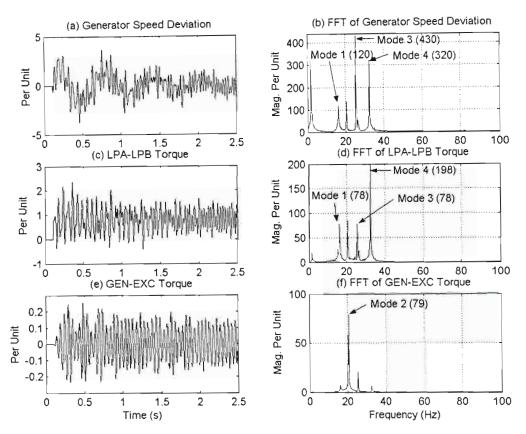

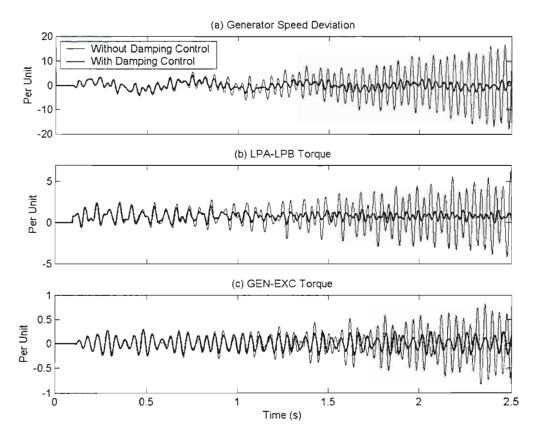

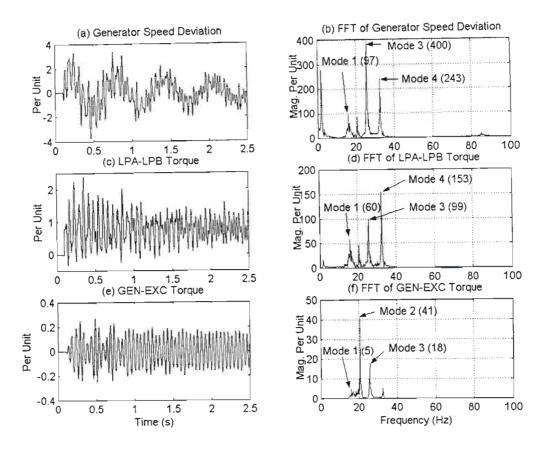

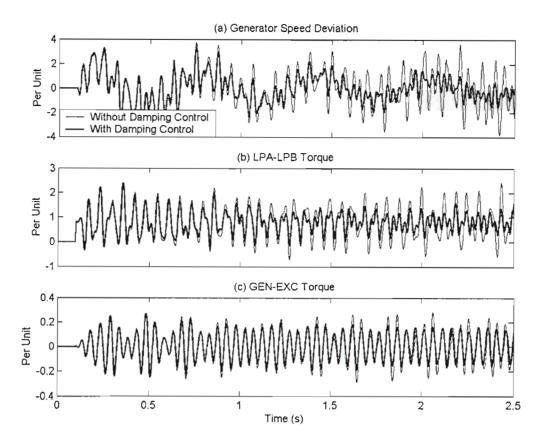

| 9.6 | Supplementary Controller for the Three-Level SSSC                                                             | 225.  |

| 9.7 | Suggestions For Further Work                                                                                  | 227   |

| APPENDIX E: |           | : PARAMETERS OF THE UPFC COMPENSATED TRAN                                         | IS-   |

|-------------|-----------|-----------------------------------------------------------------------------------|-------|

|             |           | MISSION SYSTEM AND ITS PSCAD/EMTDC MODEL                                          | LING  |

| E.1         | Paramet   | ers Of The UPFC Compensated Transmission System In                                |       |

|             | Per-Unit  | Based On [27]                                                                     | E.1.  |

|             | E.1.1 Pe  | r-Unit Base E.1                                                                   |       |

|             | E.1.2 Tra | ansmission Line E.1                                                               |       |

|             | E.1.2 Th  | e UPFC E.3                                                                        |       |

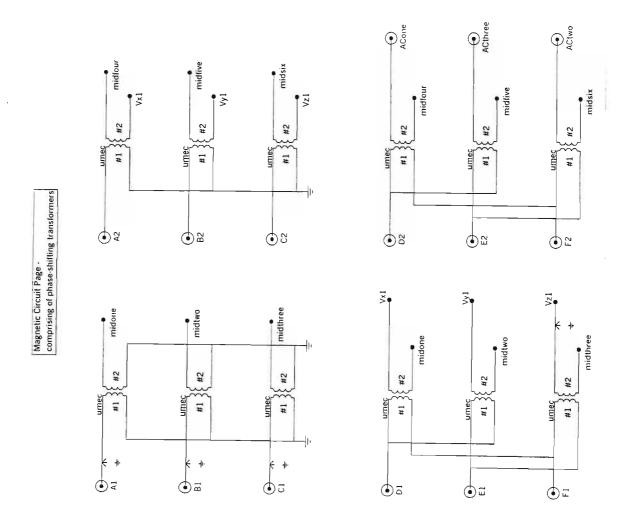

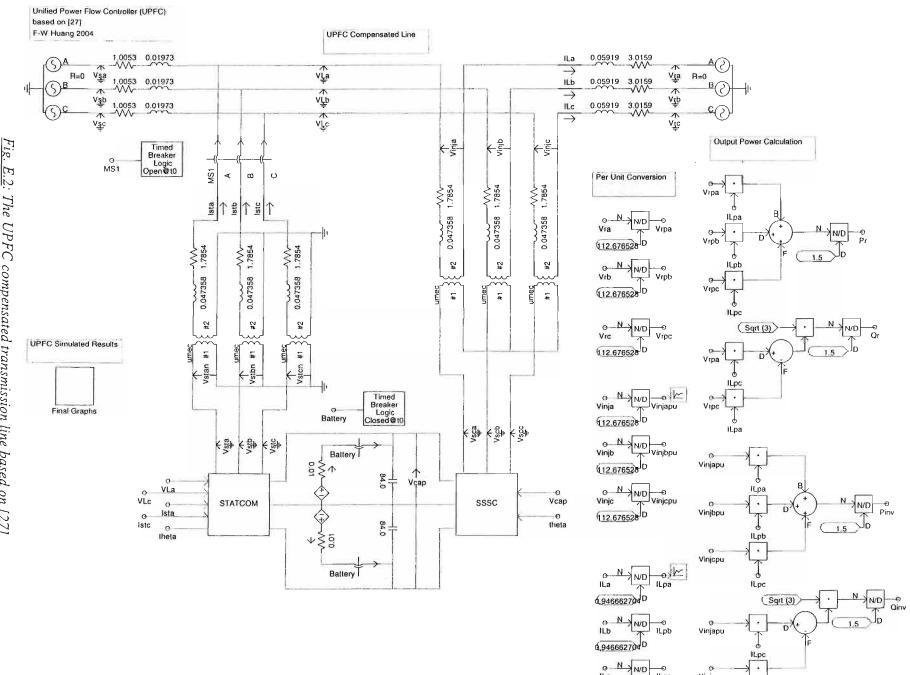

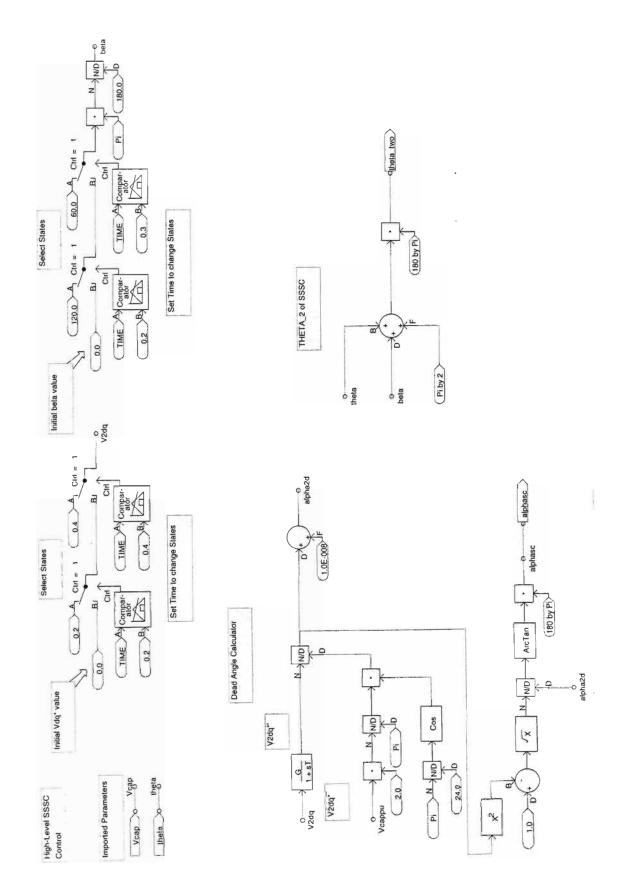

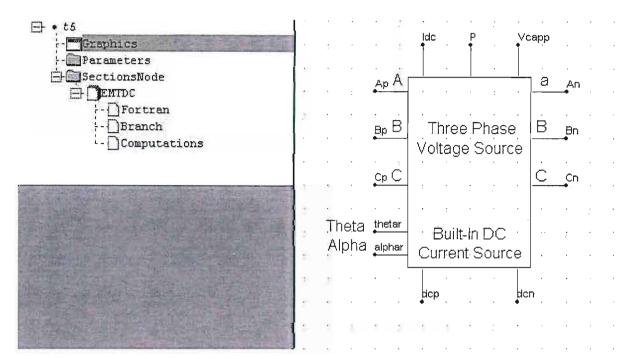

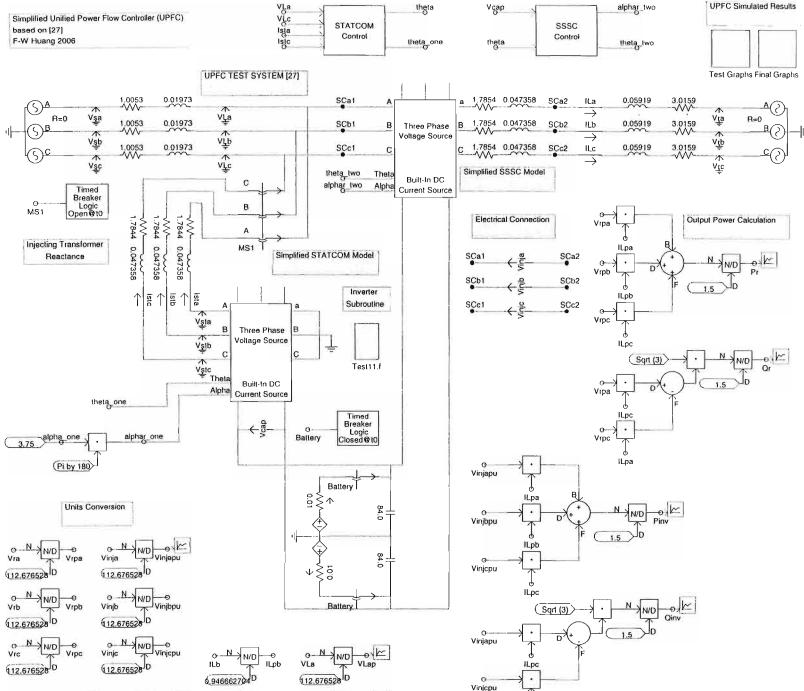

| E.2         | PSCAD/    | EMTDC Representation Of The UPFC Based On [27]                                    | E.3.  |

| APF         | PENDIX F  | CONTINUOUS-TIME INVERTER MODEL IN                                                 |       |

|             |           | PSCAD/EMTDC: DESIGN AND RESONANT                                                  |       |

|             |           | CHARACTERISTICS ANALYSIS OF THE SSSC                                              |       |

|             |           | COMPENSATED TRANSMISSION LINE                                                     |       |

| F.1         | Introduct | ion                                                                               | F.1.  |

| F.2         | Design O  | f The Continuous-Time Inverter Model In PSCAD/EMTDC                               | F.1.  |

| F.3         | The Impe  | dance Versus Frequency Characteristics Of The Simplified SS                       | SC    |

|             | Compens   | ated Transmission Line                                                            | F.7.  |

| A DD        | PENDIX G  | THE DCCAD/EMTDC MODEL C LIGED TO DY A STATE OF                                    |       |

| AI I        | ENDIA G   | THE PSCAD/EMTDC MODELS USED TO EXAMINE T<br>RESONANT CHARACTERISTIC OF THE SERIES | HE    |

|             |           | COMPENSATED TRANSMISSION SYSTEM                                                   |       |

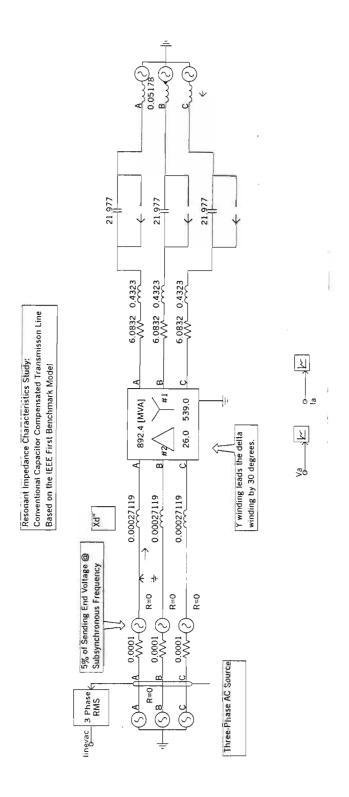

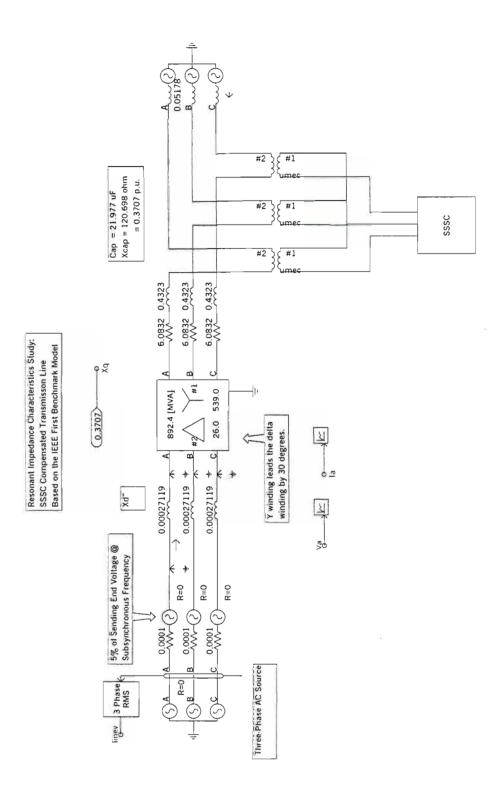

| G.1         | Introduct |                                                                                   |       |

| G.2         |           | edance Versus Frequency Characteristics Of The Series Compe                       | G.1.  |

| <b></b>     |           | nchmark Model                                                                     |       |

| G.3         |           | E First Benchmark Model Compensated With The SSSC And                             | G.1.  |

|             |           | onal Capacitors                                                                   |       |

|             |           |                                                                                   | G.4.  |

| APP         | ENDIX H:  | LEAD COMPENSATOR DESIGN FOR THE                                                   |       |

|             |           | SUPPLEMENTARY DAMPING CONTROLLER                                                  |       |

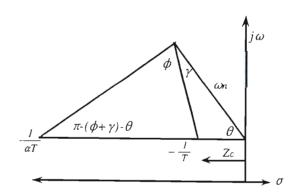

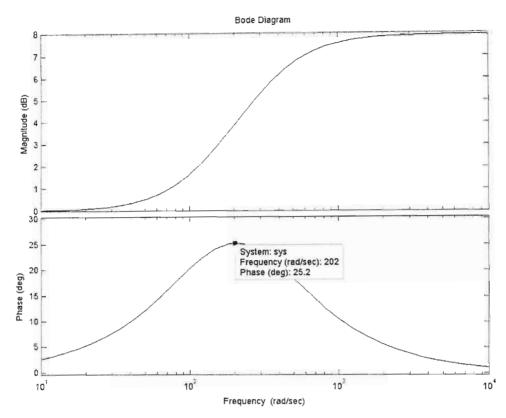

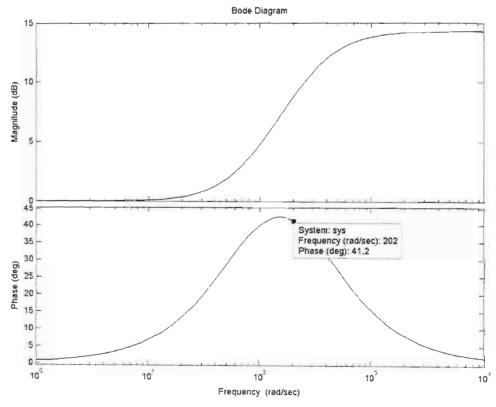

| H.1         | Introduct | ion                                                                               | H.1.  |

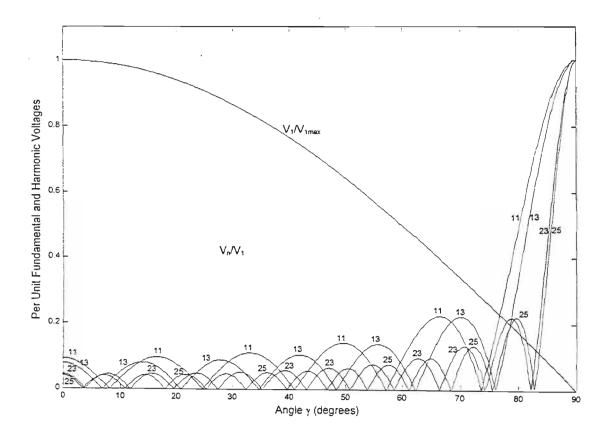

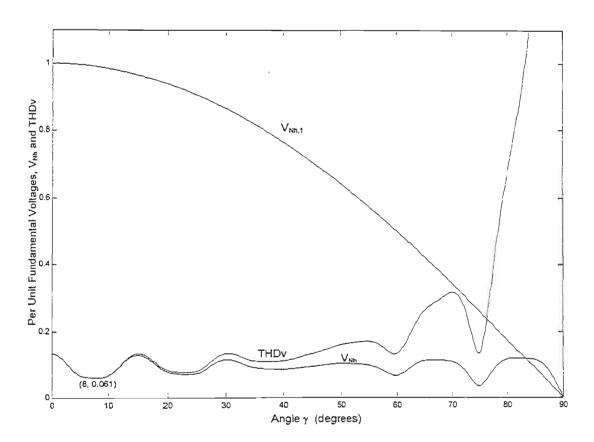

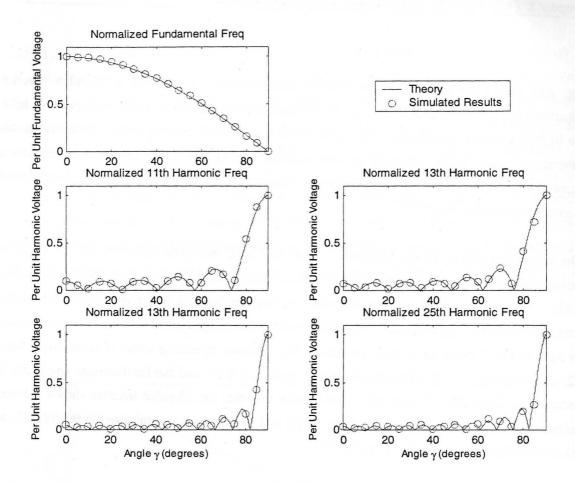

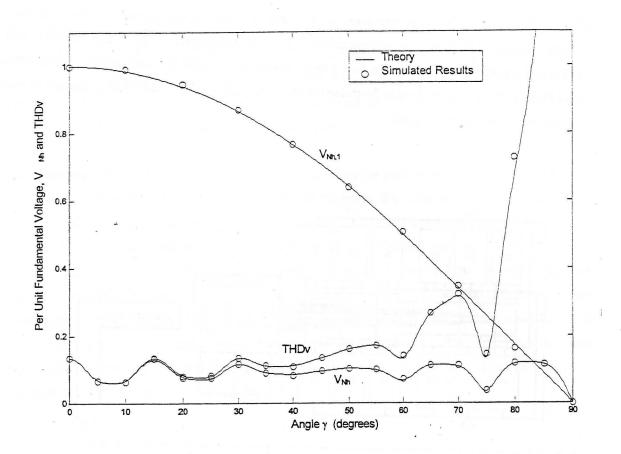

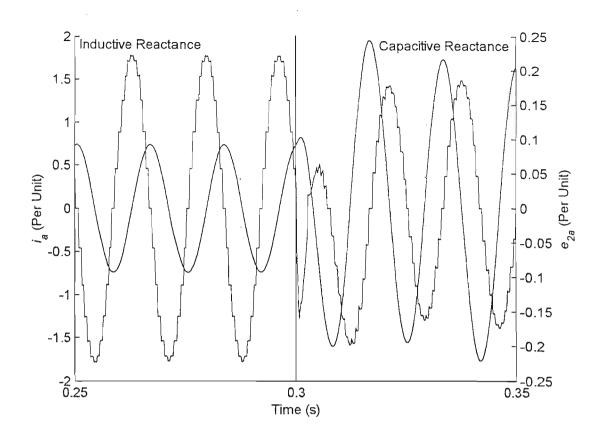

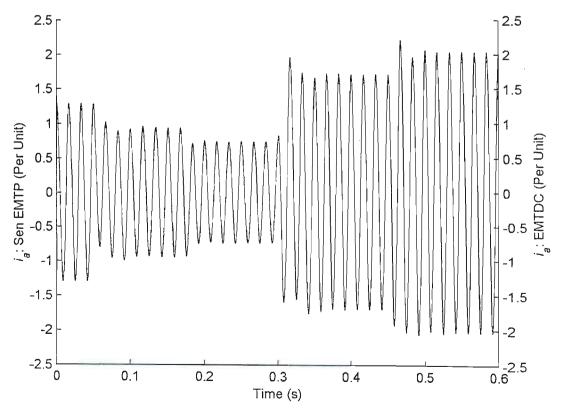

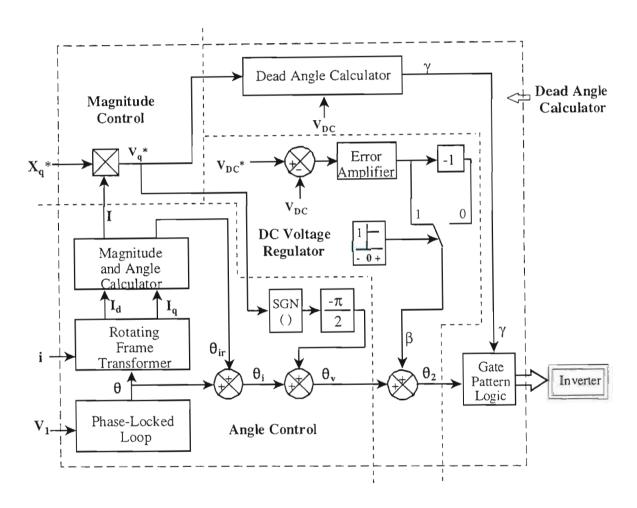

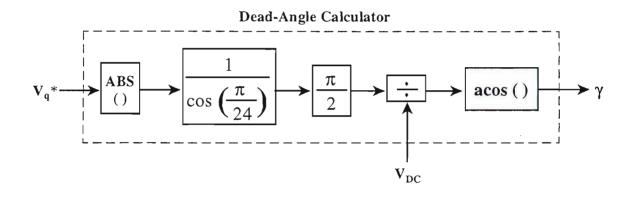

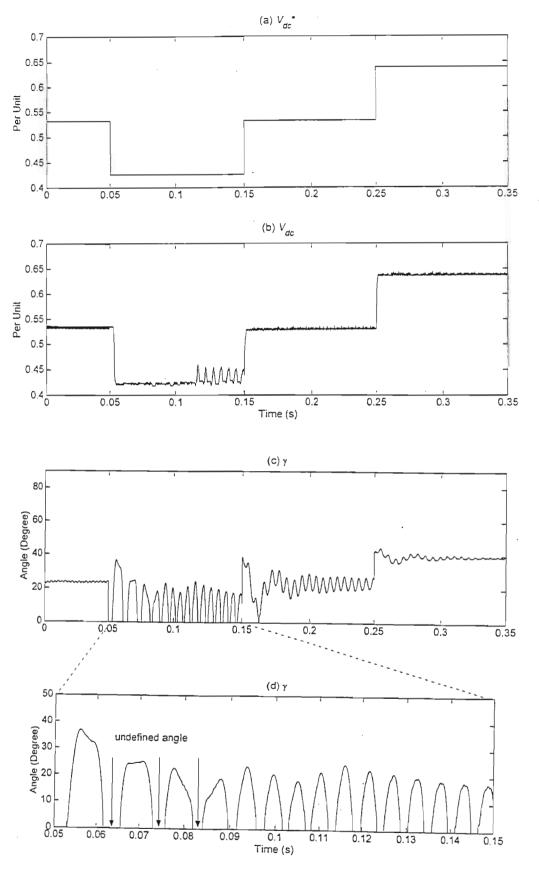

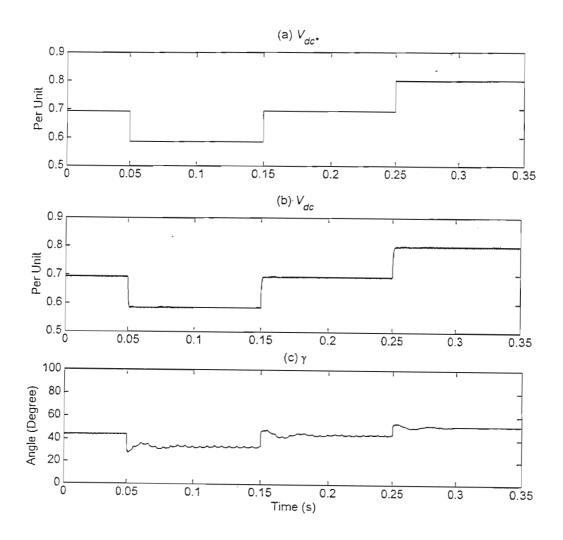

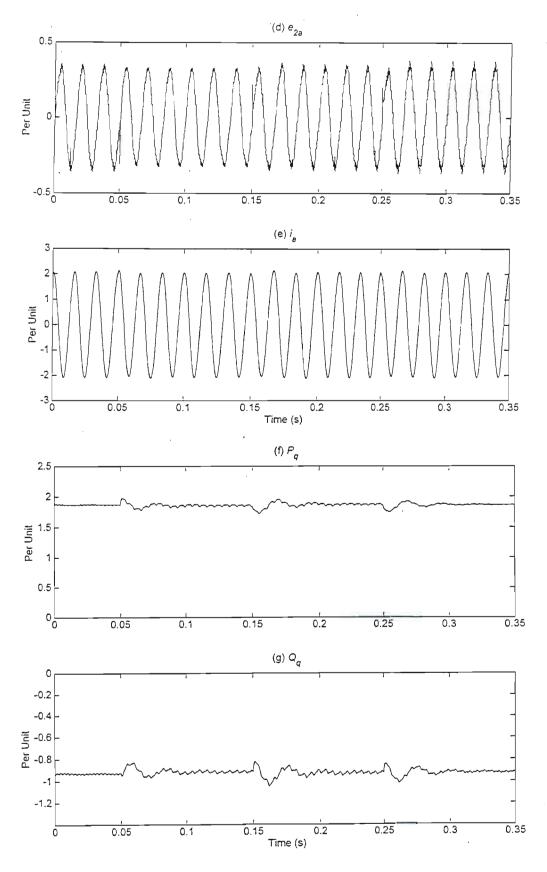

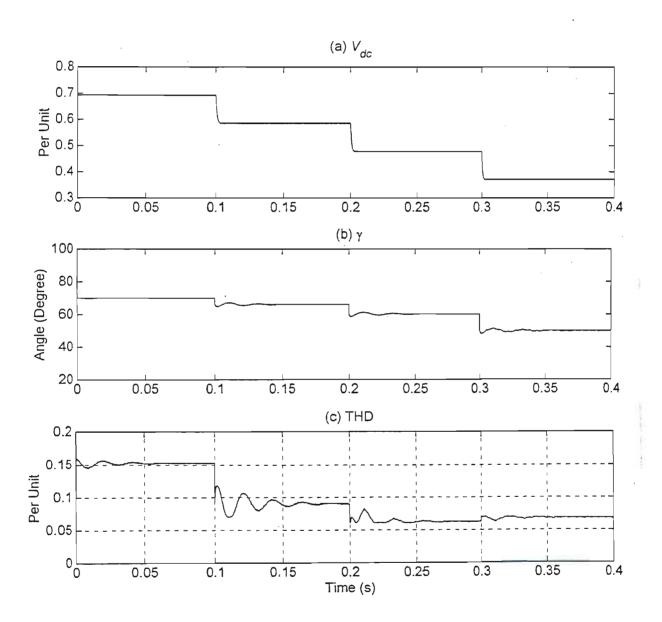

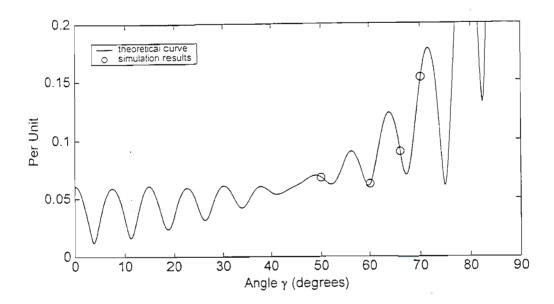

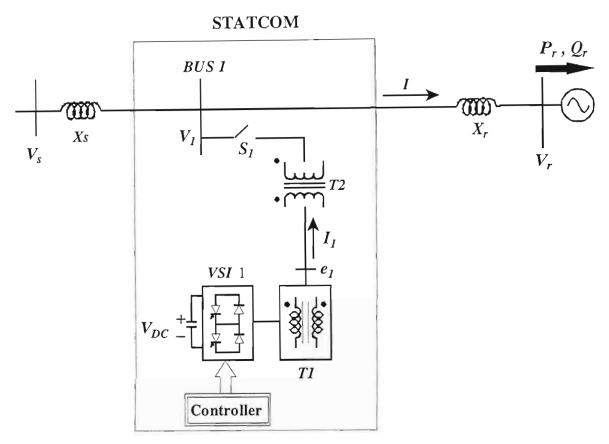

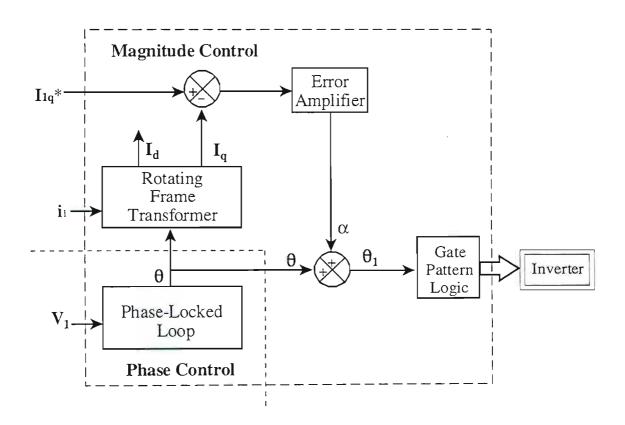

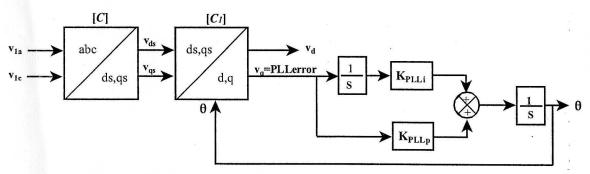

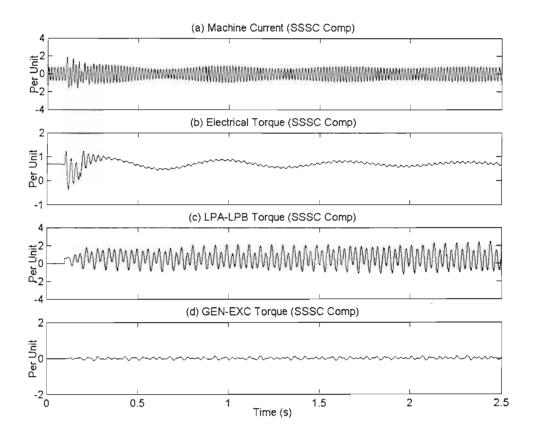

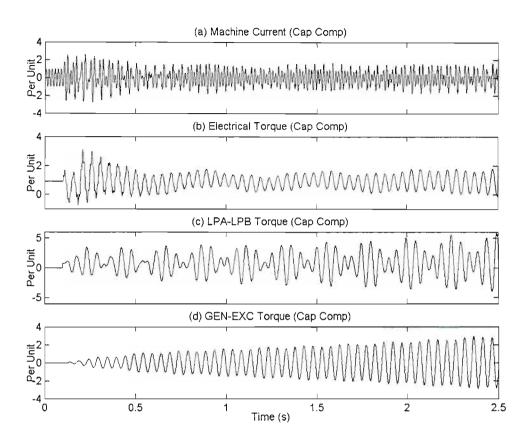

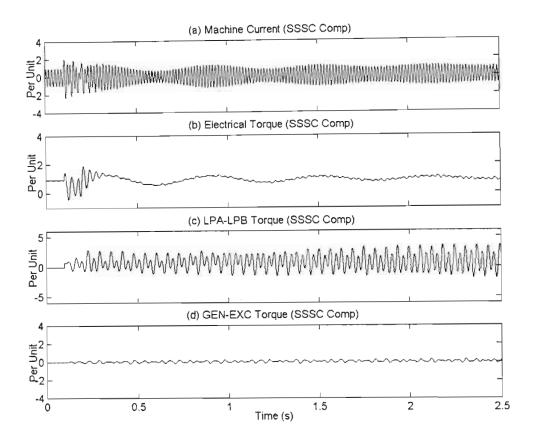

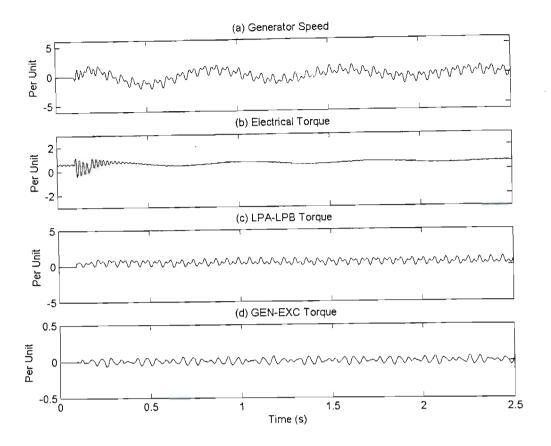

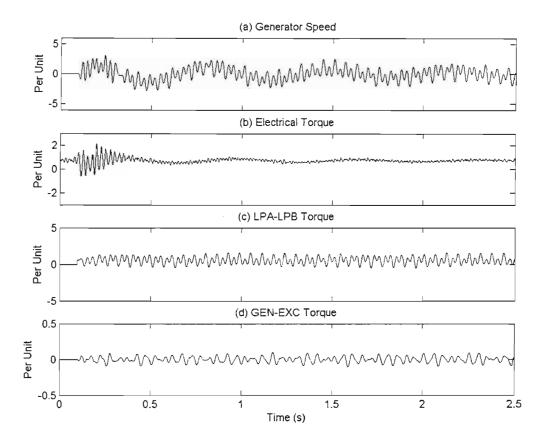

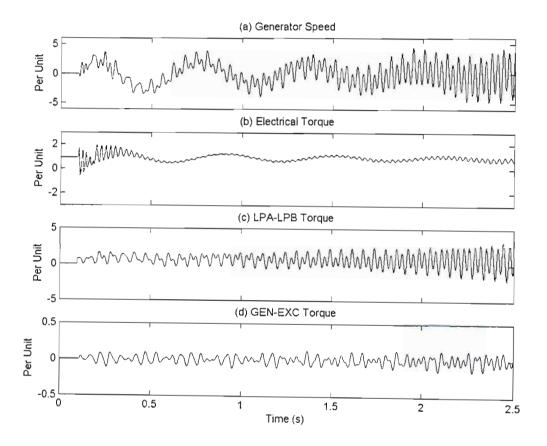

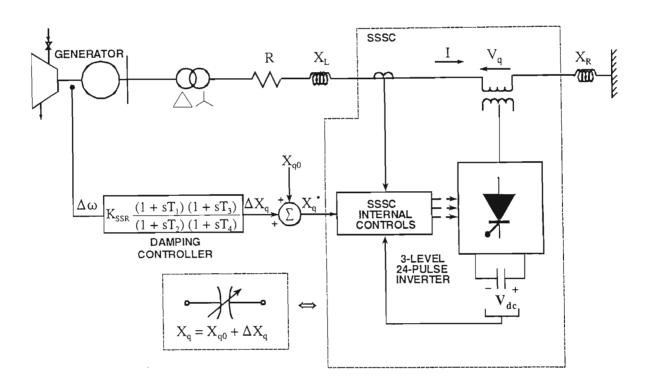

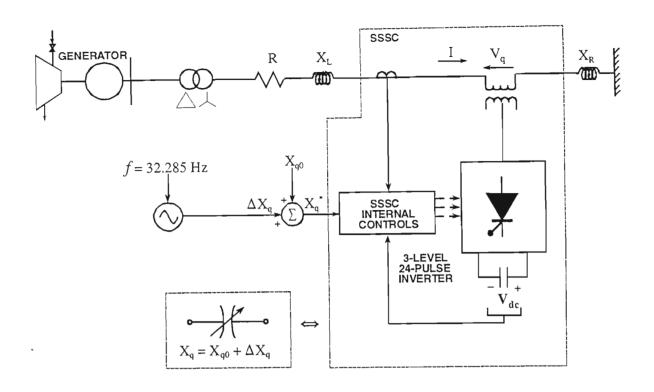

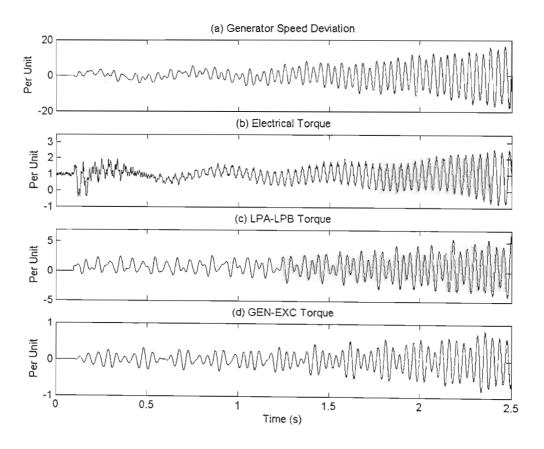

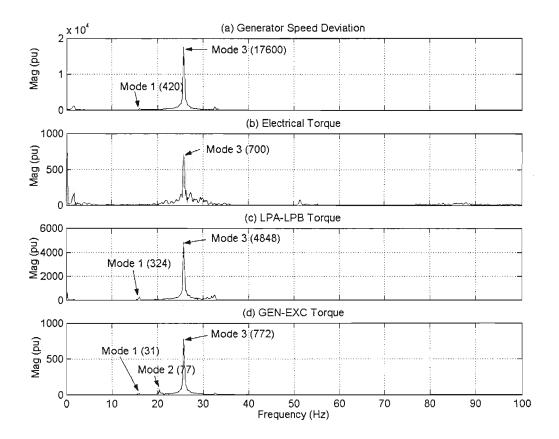

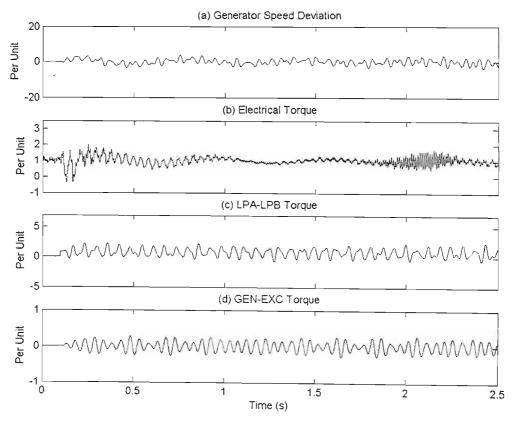

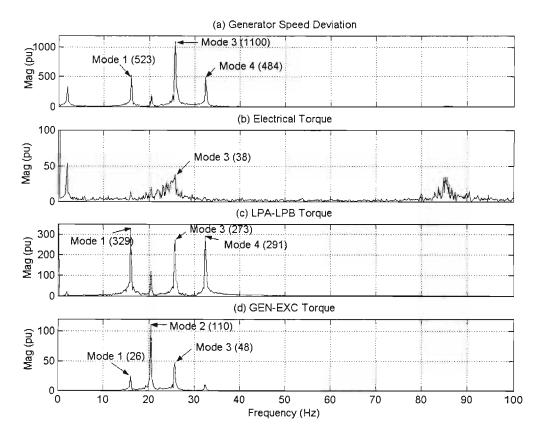

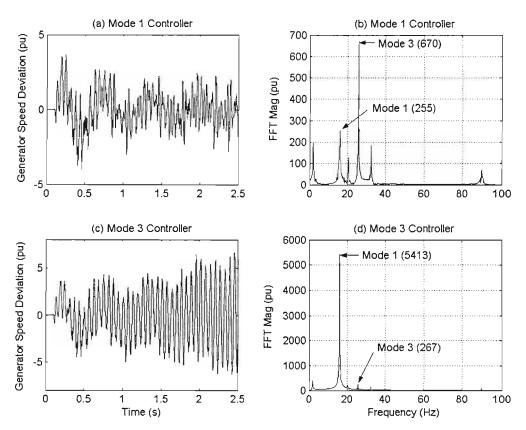

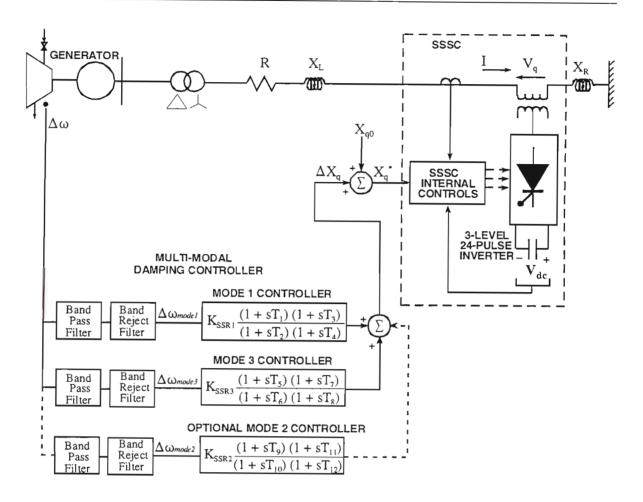

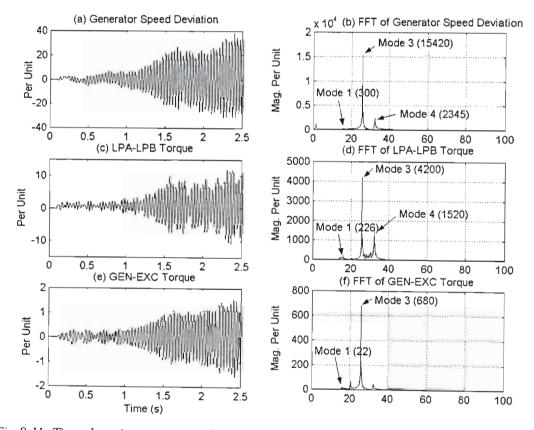

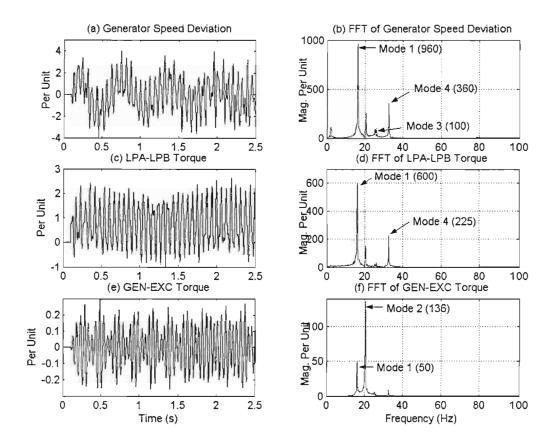

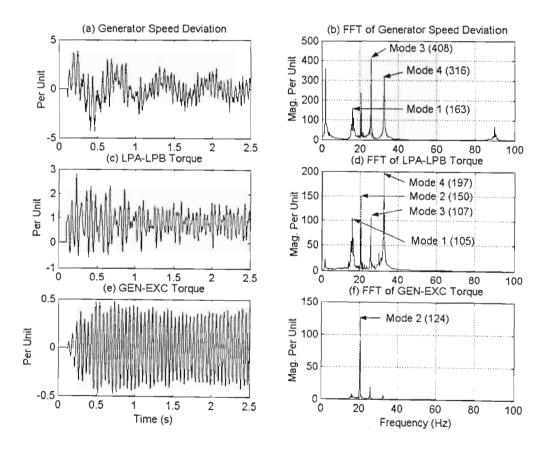

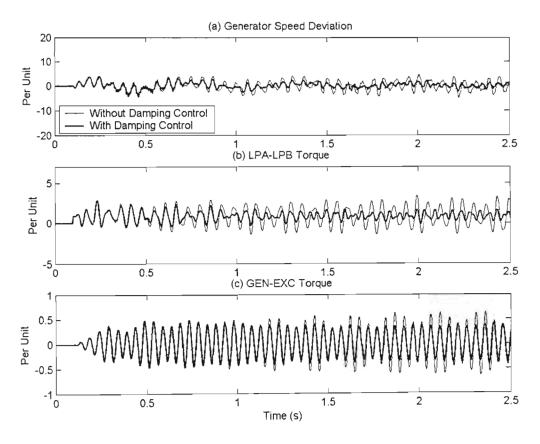

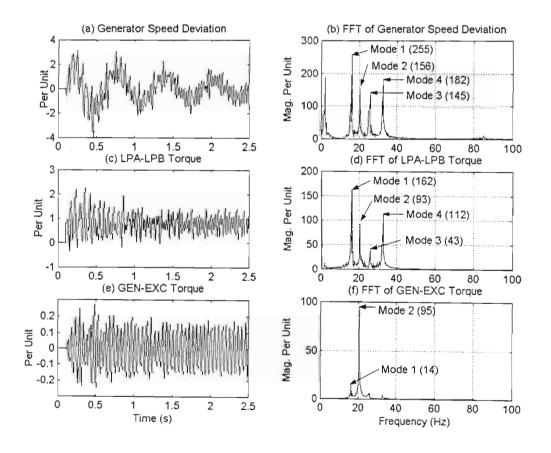

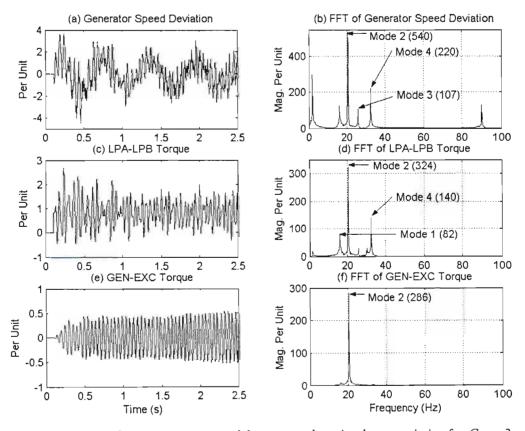

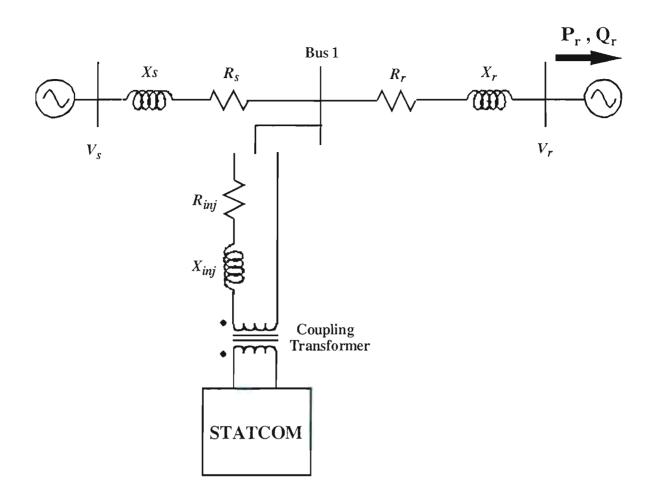

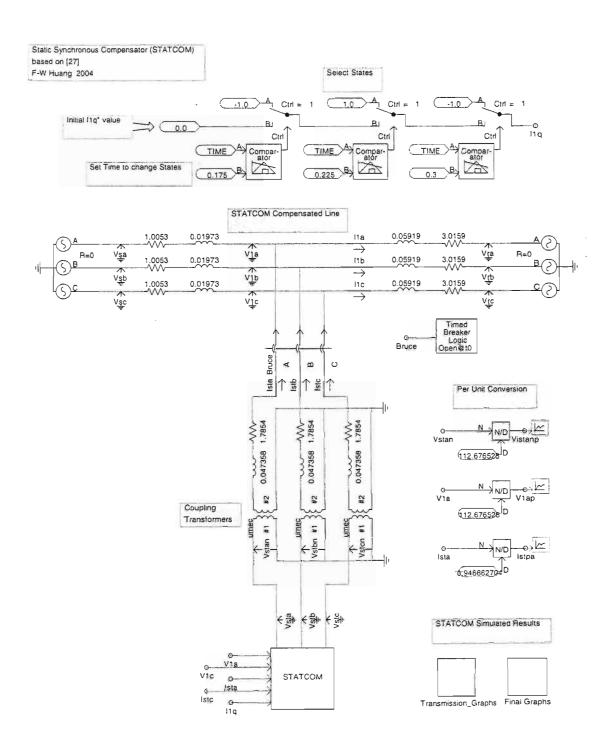

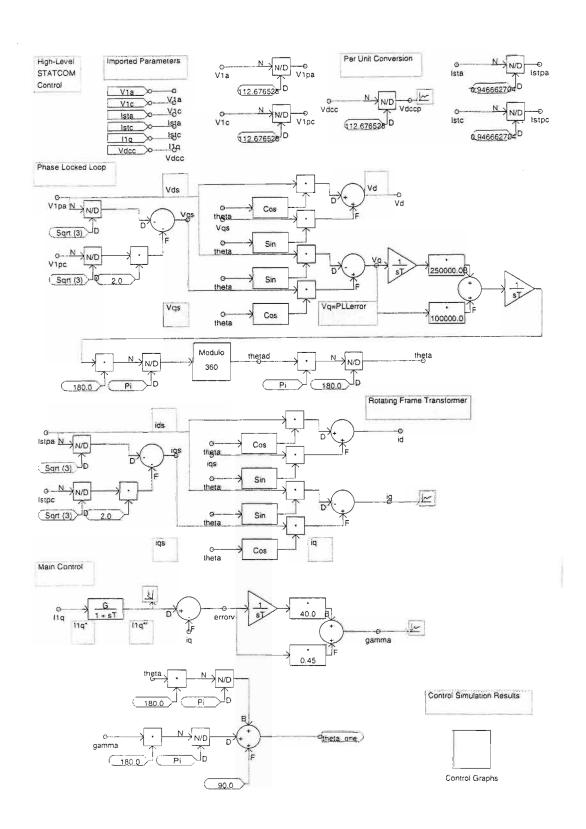

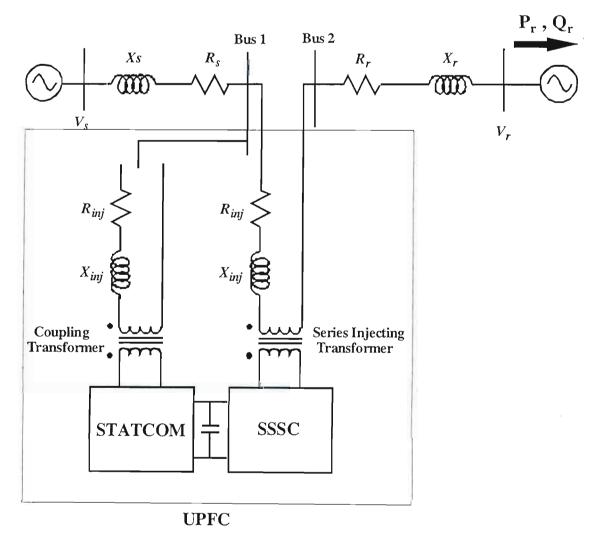

| H.2         | Lead Con  | npensator Design                                                                  | H.1.  |